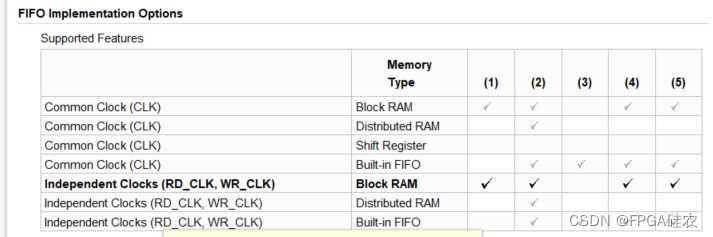

如图所示,在赛灵思官方提供的FIFO IP里,同步FIFO(Common Clock)可以由BRAM、DRAM和移位寄存器构成,或者由内建的FIFO构成,异步FIFO(Independent Clocks)可以由BRAM、DRAM和内建的FIFO构成。

本文主要实现基于移位寄存器的同步FIFO。

实现的思路为:

设置一个计数器,记录目前FIFO内部的数据个数,外部每向FIFO写入一个数据,移位寄存器就进行一次移位,而读出数据的位置则根据FIFO内数据的个数来确定。

以下是实现的代码:

代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/07/22 16:43:50

今天的文章基于移位寄存器的同步FIFO分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/12466.html