1 Verilog描述

module shift_p2s(

input clk,

input [7:0] din,

input load,

output reg q

);

reg [7:0] tmp;

always@(posedge clk)begin

if(load == 1’b1)

tmp <= din;

else begin

q <= tmp[7];

tmp <= {tmp[6:0],1’b0};

end

end

endmodule

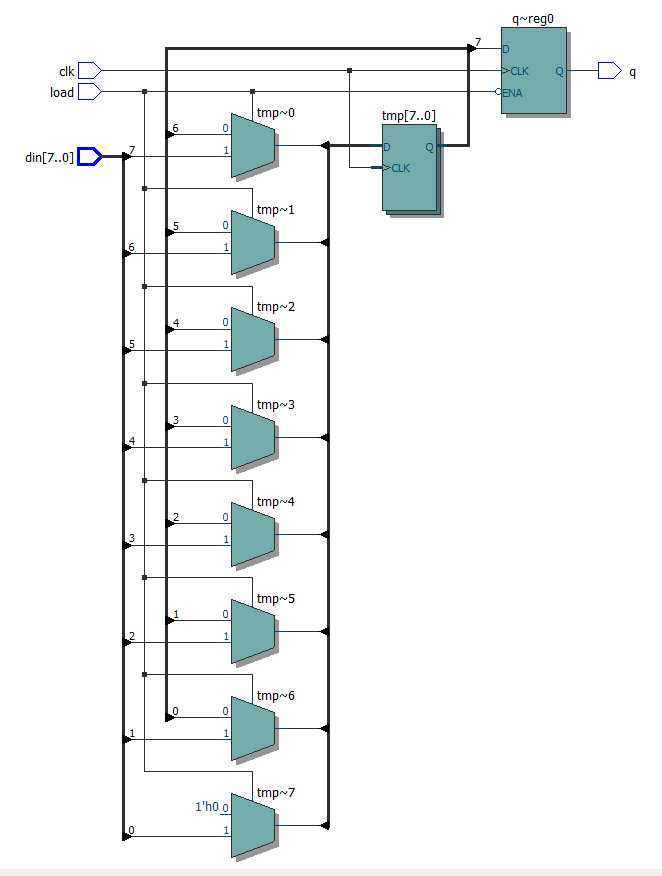

2 RTL视图

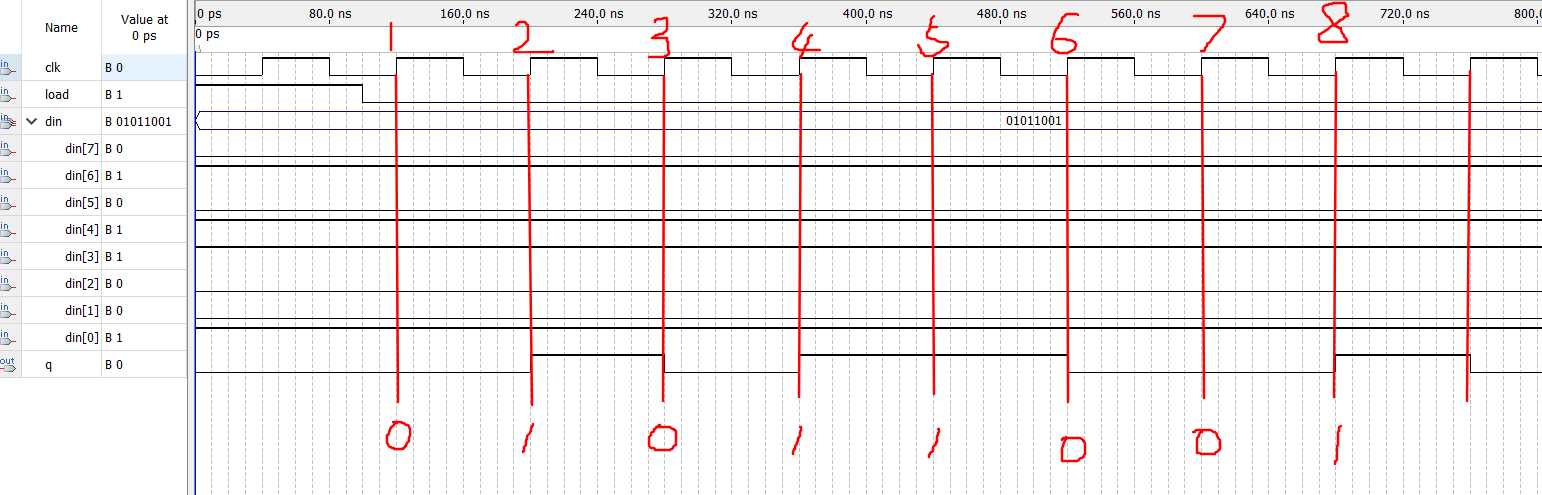

3 功能仿真

今天的文章8位并行输入串行输出的移位寄存器的Verilog描述分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/27294.html