Spartan6驱动ADS1278/4,编译环境为ISE12.2,仿真为isim。

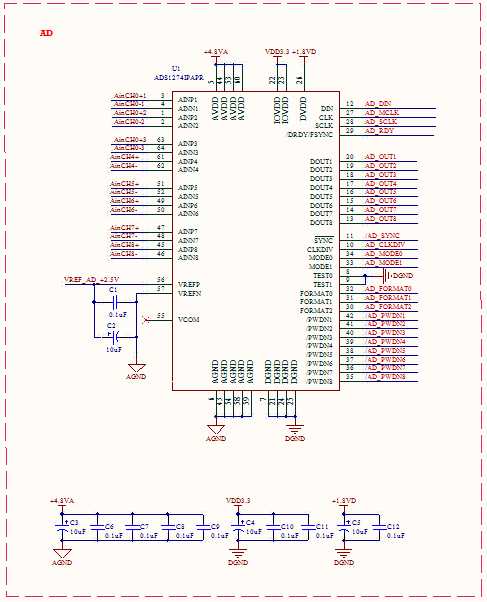

以下为ADS1278/4的引脚图:

个人总结ADS1278/4的特征:

ADS1278/4在芯片设计时,去掉了ADS1278/4的内部寄存器,对于ADS1278/4的工作方式的配置不需要通过通信的方式进行,直接通过IO的电平配置,达到预期的效果。

Ainp1-Ainn1到Ainp8-Ainn8为模拟信号输入端。

CLK: ADS1278/4的主时钟输入端

DIN: 在一般的情况下是没有用的,在多片级联的时候才能用的到。

SCLK: ADS1278/4通信时用到的时钟输入端

DRDY/FSYNC: ADS1278/4通信时数据发送使能端口。

DOUT1-DOUT7: ADS1278/4的数据输出端

SYNC: 从新启动数据转换的端口,当SYNC为低时,AD转换停止。

CLKDIV: ADS1278/4主时钟的选择端

//————————————————————————————–//

MODE0: MODE1:

工作模式选择: 00:High-Speed

01:High-Resolution

10:Low-Power

11:Low-Speed

//————————————————————————————–//

Test0:

Test1: 测试用的引脚

//————————————————————————————–//

PWDN1- PWDN7:关掉相应AD通道的电源,低电平有效,为了降低功耗。

//————————————————————————————–//

Format0:

Format1:

Format2:

通信模式选择:

000:SPI TDM Dynamic

001:SPI TDM Fixed

010:SPI Discrete —

011:Frame-Sync TDM Dynamic

100:Frame-Sync TDM Fixed

101:Frame-Sync Discrete —

110:Modulator — —

//————————————————————————————–//

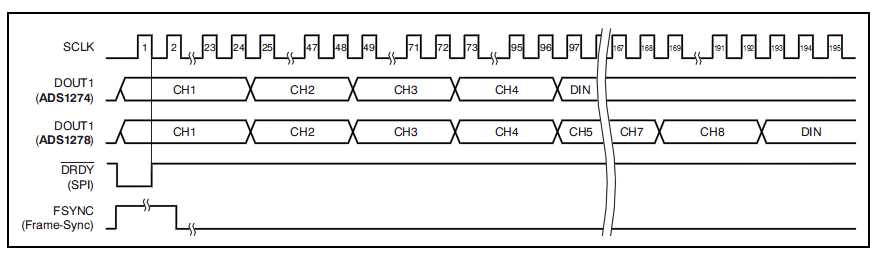

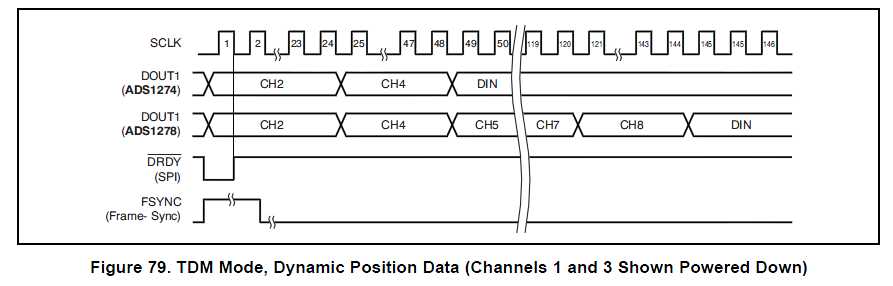

TDM模式: time division multiplexed

Fixed 模式:Fixed-Position Data:所有的信号输出在一根数据线上,即DOUT1.

Dynamic 模式:DynamicPosition Data:不发送相应关掉的电源通道的数据。

如图:通道1与3电源被关断,所以数据不发送。

最终IO的选择:

Format0: 1

Format1: 0

Format2: 1 Frame-Sync 数据发送模式

//————————————————————————————–//

Test0: 0

Test1: 0

//————————————————————————————–//

MODE0: 0

MODE1: 0 高速模式

//————————————————————————————–//

PWDN1: 1 开启1、2、3通道

PWDN2: 1

PWDN3: 1

PWDN4: 0

PWDN5: 0

PWDN6: 0

PWDN7: 0

//————————————————————————————–//

ADS1274与FPGA的通信:

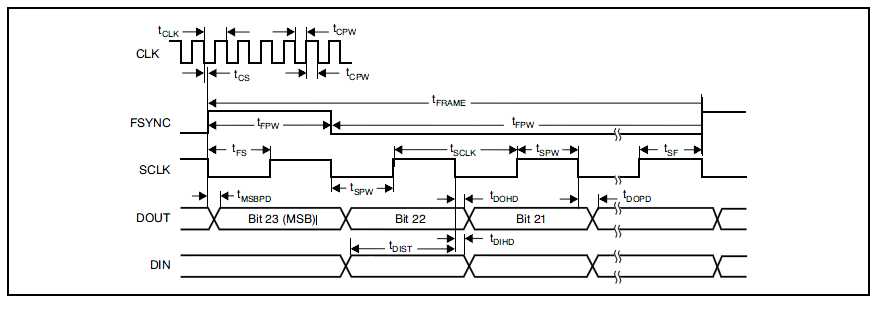

此次设计为Frame-Sync模式,时序图为下图:

时序制作时需要注意以下几点:

1. FSYNC为高电平启动数据传输, SCLK的第一个低电平时,AD1274准备第一个数据,在FSYNC为高电平后的SCLK的第一个上升沿取第一个数据。

2. FSYNC的高电平必须大于一个SCLK的时钟周期

3. FSYNC的周期必需大于CLK的256倍,且小于2560倍。这个一定要注意,开始的时候就是因为这个导致数据出错。

4. SCLK为必须为CLK的1、2、4、8的分频

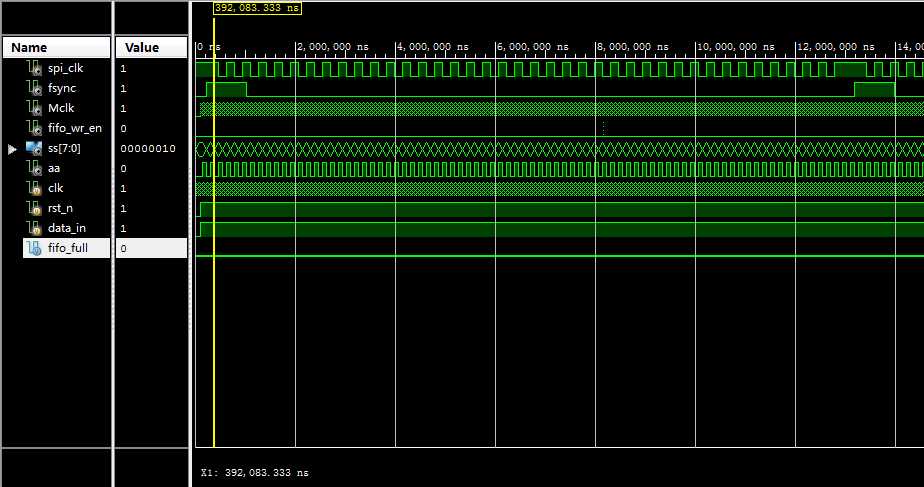

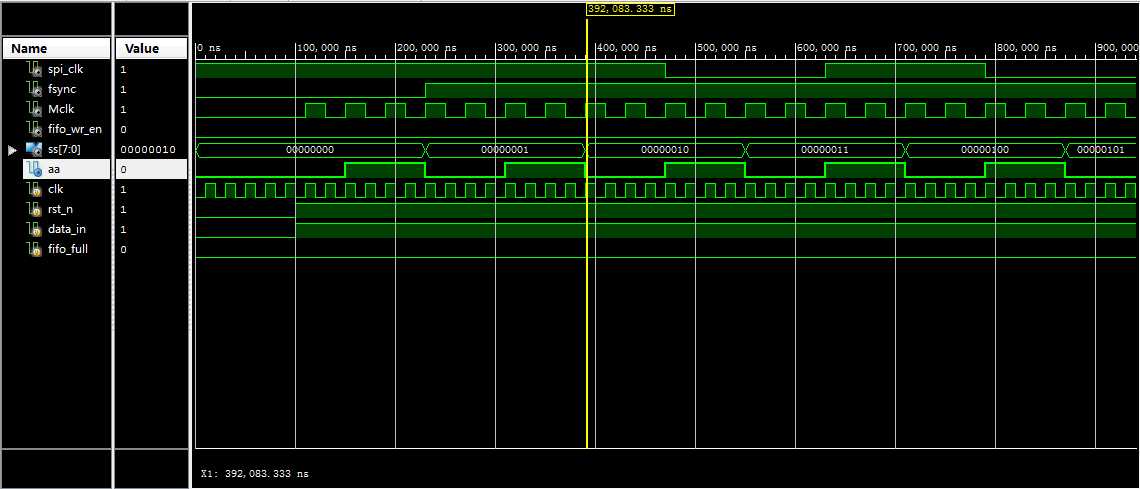

以下为isim一个完整周期的仿真时序:

以下是FPGA的程序设计:

moduleAD_frame_sync(

clk,rst_n,Mclk,

spi_clk,fsync,

data_in,

ad_dataout,

fifo_wr_en,

fifo_full,

ss,aa

);

input clk; //FPAG输入时钟信号50MHz

input rst_n; //FPGA输入复位信号

input data_in; //AD数据输入信号线

input fifo_full;

output aa;

output [7:0]ss;

outputfifo_wr_en; //ad data OK

output[23:0]ad_dataout; //ad data out

output Mclk; //AD1274’s master clk

output spi_clk; //farme_sync的时钟线

output fsync; //farme_sync的启动信号线

//——————————————————————————————-//

//function:AD1274’smaster clk form FPGA’s clk,f_master = fpga_clk/2=50MHz/2=25MHz

//———————————–

reg cc;

always @(posedge clkor negedge rst_n)

if(!rst_n)

cc <= 1’b0;

else

cc <= cc + 1’b1;

assign Mclk =cc;

//———————————–

//———————————————————————————————//

//function: clk8m =f_master /4 =25MHz/4=6.25MHz

//————————————-

reg[1:0] acc;

always @(posedgeMclk or negedge rst_n)

if(!rst_n)

acc <= 1’b0;

else

acc <= acc + 1’b1;

assign clk8m =acc[1];

//————————————-

//———————————————————————————————//

//function:count forSPI Time sequence

//—————————————-

reg[7:0] cnt8; //SPI Time sequencecounter ,Count range:0-51

reg fsync_reg; //SPI read control wire:fsync’s register

always @(negedgeclk8m or negedge rst_n)

if(!rst_n)

begin

cnt8 <= 8’d0;

fsync_reg <= 1’b0;

end

else if(cnt8 < 8’d80)

begin

cnt8 <= cnt8+1’b1;

if(cnt8 < 5)

fsync_reg <= 1’b1; //SPI read enable,fsync_reg = 1;

else

fsync_reg <= 1’b0;

end

else cnt8 <= 8’d0; //SPIcount reset

assign fsync =fsync_reg;

assign ss = cnt8;

assign aa = clk8m;

//—————————————-

//———————————————————————————————-//

//function: creatspi_clk

//—————————————-

reg spi_clkr; //spi_clkregister

always @(posedgeclk8m or negedge rst_n)

if(!rst_n) spi_clkr <= 1’b1; //spi_clk initial level is 1

else if(cnt8 > 8’d1 && cnt8 <8’d80)

spi_clkr <= ~spi_clkr; //whencnt8 at 2 to 51 ,spi_clkr flip

else if(cnt8 <= 8’d1)

spi_clkr <= 1’b1; //spi_clk initial level is 1

assign spi_clk =spi_clkr;

//—————————————-

//———————————————————————————————–//

//function:receive24bit data from ad1274

//——————————————-

reg[23:0]ad_datareg; //24 bit data register

reg[23:0]ad_datareg1;

reg ad_dataOkreg;

always @(posedgeclk8m or negedge rst_n)

if(!rst_n)

begin

ad_datareg <= 0;

ad_dataOkreg <= 0;

end

else if(!fifo_full)

begin

case(cnt8)

8’d3:ad_datareg[23] <= data_in;

// begin

// ad_datareg1<= ad_datareg1 +1; //receivebit23

//end

8’d5:ad_datareg[22] <= data_in; //receivebit22

8’d7:ad_datareg[21] <= data_in; //receivebit21

8’d9:ad_datareg[20] <= data_in; //receivebit20

8’d11:ad_datareg[19] <= data_in; //receivebit19

8’d13:ad_datareg[18] <= data_in; //receivebit18

8’d15: ad_datareg[17]<= data_in; //receivebit17

8’d17:ad_datareg[16] <= data_in; //receivebit16

8’d19:ad_datareg[15] <= data_in; //receivebit15

8’d21:ad_datareg[14] <= data_in; //receivebit14

8’d23:ad_datareg[13] <= data_in; //receivebit13

8’d25:ad_datareg[12] <= data_in; //receivebit12

8’d27:ad_datareg[11] <= data_in; //receivebit11

8’d29:ad_datareg[10] <= data_in; //receivebit10

8’d31:ad_datareg[9] <= data_in; //receivebit9

8’d33:ad_datareg[8] <= data_in; //receivebit8

8’d35:ad_datareg[7] <= data_in; //receivebit7

8’d37:ad_datareg[6] <= data_in; //receivebit6

8’d39:ad_datareg[5] <= data_in; //receivebit5

8’d41:ad_datareg[4] <= data_in; //receivebit4

8’d43: ad_datareg[3]<= data_in; //receivebit3

8’d45:ad_datareg[2] <= data_in; //receivebit2

8’d47:ad_datareg[1] <= data_in; //receivebit1

8’d49:ad_datareg[0] <= data_in; //receivebit0

8’d50:ad_dataOkreg <= 1’b1; //set ad_dataOk 1,write data to fifo

8’d51:ad_dataOkreg <= 1’b0; //set ad_dataOk 0

default: ;

endcase

end

assignad_dataout[23:0] = ad_datareg[23:0];

//——————————————-

//———————————————————————————————–//

//function:catchad_dataOkreg’s Rising edge,for the fifo write enable Signal

//———————————–

regad_dataOkreg1,ad_dataOkreg2; //ad_dataOkreg寄存器

always @(negedge clkor negedge rst_n)

if(!rst_n) begin

ad_dataOkreg1 <= 1’b1;

ad_dataOkreg2 <= 1’b1;

end

else begin

ad_dataOkreg1 <=ad_dataOkreg;

ad_dataOkreg2 <=ad_dataOkreg1;

end

assign fifo_wr_en =ad_dataOkreg1 & (~ad_dataOkreg2); //ad_dataOkreg上升沿置高一个时钟周期

//————————————

Endmodule

yi

EMEQGROUP

2012.03.06

今天的文章Xilinx Spartan 6 驱动ADS1278/4分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/33403.html