感谢阅读本文,在接下来很长的一段时间里,我将陆续分享项目实战经验。从电源、单片机、晶体管、驱动电路、显示电路、有线通讯、无线通信、传感器、原理图设计、PCB设计、软件设计、上位机等,给新手综合学习的平台,给老司机交流的平台。所有文章来源于项目实战,属于原创。

一、拓扑结构

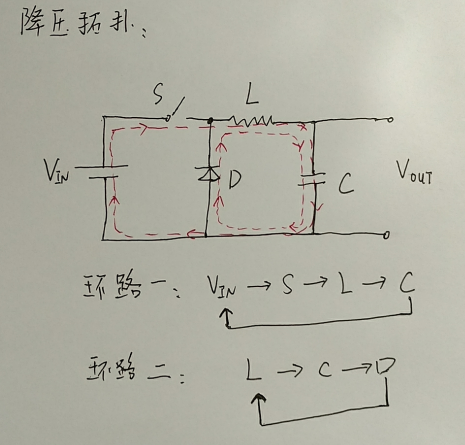

1、降压拓扑如上图,要想掌握降压电路,必须深刻理解拓扑结构,几乎所有降压DC to DC都是基于此拓扑结构。

2、环路一,开关导通时的电流路径;环路二,开关闭合时的电流路径。闭合环路,变化的电流产生磁场,为了降低EMC,设计PCB时,环路设计应该尽量小,同时,不要干扰了模拟电路,比如反馈回路、增益补偿、使能部分等。

3、为了降低功耗,功率电感应该选取低DCR的,饱和电流为平均电流的4/3(经验值);续流二极管D选取肖特基二极管,或选择同步降压IC(集成了续流二极管)。

4、为了降低输出纹波,电感值、电容值需要选择合适的值,一般datasheet有推荐, 电感值越大,相对纹波越小,同时,由于电感阻碍电流变化,导致响应负载的速度变慢;电容一般选用铝电解电容与陶瓷电容(低ESR)的组合,高度有限制或

今天的文章dc-dc降压电路原理_dcdc隔离电源方案分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/77283.html