目录

1.测试分类

半导体测试就是通过测量半导体的输出响应和预期输出并进行比较以确定或评估集成电路功能和性能的过程。

根据分类标准不同可以有多种分类有以下几种分类:

1.1 参数测试和功能测试。

参数测试:

参数测试验证的是电路的参数是否符合要求,采用诸如电流和电压之类的参数进行测量

功能测试:

功能测试是检测被测试的电路(组合逻辑,时序逻辑,存储器)在指定的输入条件下的输出是否正确。它是基于逻辑电平的故障检测,逻辑电平值通过测量原始输出的电压来确定,因此功能测试实际上是电压测试。(VLSI测试方法学和可测性设计-雷绍充)

但是还有下面的分类描述

摘自半导体测试ATE产业详解,国产机会在哪里?_手机搜狐网

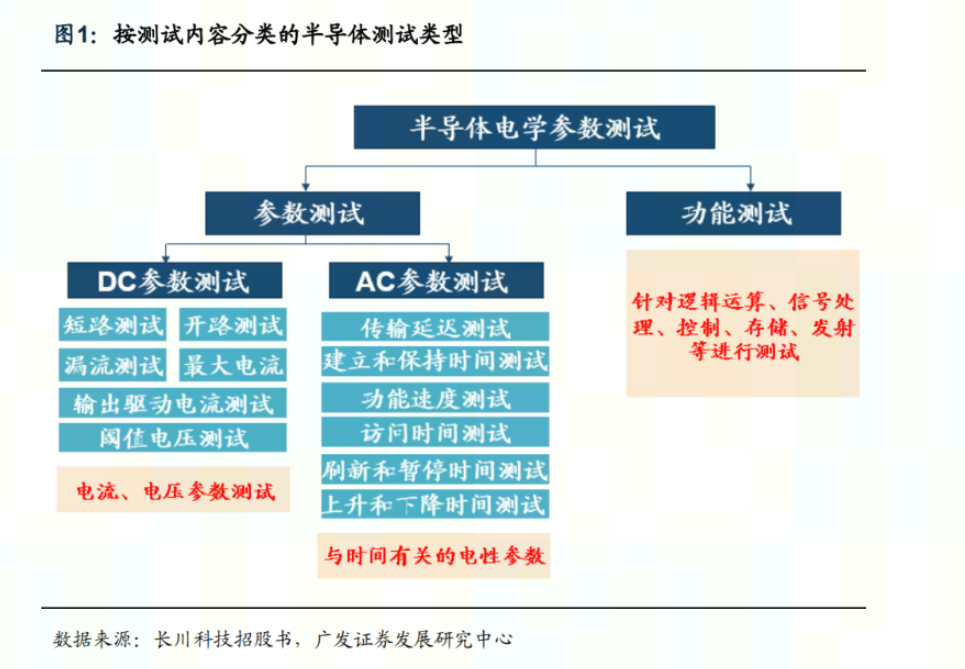

(1)参数测试。参数测试是确定芯片管脚是否符合各种上升和下降时间、建立和保持时间、高低电压阈值和高低电流规范,包括DC(Direct Current)参数测试与AC(Alternating Current)参数测试。DC参数测试包括短路测试、开路测试、最大电流测试等。AC参数测试包括传输延迟测试、建立和保持时间测试、功能速度测试等。这些测试通常都是与工艺相关的。CMOS输出电压测量不需要负载,而TTL器件则需要电流负载。

(2)功能测试。功能测试决定芯片的内部数字逻辑和模拟子系统的行为是否符合期望。这些测试由输入适量和相应的响应构成。他们通过测试芯片内部节点来检查一个验证过的设计是否正产工作。功能测试对逻辑电路的典型故障有很高的覆盖率。

所以拿DC和AC测试来说,在慢时钟的情况下是可以测出大部分的短路 开路问题(stuck-at).AC呢在正常时钟又可以测试元件的transition问题。

很多分类采用标准不同可能相互交叉。

1.2 根据测量输出电流还是电压

电压测试:

判断输出的逻辑电平正确与否,

电流测试:

常见的一种

1.3 根据测试激励的快慢

DC (static)testing

测试激励比正常工作要慢很多的时钟

AC testing (At-speed testing)

测试激励使用正常时钟

DC/AC分类来自Digital systems testing and testable design —Miron Abramovici

具体可参考:

VLSI芯片电路测试分类testMode、模式、时钟复位输入输出

需要说明的是 DC/AC并不对应具体的测试内容,scan测试的stuck-at 属于DC测试,at speed scan test属于AC测试。结合DC/AC与scan就是 DC scan test,AC scan test。

funcTest也有DC和AC的划分。

有时也会把DC/AC专指scan测试。注意语境区分

1.4 根据测试对象为模拟电路还是数字电路

数字电路常见测试方法

mbist、lbist、scan

模拟电路测试方法

burn-in,analogy-test

1.5 其他

参见Digital systems testing and testable design —Miron Abramovici的page4

2.testMode与functionMode

芯片测试一般都会分为testMode和functionMode。这两种测试的区别在于:

1.testMode在测试的时候 时钟,复位,电路结构[scan chain,需要专用jtag],激励和芯片正常工作的都不太一样。更偏向于第1.1节说的参数测试

2.functionMode就是让芯片工作在正常的功能模式,不在需要jtag而是直接boot cpu 来测试具体的芯片功能,但是这个测试空间有限,毕竟大规模测试还是回片测试。这里就偏向于第1.1节说的功能测试和verification/simulation相比,这个func测试testPattern有限,不是侧重业务的,用在回片筛片。筛完片 才有大规格的回片测试。

ptest=1就被称作testMode,而对于ptest=0 被称为function mode (区别于function test)。

2.1 test_mode的实例

下面给出了一系列的测试mode,根据输入ptest和test_mode分成了很多的mode。

input ptest;

input [3:0] test_mode;

output ptest_mbist_mode;

output ptest_scan_mode;

output ptest_lbist_mode;

output ptest_func_mode;

output ptest_ana_mode;

output ptest_atb_mode;首先这里的所有的测试需要 ptest=1才有效

然后根据test_mode decode出很多的面向某一测试的模式(根据测试方案而定)。

在电路设计过程中,电路根据以上不同的mode选择不同的时钟,复位,输入源和输出源。

其中scan_mode/mbist_mode就属于DFT同事主要处理的工作

atb_mode就是ATE机台测试,需要用到机台的都可以包在这个mode下。atb_mode可以完全包含ptest_func_mode,还可以包含buruin的一部分。

比如burunin测试分为ip的burnin和dft pattern的burnin,ip的burnin要用到机台就划到了atb_mode;dft pattern的burnin又分别划到了mbist_mode和scan_mode。

又比如 ip的iddp测试属于atb_mode;soc的iddq是mentor提供的flow 是在scan环境中产生,所以属于scan_mode

又因为 atb_mode包含多个测试,所以单独划出了ptest_func_mode.

上面这种测试方案就没有单独的burnin_mode和iddq_mode。换一种测试方案可能test_mode的取值会不一样。

2.1.1 function test

我们可以在testMode下测试function,也可以在funcMode下测试function。

这里讲的是在testMode下func test 对应ptest_func_mode==1

测试目的:

测试逻辑运算,控制等电路。

所以电路工作在正常功能模式下,测试clk是内部PLL输出的功能clk。

这种测试mode:

1. 输入的testPattern,通过Funcjtag来输入,也有可能就存在片上sram或片外flash

2. 寄存器 通过funcjtag,然后jtag2axi来配置芯片内部各功能模块

2.2 functionMode下的测试

1. 输入的testPattern,可能就存在片上sram或片外flash

2.寄存器用cpu来配置

常见的SLT(system level Test)主要就是funcMode下的测试,测试芯片的功能性能等。

2.3 测试与jtag

测试经常需要jtag电路,但也不是所有测试都需要jtag。比如有的测试是把pattern和结果都存在片上sram中,在空闲时刻 待测单元 读取sram中testPattern 并将输出与sram中的测试结果比对。这个过程就可以没有jtag。下面讲一讲有jtag的。

实际中的测试构架中有三类jtag:

1.testJtag

testJtag是菊花链的拓扑,相关subsys的testJtag都会串上来。用的是jtag拓扑网络的tap controller。可以用于scan_mode,mbist_mode和atb_mode的测试。

比如scan_mode下对scan-chain灌testPattern 和 测试指令,输出测试结果。

2.funcJtag

主要用在funcTest,由2.1.1节可知,func Test需要配置正常的功能寄存器,这时可以使用cpu来配置也可以用funcJtag。那么这个Jtag就不能用tap controller,我们通过jtag2axi将funcJtag接口转为axi接口就可以挂在nic上配置各subsys的apb slave。

这个funcJtag也是要上菊花链的,才能将多个subsys的funcJtag互联。

3.个别模拟IP自带的Jtag

比如pcie和hdmi的第三方phy都有jtag接口,这些jtag接口一般不用上DFT的testJtag链,因为这些IP的数字部分 我们在做DFT的时候可以直接通过subsys的testJtag来测试。另一方面这个Jtag一般也不上funcJtag的菊花链,上一段也说了 funcJtag可以访问subsys的所有apb slave,所以也可以通过funcJtag做func test。最终这些phy自带的Jtag直接接到了pad。

这样第三方phy在需要一些独特的测试时可以直接用这个Jtag:比如第三方提供的LoopBack测试。此时无论用来做机台测试或功能测试,比用funcJtag的链要短,速度自然也快一些。

3.测试模式下的时钟复位输入输出

选择不同的时钟是因为有DC/AC测试的需求;

选择复位是因为测试模式下需要将被测试电路复位到确定的状态,之所以没用系统复位有两个原因:1.测试时钟可能和系统时钟异步。2.被测试电路不一定和正常工作电路处于相同的复位域

选择输入是因为测试状态下激励来源不同于正常工作的激励

选择输出是因为输出的路径可能和正常工作路径不同

今天的文章verilog时钟模块_led型驱动芯片9609s资料分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/81403.html