使用PH1A100 DEMO板卡进行GMII以太网接口设计和测试

一、设计概述

TD软件版本:TD5.0.5-64bit

工程 :PH1_TEMAC_GMII_DEMO

参考工程 : APUG008_三速以太网 MAC 应用方案、EG4_TEMAC_GMII_DEMO工程

测试方案 :mac1_demo工程 与 PC 对接,帧间间隙为发包工具最小设置值1ms

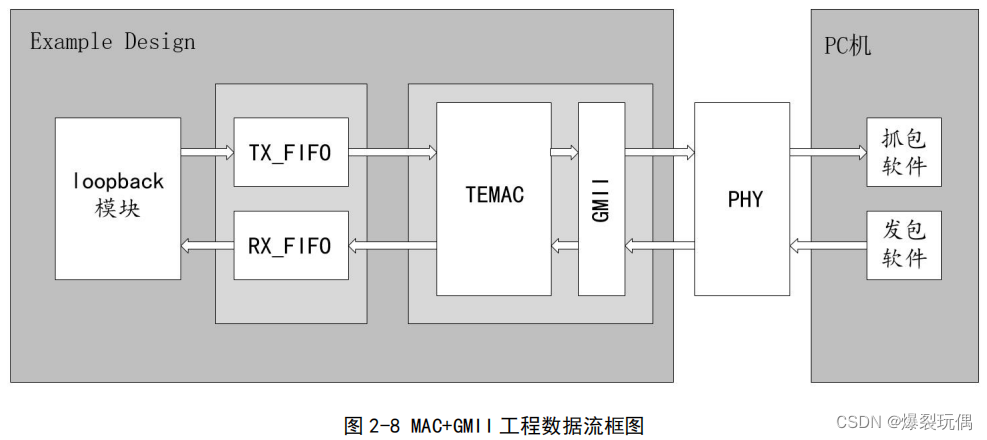

数据环回路径:发包工具—>GMII_RXD—>MAC核—>RX_DATA—>LOOPBACK—>TX_DATA—>MAC核—>GMII_TXD—>收包工具。

二、工程设计模块

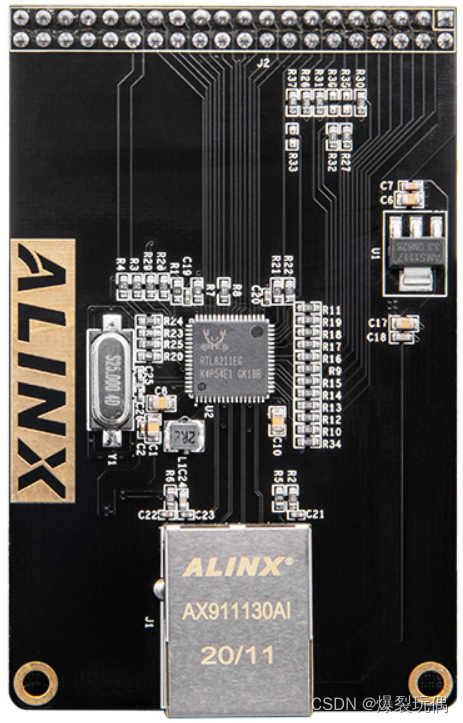

本次设计的以太网模块并未使用PH1A100 DEMO板卡板载以太网模块,而是使用黑金AN8211以太网模块,能够支持10/100/1000 Mbps。

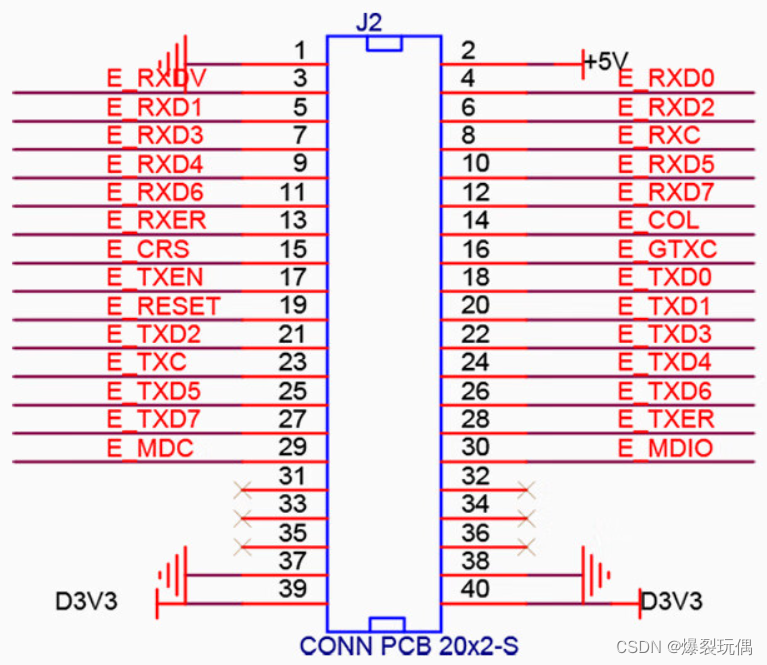

该模块的接口定义为:

本次设计的工程框架如图:

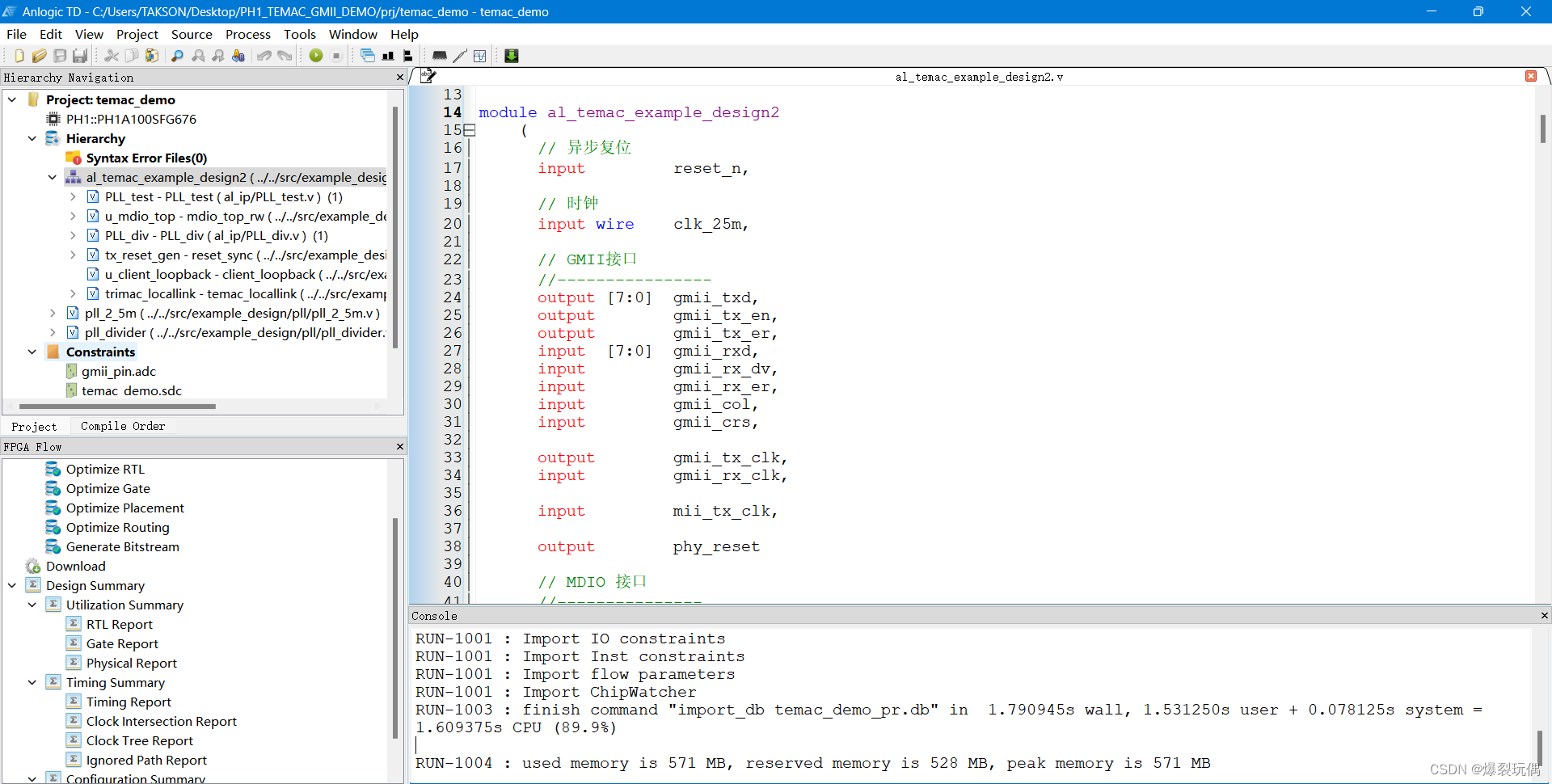

本次设计的顶层和整体工程结构如下:

主要采用的是PLL 模块生成对应的GMII时钟驱动信号,即125MHZ。

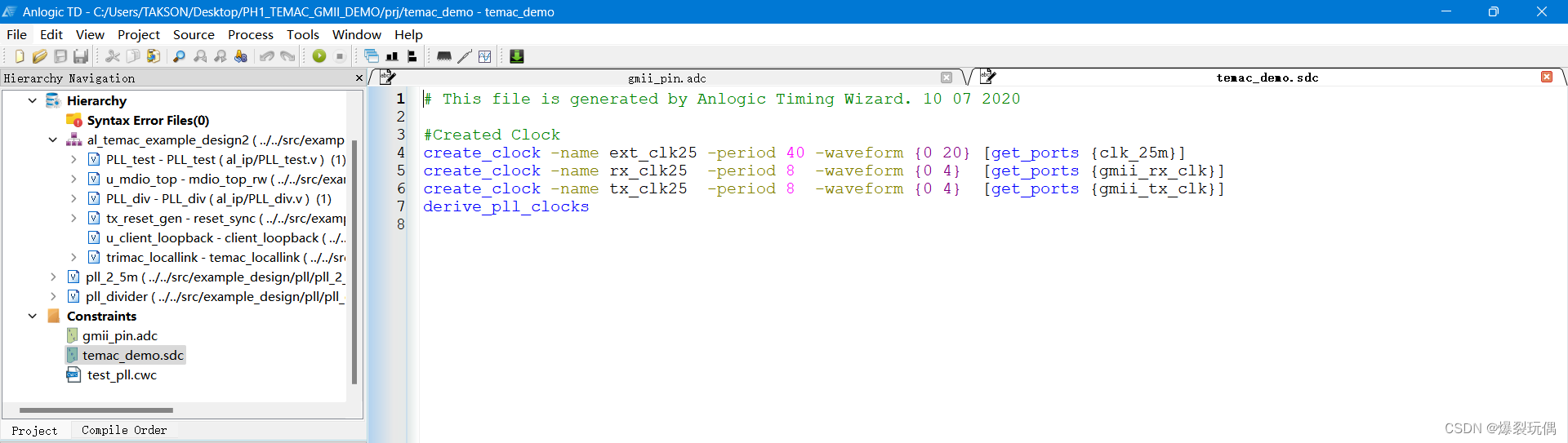

时序约束为:

- 对PLL IP进行时序约束;

- 对clk_25m系统时钟进行时序约束;

- 对gmii_rx_clk和gmii_tx_clk进行时序约束;

二、板载测试

1. 板载连接

AN8211以太网模块直接连接DEMO板卡的user IO1,并且具有防反插功能,可以直接进行连接,对应接口可以对应原理图进行对接;

2. 软件配置

- 根据APUG008手册,在电脑/属性/设备管理器/网络适配器/Realtek pcie GBE Family Controller 属性/高级中,选择“自动侦测”或“1Gbps 全双工”。

注意:各个不同的网口可能名称不同,不用局限为Realtek pcie GBE Family Controller名称。

2. 打开发包软件 XCAP 和抓包软件 Wireshark。发包软件 XCAP 中启动接口,抓包软件 Wireshark 中开始捕获数据。

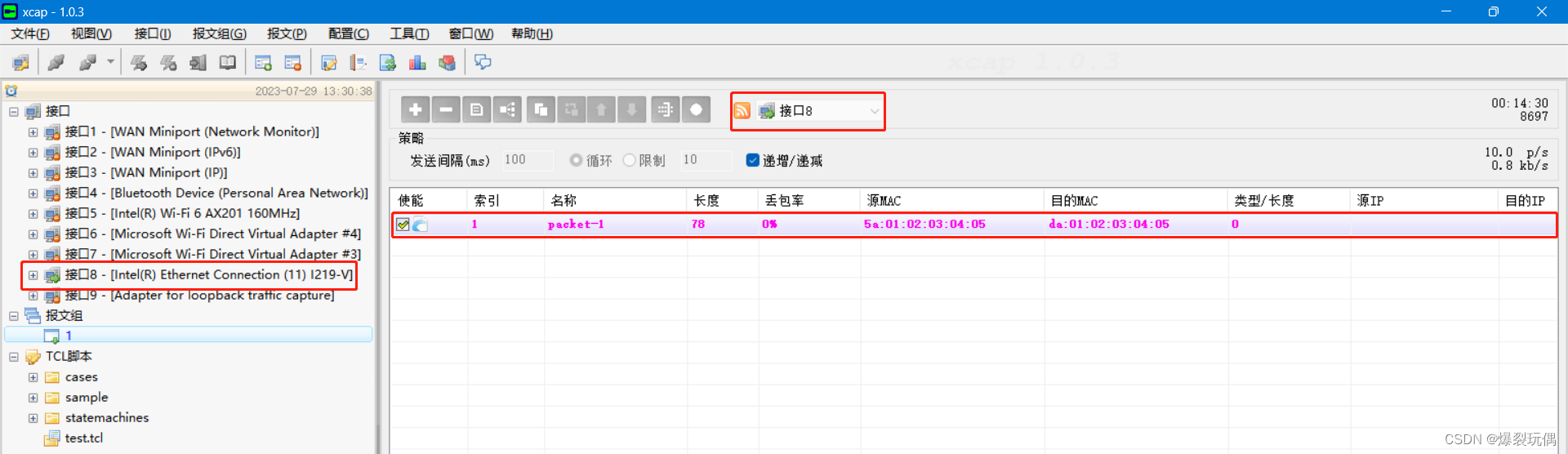

XCAP软件设置如下:

(1)首先需要将对应的网络接口进行连接;

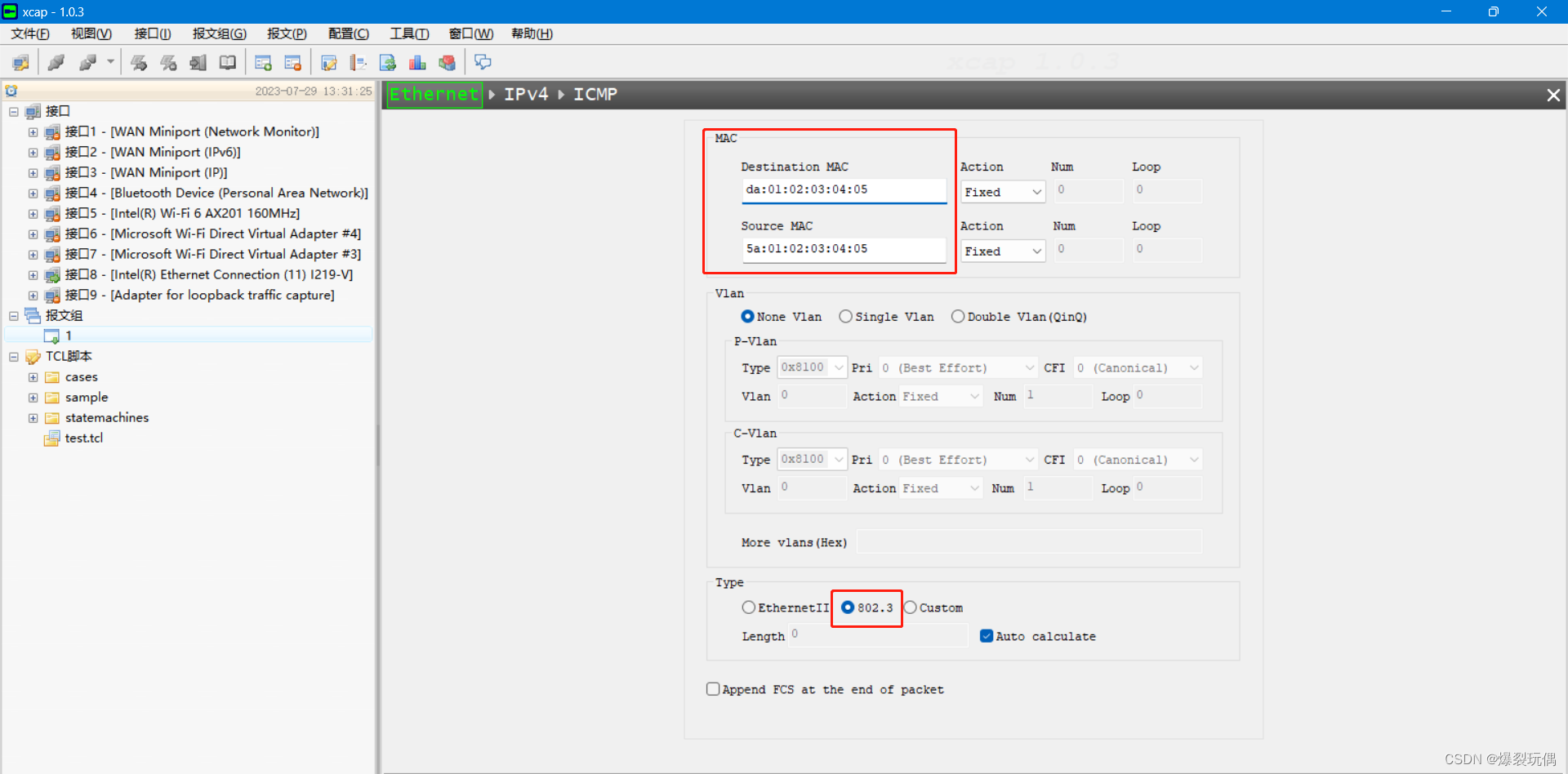

(2)然后新建一个报文组,并进行设计,主要设置为目的MAC地址和源MAC地址,并且tpye选择802.3,其他设置默认即可。

注意:目的MAC地址和源MAC地址为FPGA工程中设计制定部分,可以直接进行添加。

3. 实测结果

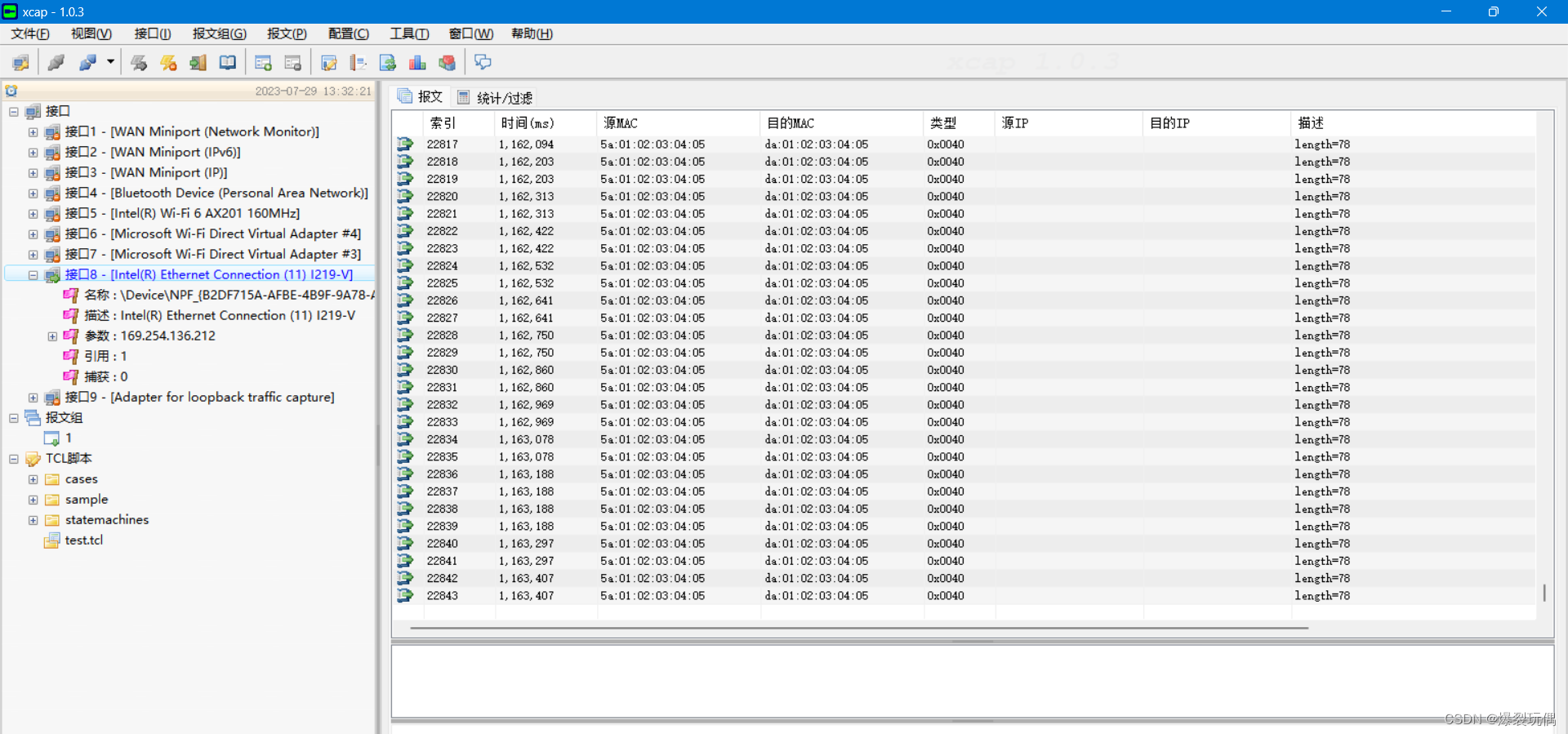

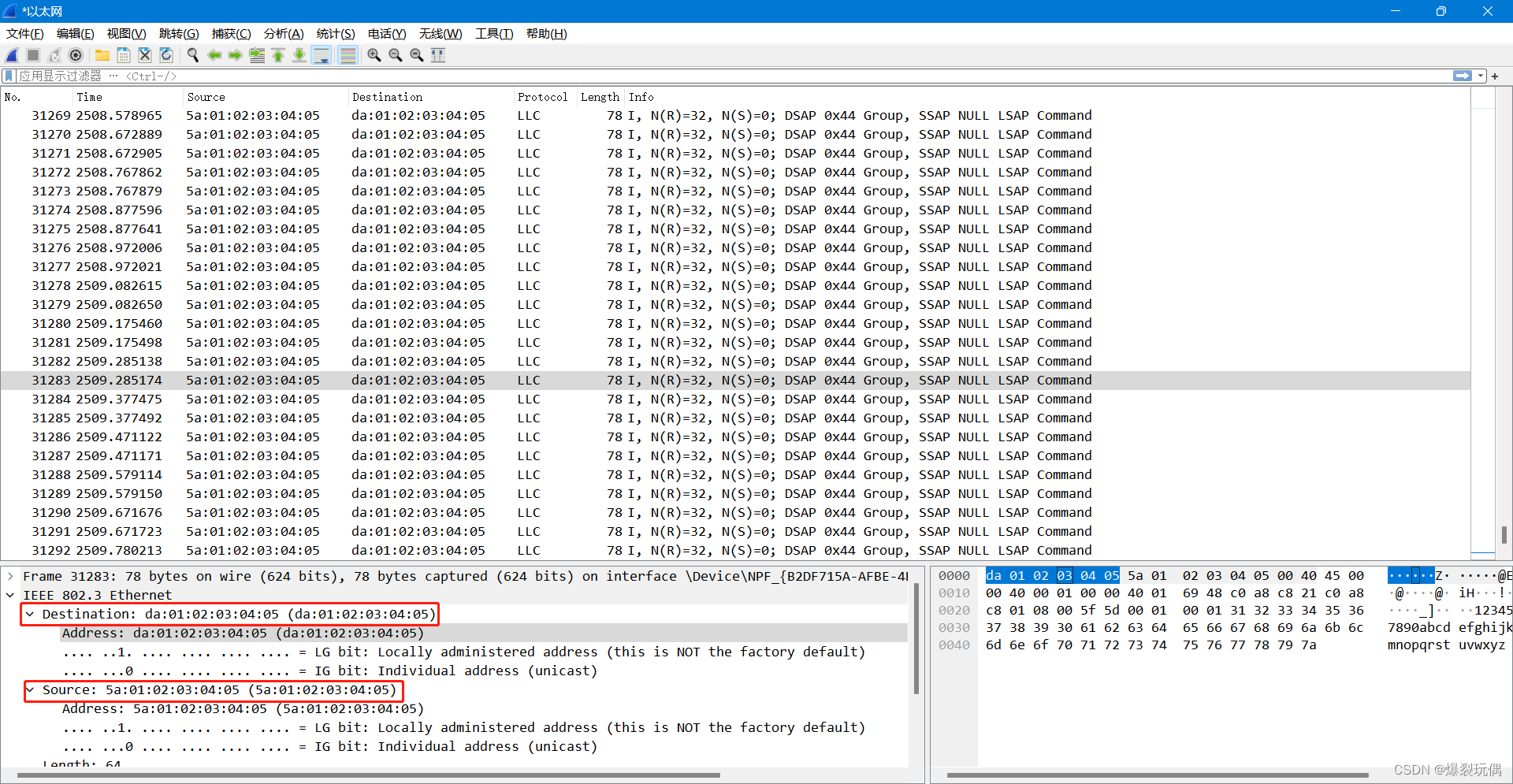

通过XCAP软件可以进行自动发包,根据手册可以进行间隔1ms的发包,但这个软件在发送时间过快时会自动退出,在接口对应位置可以直接抓取包进行查看。

并且可以在Wireshark中可以抓到对应的网络数据。

今天的文章安路科技fpga入门_常用fpga芯片的型号「建议收藏」分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/89670.html