本文转自:【FPGA】:ip核–Divider(除法器)

二、 Divider(除法器)

概述

除法器顾名思义,用来做除法运算。

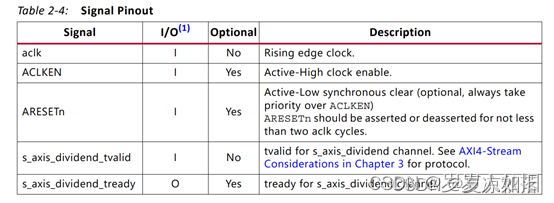

端口说明

ip核的生成

(1)在ip catalog里面选择Divders

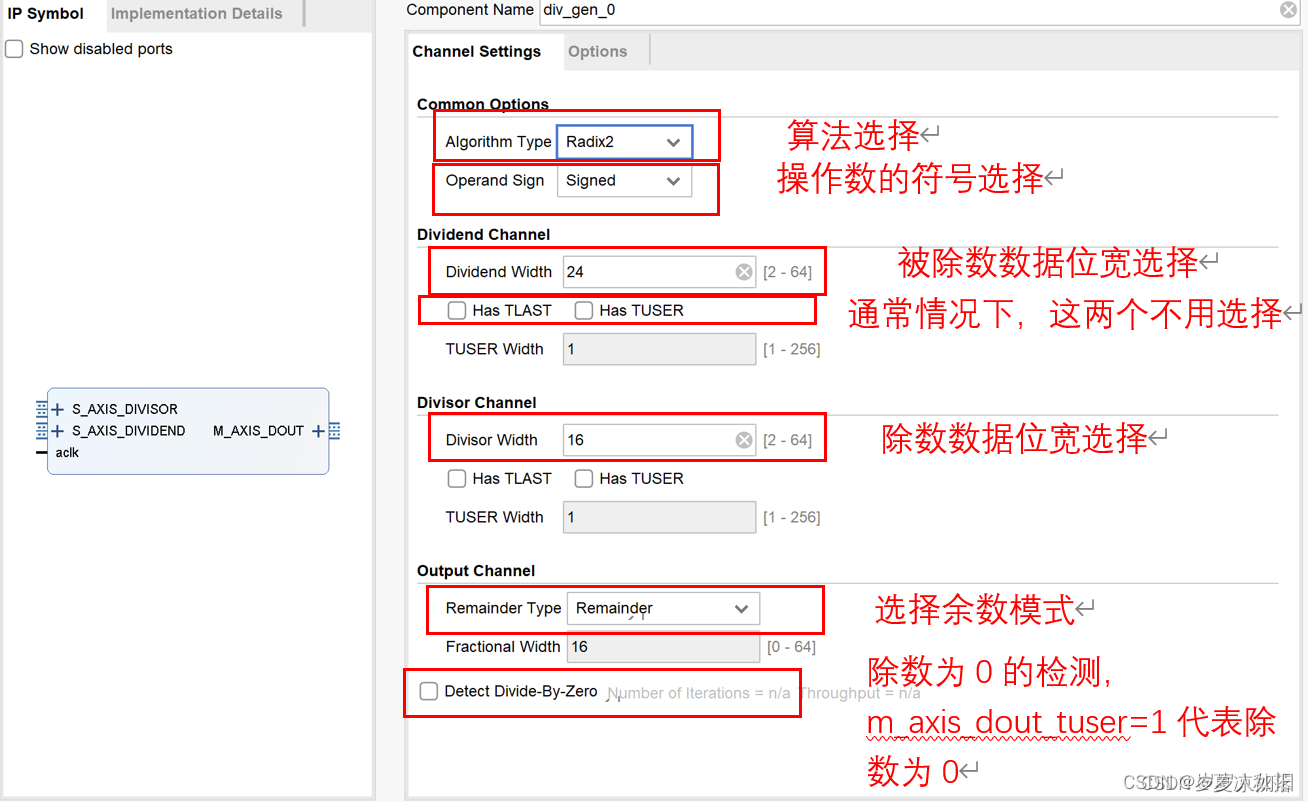

(2)channel setting,具体如下所述:

- Algorithm type: 选择不同的算法模式,其中Radix2为常用的模式(位宽12到16时优先考虑),LutMult当时数较小的时候使用(数据宽度小于等于12时,优先考虑),High Radix是当数很大的时候使用(数据位宽大于16时)。常用的是Radix2。

- Dividend Width:被除数的位数。

- Has TLAST: 指定此通道是否具有 tlast 端口。 除法器不使用此信息。 该项用于简化系统设计。tlast信息以和数据路径相同的延迟传送到输出通道。

- Has TUSER: 指定此通道是否具有 tuser 端口。 与 tlast 一样, 除法器不使用此信息。 该项用于简化系统设计。 tuser 位以和数据路径相同的延迟传送到输出。

- TUSER Width: 当 Has tuser 为 TRUE 时可用,这将设置此通道的 tuser 端口的宽度。

- Divisor Width:除数的位数。

- Remainder Type:选择余数的模式。有两种模式:Remainder:余数,以及Fractional分数模式。

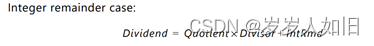

- Remainder模式的余数模式位数固定,由系统根据除数自动设定。,计算公式为

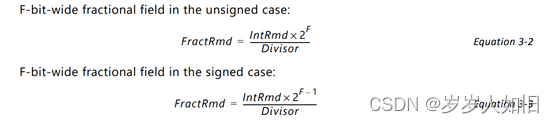

比如:6/-4 = -1 REMD 2 -6/4 = -1 REMD –2。 其中商的位宽和被除数的位宽一致,位于高位,余数的位宽和除数的位宽一致,位于低位。 - Fractional Width(f分数模式)模式,则可以在Fractional Width那一栏选择自己想要的余数位数。对于带分数输出的带符号模式,符号位同时存在于商和分数域中。例如,对于一个5位被除数、除数和分数输出:

− 9 / 4 = 9 / − 4 = − ( 21 / 4 ) ,对应的为 10111 / 00100 o r 01001 / 11100 -9/4 = 9/-4 = -(2 1/4),对应的为10111/00100 or 01001/11100 −9/4=9/−4=−(21/4),对应的为10111/00100or01001/11100

其结果为 Quotient(商) = 11110 (= -2) Remainder (余数)= 11100 (= -1/4)

- Remainder模式的余数模式位数固定,由系统根据除数自动设定。,计算公式为

常用模式为Remainder模式。本文也应选则Remainder模式。

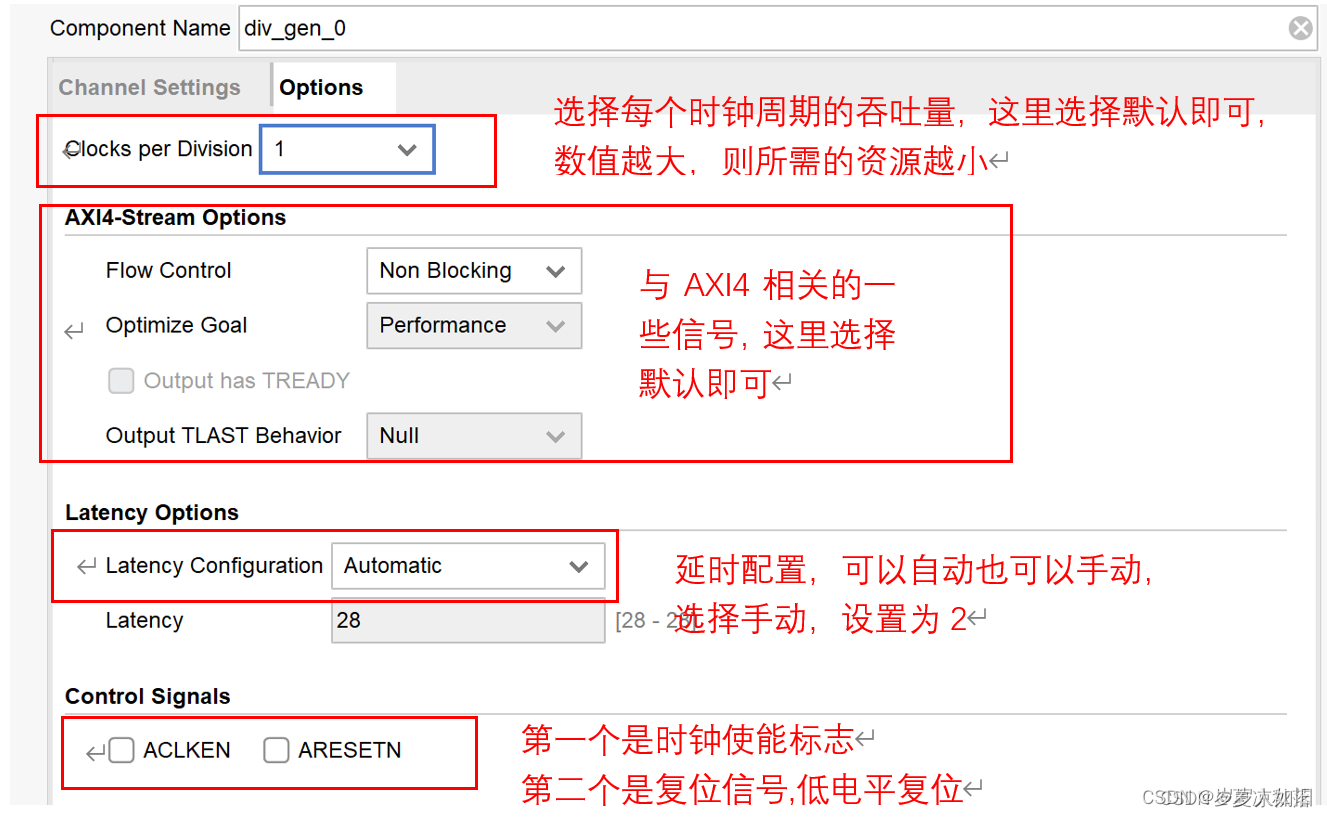

(3)option的设置,具体如下所述:

2.4 测试代码

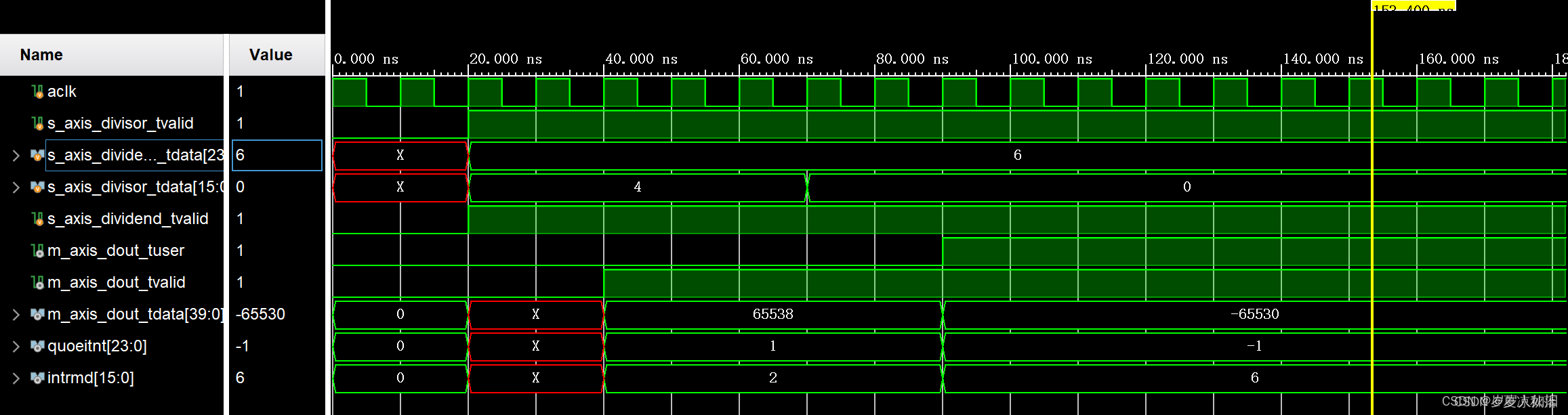

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 2022/01/16 15:00:44 // Design Name: // Module Name: divider_tb // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // // module divider_tb(); reg aclk; reg s_axis_divisor_tvalid; reg [15:0] s_axis_divisor_tdata; reg [23:0] s_axis_dividend_tdata; reg s_axis_dividend_tvalid; wire m_axis_dout_tuser; wire m_axis_dout_tvalid; wire [39:0] m_axis_dout_tdata; wire [23:0] quoeitnt; //除数 wire [15:0] intrmd ; //余数 assign quoeitnt = m_axis_dout_tdata[39:16]; assign intrmd = m_axis_dout_tdatac[15:0]; div_gen_0 div_gen_0_inst0 ( .aclk(aclk), // input wire aclk .s_axis_divisor_tvalid(s_axis_divisor_tvalid), // input wire s_axis_divisor_tvalid .s_axis_divisor_tdata(s_axis_divisor_tdata), // input wire [15 : 0] s_axis_divisor_tdata .s_axis_dividend_tvalid(s_axis_dividend_tvalid), // input wire s_axis_dividend_tvalid .s_axis_dividend_tdata(s_axis_dividend_tdata), // input wire [23 : 0] s_axis_dividend_tdata .m_axis_dout_tvalid(m_axis_dout_tvalid), // output wire m_axis_dout_tvalid .m_axis_dout_tuser(m_axis_dout_tuser), // output wire [0 : 0] m_axis_dout_tuser .m_axis_dout_tdata(m_axis_dout_tdata) // output wire [39 : 0] m_axis_dout_tdata ); initial aclk=1; always #5 aclk=~aclk; initial begin s_axis_dividend_tvalid=0; s_axis_divisor_tvalid =0; #20; s_axis_dividend_tdata = 24'd6; s_axis_divisor_tdata = 16'd4; s_axis_dividend_tvalid=1; s_axis_divisor_tvalid =1; #50; s_axis_divisor_tdata = 16'd0; end endmodule 仿真结果

从图中可以看出,输出m_axis_dout_tdata滞后于输入2个时钟周期,这与ip核设置的一致,当除数位0时,发现m_axis_dout_tuser信号拉高,说明输入的除数为0,此时输出结果无效。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/bian-cheng-ji-chu/87266.html