感觉教材和网络上对于计算机系统的结构描述都比较模糊,我自己对其进行了总结,并且画出图,不过因为学习的还是不够深入和全面,有的地方肯定是有问题的,烦请大家批评指正,我会进行修改~

现代计算机的系统层次结构为冯·诺依曼结构,其最大特点是存储程序;

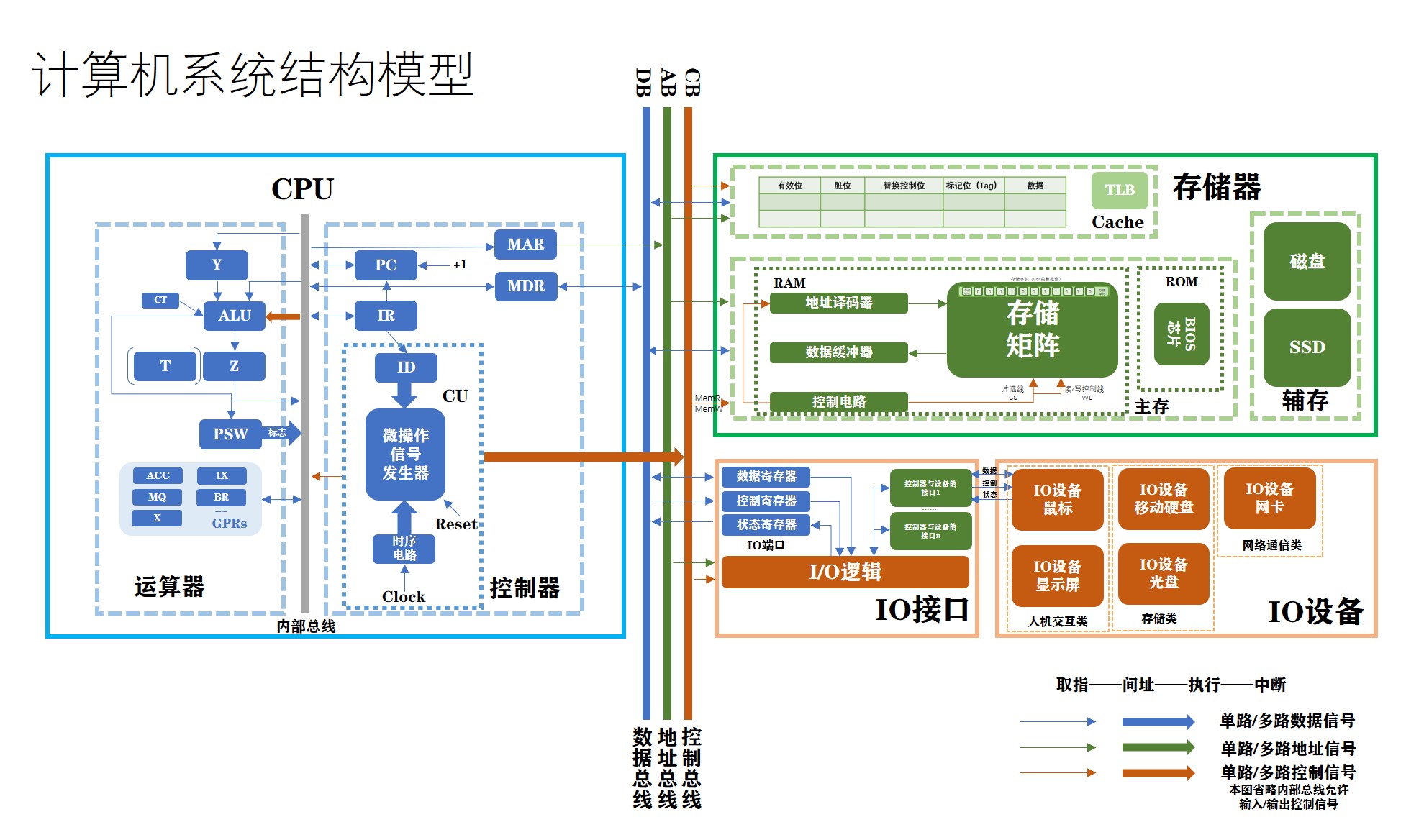

硬件部分主要包括运算器、控制器(二者组成CPU)、存储器、输入输出设备(I/O设备),如计算机系统结构模型图所示,硬件能直接执行的能且只能是机器语言;

软件部分分为系统软件与应用软件,编写诸如操作系统、编译程序等各种系统软件的人员称为系统程序员,利用计算机及所支持的系统软件来编写解决具体应用问题的人员称为应用程序员;

软件和硬件之间的界面就是指令集体系结构(ISA),定义了一台计算机可以执行的所有指令的集合,每条指令规定了计算机执行什么操作,以及所处理的操作数存放的地址空间和操作数类型,指令字和指令格式、通用寄存器个数和位数都与机器指令有关,由ISA规定。要注意ISA仅规定与指令有关的,而不规定CPU时钟周期、加法器的进位方式等,简单来说,ISA是硬件与底层软件接口,不会规定过于底层硬件的东西。

下面我们就来详细说说硬件部分的构成。

作用:运算与控制的指挥中心;

作用:运算器接收从控制器送来的命令并执行相应的动作,对数据进行加工和处理,执行算数运算和逻辑运算;

1.算术逻辑单元(ALU):进行算术、逻辑运算 ;

2.通用寄存器(GPRs):用于存放操作数 (包括源操作数、目的操作数及中间结果)和各种地址信息等;

(1)累加寄存器 (ACC):是一个通用寄存器,用于暂时存放 ALU 运算的结果信息,可以作为加法运算的一个输入端;

(2)乘商寄存器(MQ):加法减法不使用,存乘数及乘积低位、商;

(3)操作数寄存器(X):存加数、减数、被乘数、除数;

(4)变址寄存器(IX):存储应用程序的长度;

(5)基址寄存器 (BR):存储数据内存的起始位置;

对于通用寄存器组的一些说明:上面总结的是考试时常用的通用寄存器,不同系统的通用寄存器组各有不同,比如X86架构下的通用寄存器组如下图:

而ARM架构下的通用寄存器组如下图:

3.程序状态字寄存器(标志寄存器)(PSW):存放ALU运算得到的标志信息和处理机的状态信息,保留由算术逻辑运算指令或测试指令的结果而建立的各种状态信息如溢出标志(OF)、符号标志 (SF)、零标志 (ZF)、进位标志 (CF)等。PSW 中的这些位参与并决定微操作的形成;

4.暂存寄存器(Z、Y):用于暂存读来的数据,由于单总线数据通路中,每一时刻总线上只有一个数据有效,而ALU是一个没有存储功能的组合逻辑元件,在其执行运算时必须保持两个输入端同时有效,因此可以将一个操作数先放入暂存器Y中保存,使得其内容在ALU的一端始终有效,再将另一个操作数从总线直接送到ALU的另一端,此外,ALU的输出端也不能直接与总线相连,否则其输出会直接通过总线反馈到输入端,影响运算结果,且该数据不能存放在通用寄存器中,否则会破坏其原有内容,因此可以设置一个暂存器Z放置在ALU的输出端,Z可以改造为移位器(T):对操作数或运算结果进行移位运算,暂存寄存器对应用程序员是透明的;

5.计数器(CT):控制乘除运算的操作步数;

作用:指挥各部件协调进行工作,控制器的工作原理是,根据指令操作码、指令的执行步骤(微命令序列)和条件信号来形成当前计算机各部件要用到的控制信号。计算机整机各硬件系统在这些控制信号的控制下协同运行,产生预期的执行结果。

1.控制单元(CU):分析指令并发出各种微操作命令序列;

(1)指令译码器(ID):对指令的操作码进行译码;

(2)时序系统(节拍发生器):信号来自机器主频(CLK);

(3)微操作信号发生器:将操作码转换为微操作;

(4)Reset(R):重置信号;

2.程序计数器(PC):存放下一条执行的指令地址;

3.指令寄存器(IR):存放当前执行的指令;

4.存储器地址寄存器(MAR):存放访存地址,由虚拟地址空间大小决定;

5.存储器数据寄存器(MDR):暂存要从存储器读或者写的信息;

注:步骤标记(标志)来自PSW;

注意以下几点:

- 汇编程序员可见的寄存器有基址寄存器(用于实现多道程序设计,或者编制浮动程序)和状态/标志寄存器、程序计数器PC及通用寄存器组。

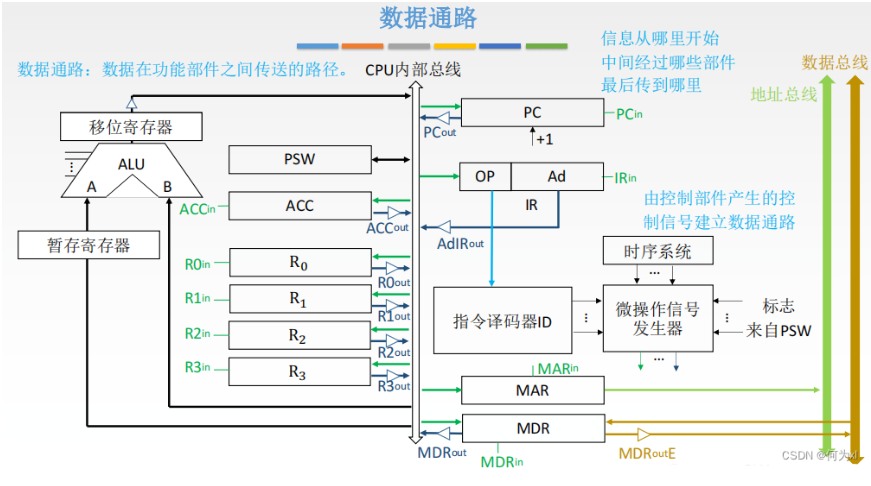

- 数据通路的功能是实现CPU内部的运算器和寄存器以及寄存器之间的数据交换,ALU、通用寄存器、状态寄存器、Cache、浮点运算逻辑、异常和中断处理逻辑等,都是指令执行过程中数据流经的部件,都属于数据通路的一部分。数据通路中的数据流动路径由控制部件控制,控制部件根据每条指令功能的不同,生成对数据通路的控制信号。结构如下图:

- 组合逻辑元件(操作元件):不含存储信号的记忆单元,任何时刻产生的输出仅取决于当前的输入,加法器、算术逻辑单元(ALU)、译码器、多路选择器、三态门等都属于操作元件;时序逻辑元件(状态元件):包含存储记忆单元,各类寄存器和存储器,如通用寄存器组、程序计数器、状态/移位/暂存/锁存寄存器等,都属于状态元件。

作用:存放程序和数据;

作用:存放程序和数据;

1.存储体:存储信息的主体,可由多片芯片组合而成,每篇芯片上是由存储元件组成的存储单元,一个存储单元存放一个存储字长的数据,通常为8bit的整数倍;

2.读写电路:控制读写;

1)控制电路:其中时序系统产生存储器操作所需的各种时序信号,由统一时钟(Clock)分频得到,输入信号线为片选线、读写控制线;

2)读写数据线:地址线用以输入地址、数据线用以输出数据;

3.译码驱动

1)地址译码器:对输入地址信号进行译码;

2)驱动器:驱动主存,以进行读写;

4.数据缓冲器:临时存放输出数据;

作用:介于CPU和内存之间,是CPU和RAM之间的桥梁,用于解决它们之间的速度冲突问题。给出一个地址,先查询其是否存储在Cache中,查询速度较快,如果不在Cache中,再去主存中查询,这样的话,如果一个数据或者一组数据常用,可以减少查询时间。

每个Cache块中包含有效位、脏位、替换控制位、标记位、数据。

作用:速度相较于主存更慢,帮助主存记忆更多信息。主要包括磁盘、SSD等。

1.输入设备:将程序和数据以机器所能识别和接受的信息形式输入计算机;

2.输出设备:将计算机处理的结果以人们所能接受的形式或其他系统所要求的信息形式输出;

1.地址总线:传送的是从CPU等主设备发往从设备的地址信号。

2.控制总线:传送的是一个部件对另一个部件的控制或状态信息,如CPU对存储器的读、写控制信号等。

3.数据总线:传送的是各部件之间交换的数据信息,数据总线通常是双向的。

写在后面

这个专栏主要是我在学习408真题的过程中总结的一些笔记,因为我学的也很一般,如果有错误和不足之处,还望大家在评论区指出。希望能给大家的学习带来一点帮助,共同进步!!!

参考资料

[1]王道408教材(2025版)

[2]王道课程资料

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/bian-cheng-ri-ji/73060.html