我们的板子一直很卡,在后面做内存测试的时候,才发现只有约400M,一G的内存没有真正体现

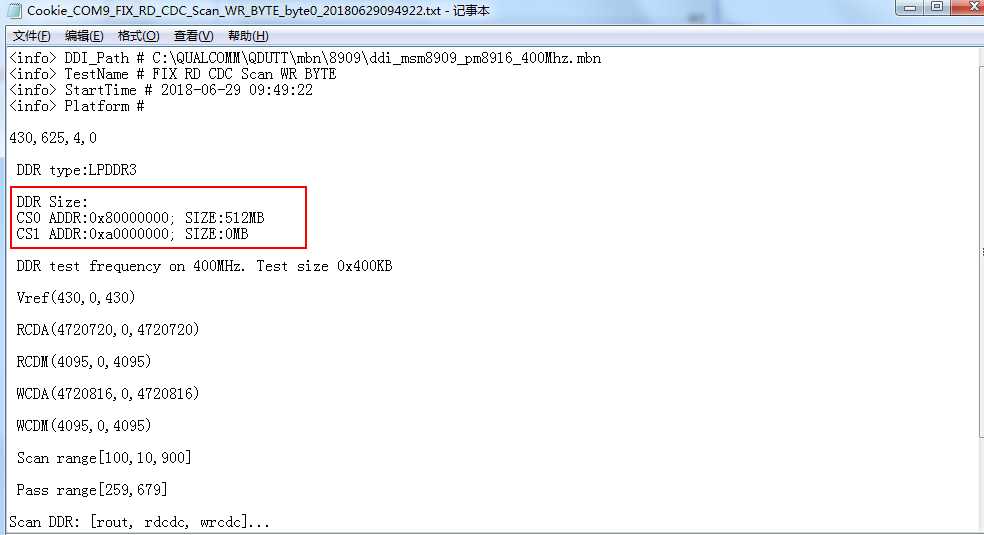

叫硬件用qdutt检测一下,发现只有一个片选

DDR的大小初始化为sbl1_ddr_init,获取大小的地方为:

/*!

* @brief

* Returns the ddr size and base address

*

* @details

*

*

* @param None

*

* @par Dependencies

* None

*

* @par Side Effects

* None

*

* @retval ddr_size_infor contains the ddr size and base address

*

* @sa None

*/

ddr_size_info ddr_get_size(void)

{

ddr_info ddr_physical_info = ddr_get_info();

/* Check to see if interleave is turned on for CS0 */

if(ddr_physical_info.interleaved_memory & SDRAM_CS0)

{

/* Interleave mode is on for CS0 , double the size of CS0, and do not populate interface 1 */

ddr_physical_info.ddr_size.sdram0_cs0 *= 2;

ddr_physical_info.ddr_size.sdram1_cs0 = 0;

}

if(ddr_physical_info.interleaved_memory & SDRAM_CS1)

{

/* Interleave mode is on for CS1 , double the size of CS1, and do not populate interface 1 */

ddr_physical_info.ddr_size.sdram0_cs1 *= 2;

ddr_physical_info.ddr_size.sdram1_cs1 = 0;

}

return ddr_physical_info.ddr_size;

https://blog.csdn.net/js_wawayu/article/details/52089972

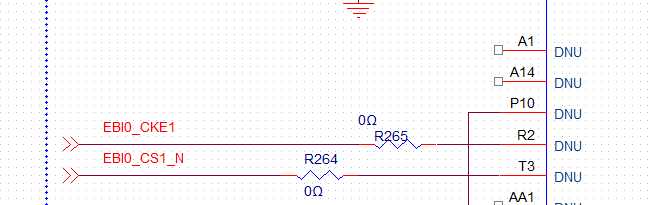

后面发现是硬件片选没接,cs1 cke1没接

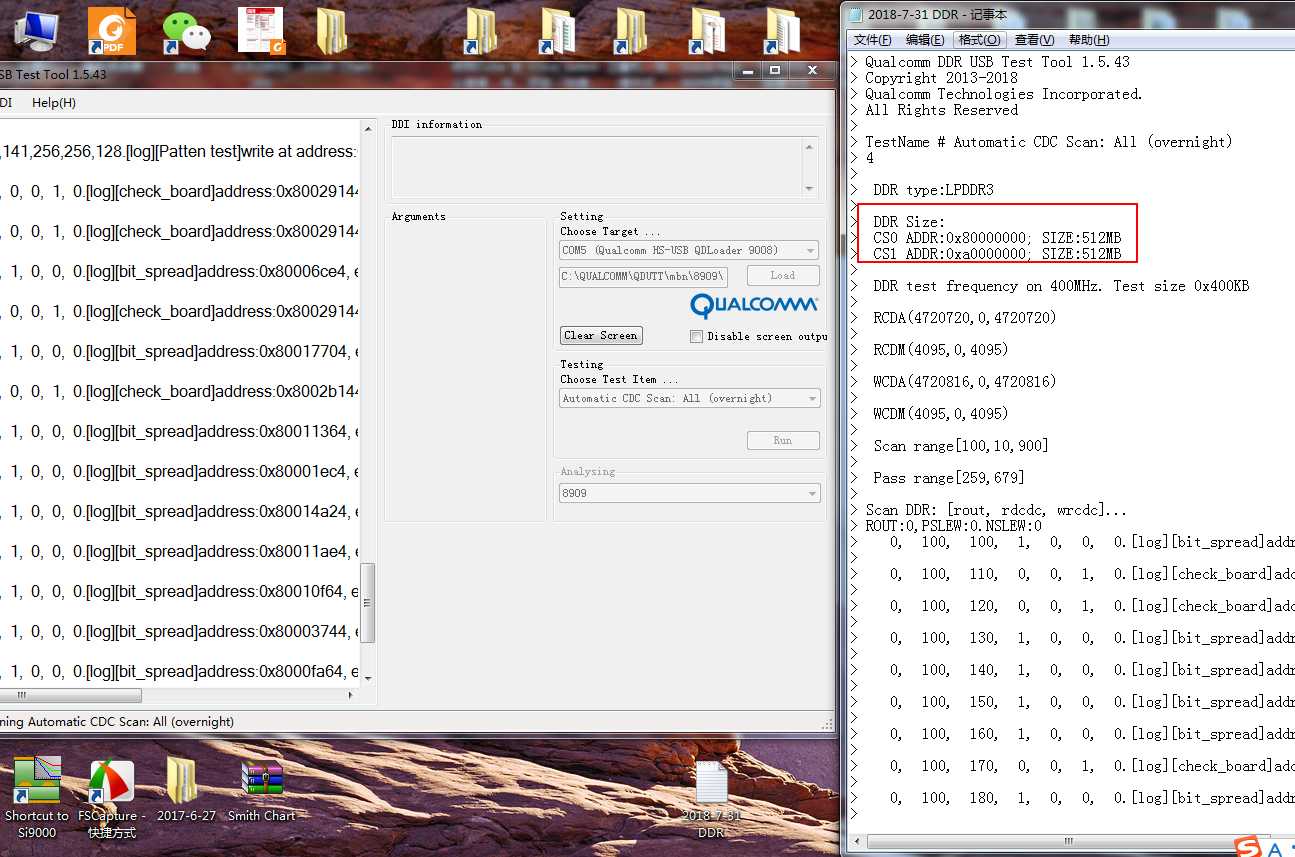

接上之后用qdutt检测到两片都是512m

修改之后发现软件启动不了,找不到dtb

[5830] Kernel image not patched..Unable to locate dt offset[5860] DTB offset is incorrect, kernel image does not have appended DTB

后面发现是dts对应有一个memory的标记,修改一下这个就可以了

qcom,board-id= <8 0x04>;

这个可由打印得出

[5860] DTB offset is incorrect, kernel image does not have appended DTB

[5870] Device info 0x00000109/00020000/0x04010008/4, pmic 0x2000b/0x0/0x0/0x0

在lk下面这个函数里添加打印调试就可以发现问题所在

static int platform_dt_absolute_match(struct dt_entry *cur_dt_entry, struct dt_entry_node *dt_list)

----

/* Determine the bits 10:8 to check the DT with the DDR Size */

cur_dt_hlos_ddr = (cur_dt_entry->board_hw_subtype & 0x700);

内存测试

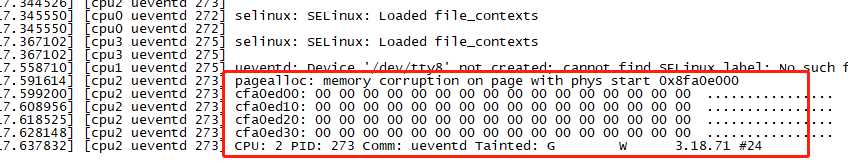

我们一块三星的emcp上用533M跑起来总是挂掉,现在降到100M可以跑一段时间,说明是硬件问题,硬件也说存在pdn仿真有问题,故此降频的方法可以验证是硬件问题

每次都是有如下类似打印

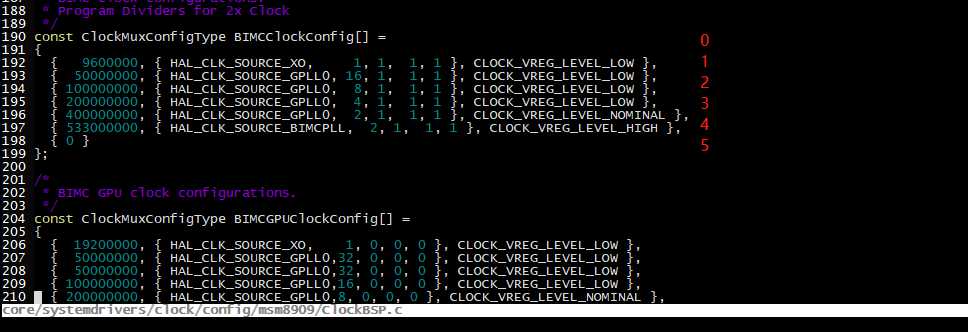

内存降频

amss_8909/rpm_proc$ vi core/systemdrivers/clock/config/msm8909/ClockBSP.c

ClockMuxConfigType BIMCClockConfig[] = { { 9600000, { HAL_CLK_SOURCE_XO, 1, 1, 1, 1 }, CLOCK_VREG_LEVEL_LOW }, // Index = 0 { 37500000, { HAL_CLK_SOURCE_GPLL0, 16, 1, 1, 1 }, CLOCK_VREG_LEVEL_LOW }, // Index = 1 { 50000000, { HAL_CLK_SOURCE_GPLL0, 12, 1, 1, 1 }, CLOCK_VREG_LEVEL_LOW }, // Index = 2 { 100000000, { HAL_CLK_SOURCE_GPLL0, 6, 1, 1, 1 }, CLOCK_VREG_LEVEL_LOW }, // Index = 3 { 200000000, { HAL_CLK_SOURCE_GPLL2, 4, 1, 1, 1 }, CLOCK_VREG_LEVEL_LOW, 0, CHIPINFO_FAMILY_MSM8x26 }, // Index = 4 { 225000000, { HAL_CLK_SOURCE_GPLL2, 4, 1, 1, 1 }, CLOCK_VREG_LEVEL_LOW, 0, CHIPINFO_FAMILY_MSM8926 }, // Index = 5 { 266666667, { HAL_CLK_SOURCE_GPLL3, 4, 1, 1, 1 }, CLOCK_VREG_LEVEL_NOMINAL, 0, CHIPINFO_FAMILY_MSM8x26 }, // Index = 6 { 300000000, { HAL_CLK_SOURCE_GPLL3, 4, 1, 1, 1 }, CLOCK_VREG_LEVEL_NOMINAL, 0, CHIPINFO_FAMILY_MSM8926 }, // Index = 7 { 400000000, { HAL_CLK_SOURCE_GPLL2, 2, 1, 1, 1 }, CLOCK_VREG_LEVEL_NOMINAL, 0, CHIPINFO_FAMILY_MSM8x26 }, // Index = 8 { 450000000, { HAL_CLK_SOURCE_GPLL2, 2, 1, 1, 1 }, CLOCK_VREG_LEVEL_NOMINAL, 0, CHIPINFO_FAMILY_MSM8926 }, // Index = 9 { 533333333, { HAL_CLK_SOURCE_GPLL3, 2, 1, 1, 1 }, CLOCK_VREG_LEVEL_HIGH, 0, CHIPINFO_FAMILY_MSM8x26 }, // Index = 10 { 600000000, { HAL_CLK_SOURCE_GPLL3, 2, 1, 1, 1 }, CLOCK_VREG_LEVEL_HIGH, 0, CHIPINFO_FAMILY_MSM8926 }, // Index = 11 { 0 } // Index = 12 };

这里为

修改:

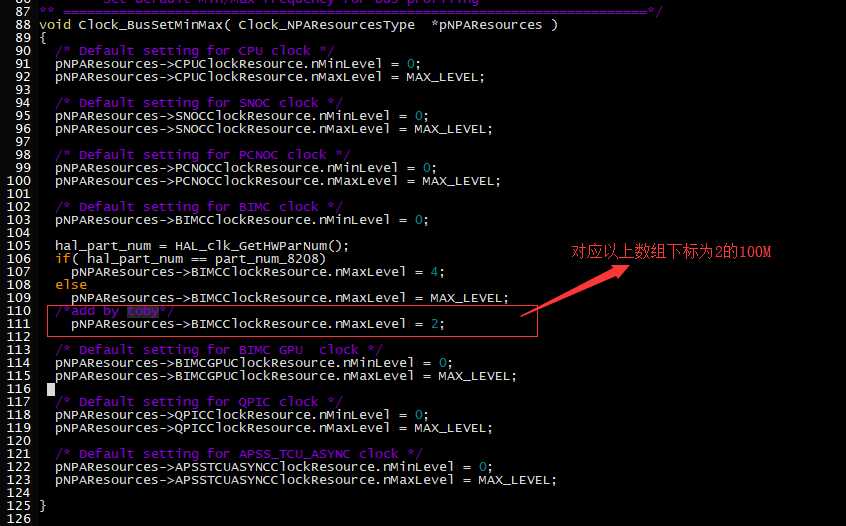

amss_8909/rpm_proc$ vi ./core/systemdrivers/clock/hw/msm8909/ClockRPM.c

/* ========================================================================= ||- macro

** Function : Clock_BusSetMinMax ||| XO_LEVEL

** Set default Min/Max frequency for bus profiling ||| MAX_LEVEL

** =========================================================================*/ ||| QDSS_CLOCK_NU

void Clock_BusSetMinMax( Clock_NPAResourcesType *pNPAResources ) ||

{ ||- typedef

/* Default setting for CPU clock */ ||| ClockVddMinTy

pNPAResources->CPUClockResource.nMinLevel = 0; ||| clock_id_type

pNPAResources->CPUClockResource.nMaxLevel = MAX_LEVEL; ||

||- variable

/* Default setting for SNOC clock */ ||| clk0_adapter

pNPAResources->SNOCClockResource.nMinLevel = 0; ||| clk1_adapter

pNPAResources->SNOCClockResource.nMaxLevel = MAX_LEVEL; ||| clk2_adapter

||| clkVddMin

/* Default setting for PCNOC clock */ ||| qpic_adapter

pNPAResources->PCNOCClockResource.nMinLevel = 0; ||| part_num_8208

pNPAResources->PCNOCClockResource.nMaxLevel = MAX_LEVEL; ||| hal_part_num

||| snoc_curr_vot

/* Default setting for BIMC clock */ ||

pNPAResources->BIMCClockResource.nMinLevel = 0; ||- function

||| Clock_BusSetM

hal_part_num = HAL_clk_GetHWParNum(); ||| Clock_QDSSCon

if( hal_part_num == part_num_8208) ||| Clock_IsQDSSO

pNPAResources->BIMCClockResource.nMaxLevel = 4; ||| Clock_DetectC

else ||| Clock_SNOCIni

pNPAResources->BIMCClockResource.nMaxLevel = MAX_LEVEL; ||| Clock_SetupSN

/*add by toby*/ 修改的地方 ||| Clock_SetupSY

pNPAResources->BIMCClockResource.nMaxLevel = 2; ||| Clock_DetectR

||| Clock_InitQPI

/* Default setting for BIMC GPU clock */ ||| Clock_ConfigB

pNPAResources->BIMCGPUClockResource.nMinLevel = 0; ||| Clock_InitClk

pNPAResources->BIMCGPUClockResource.nMaxLevel = MAX_LEVEL; ||| Clock_EnableC

||| Clock_InitIma

/* Default setting for QPIC clock */ ||| Clock_Process

pNPAResources->QPICClockResource.nMinLevel = 0; ||| Clock_Process

pNPAResources->QPICClockResource.nMaxLevel = MAX_LEVEL; ||| Clock_GetSubS

||| Clock_Init

/* Default setting for APSS_TCU_ASYNC clock */ |

pNPAResources->APSSTCUASYNCClockResource.nMinLevel = 0; | ~

pNPAResources->APSSTCUASYNCClockResource.nMaxLevel = MAX_LEVEL; | ~

| ~

}

烧录对应的rpm.mbn后查看频率:为100M

msm8909:/ # cat /sys/kernel/debug/clk/bimc_clk/measure

100000018

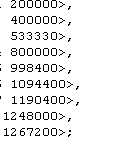

memtester 20M 3

给cpu定频后再测试

cpu 频率测试

adb shell "echo %freq% > /sys/devices/system/cpu/cpu0/cpufreq/scaling_min_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu0/cpufreq/scaling_max_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu1/cpufreq/scaling_min_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu1/cpufreq/scaling_max_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu2/cpufreq/scaling_min_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu2/cpufreq/scaling_max_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu3/cpufreq/scaling_min_freq"

adb shell "echo %freq% > /sys/devices/system/cpu/cpu3/cpufreq/scaling_max_freq"

%freq% 这个换成需要设置的频率 ,

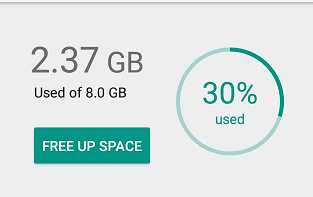

我们客户发现我们的内存大小不对8G大小只有2G,后面发现是需要修改data 分区的大小可以改变:

于是在/data分区修改为5.5GB,可以检测到5.3G接近了

Index: android/device/qcom/msm8909/BoardConfig.mk

===================================================================

--- android/device/qcom/msm8909/BoardConfig.mk (revision 234)

+++ android/device/qcom/msm8909/BoardConfig.mk (revision 235)

@@ -110,7 +110,7 @@

BOARD_BOOTIMAGE_PARTITION_SIZE := 0x02000000

BOARD_RECOVERYIMAGE_PARTITION_SIZE := 0x02000000

BOARD_SYSTEMIMAGE_PARTITION_SIZE := 943718400

-BOARD_USERDATAIMAGE_PARTITION_SIZE := 1659305984

+BOARD_USERDATAIMAGE_PARTITION_SIZE := 5905580032#4294967296#1659305984

BOARD_CACHEIMAGE_PARTITION_SIZE := 115343360

BOARD_PERSISTIMAGE_PARTITION_SIZE := 33554432

BOARD_OEMIMAGE_PARTITION_SIZE := 268435456

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/37885.html