数据通路的基本概念

是CPU内部各执行部件间进行信息传递的路径,通路的建立依赖于各执行部件间的控制信号,比如运算器的运算选择信号加减乘除,寄存器的写入控制信号,主存的读写控制信号,其中有些信号需要靠时钟驱动,由时钟配合才能完成,不同指令在数据通路上是不同的,相同的指令,在指令执行的不同阶段,数据通路也是不相同的。分为共享通路(总线)和专用通路

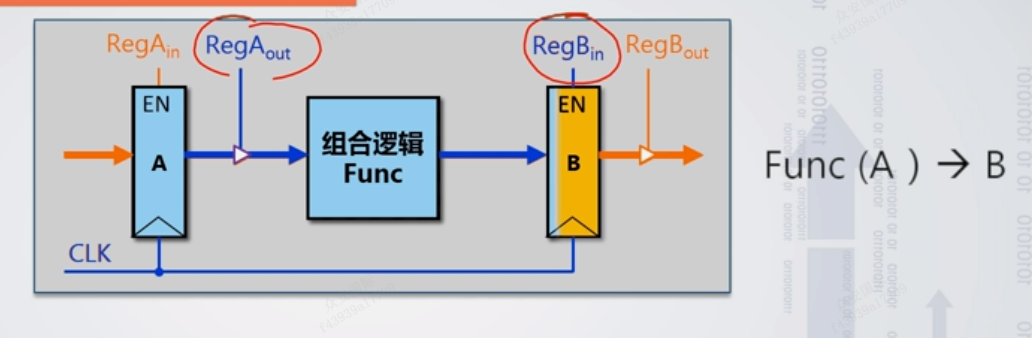

数据通路抽象模型(寄存器传输)

将A的信息传输给B

- 首相将A的信息经过控制信号RegAout(三态门信号),读出送给逻辑组合

- 经过一个逻辑组合的延迟后,传递到寄存器B的输入端

- 要想将数据加载到寄存器B端必须要给出寄存器的写使能信号RegBin,还需要在时钟的配合下完成保存数据

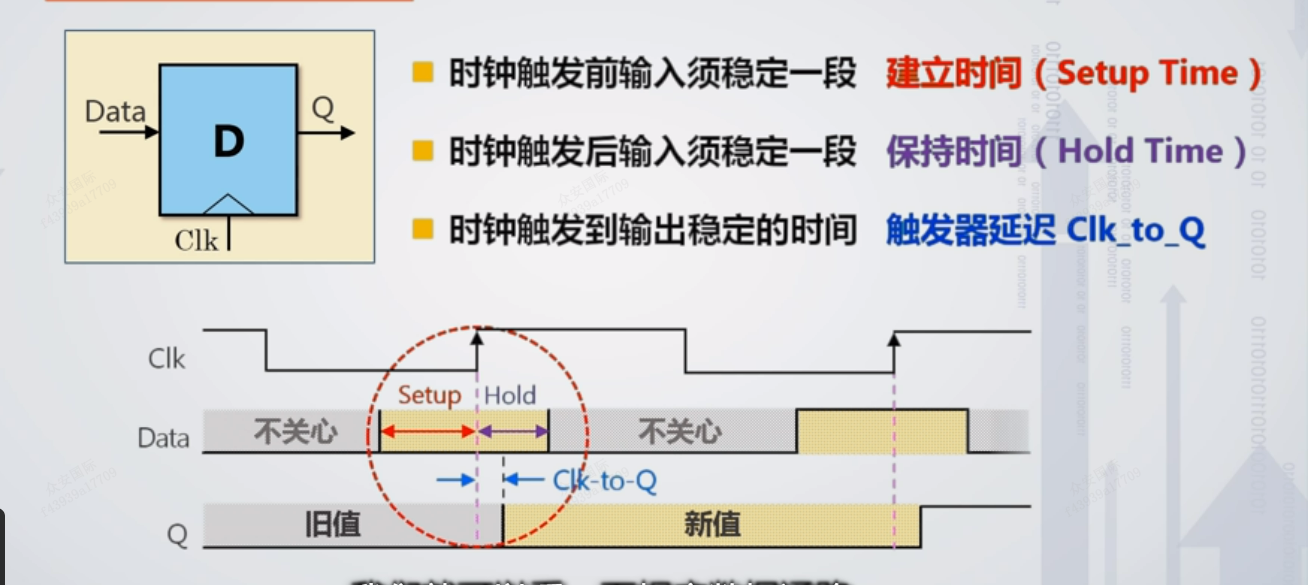

D触发器定时模型

包括一个一位的数据输入Data,一个一位的数据输出Q,Q端能够在时钟到来之前,一直所存一个固定的状态,所以D触发器是一个存储器件,可以存储一位数据。当时钟到来之后,Q值将所存一位新的Data值

时钟触发前输入需稳定一段,建立时间

时钟触发后输入需稳定一段时间,保持时间

这两个叠加在一起成为数据的稳定时间

时钟触发到输出稳定的时间触发器延迟时间

这个时间Q值将更新为Data的新值

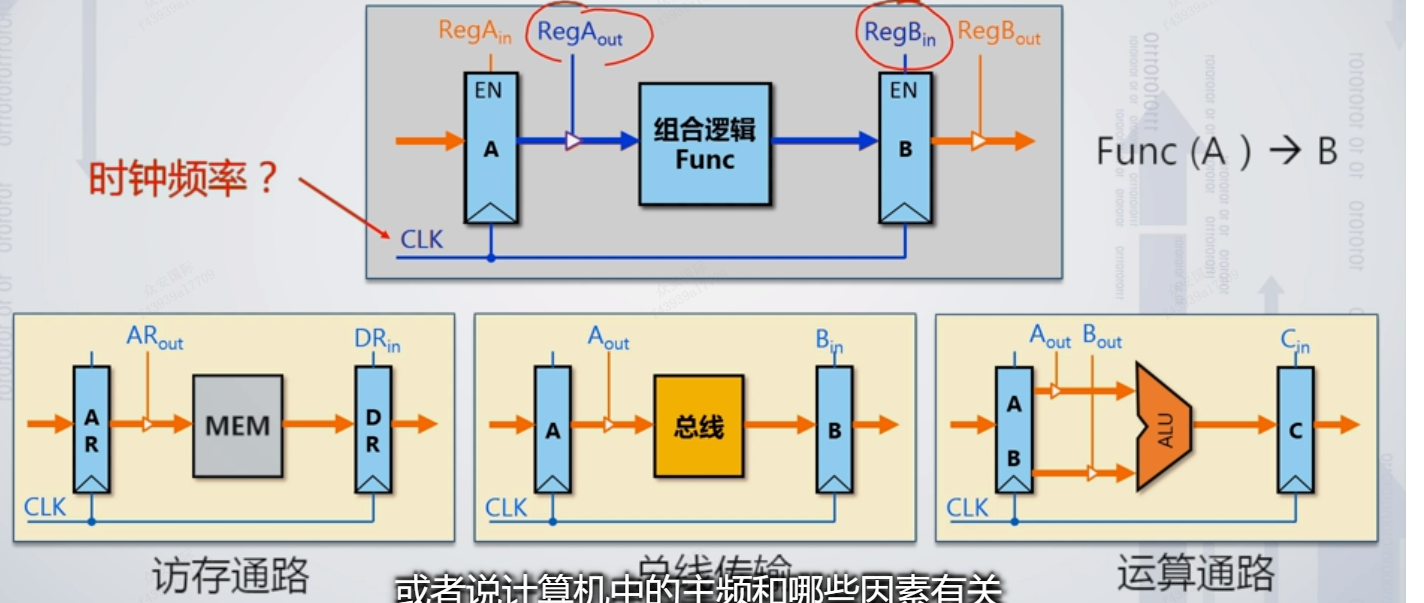

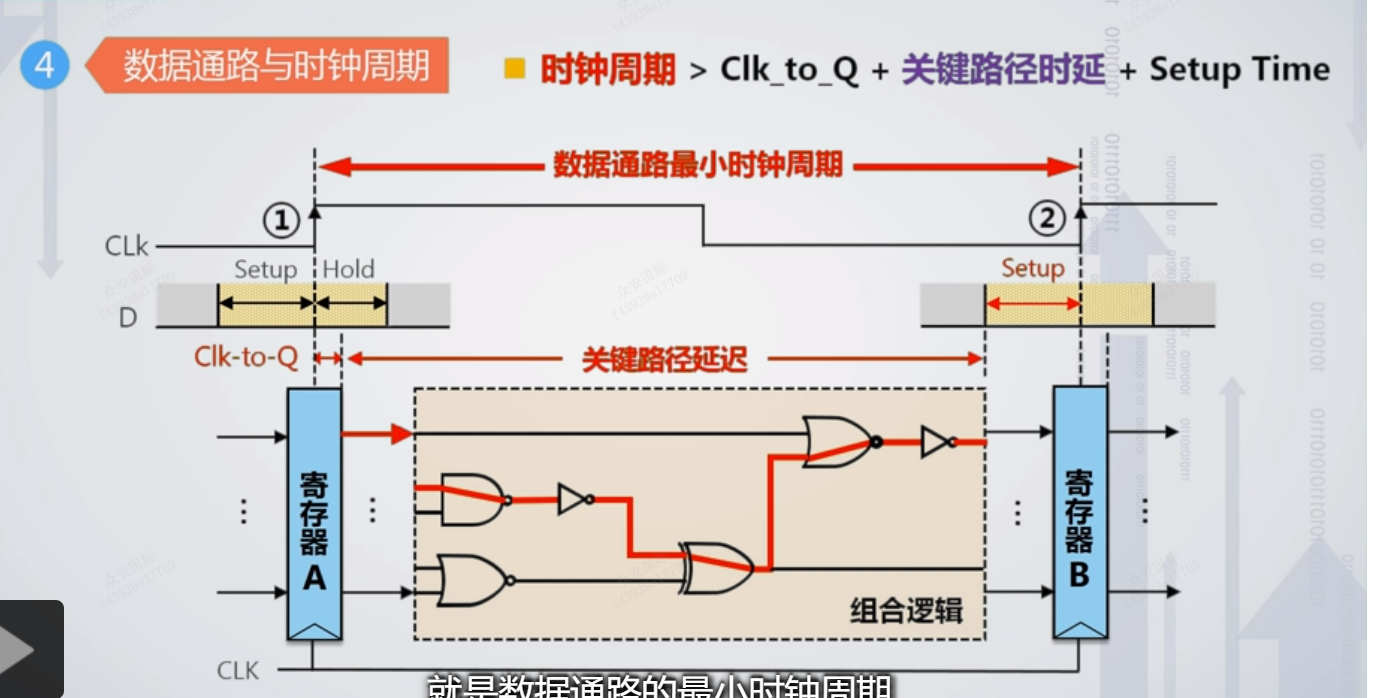

数据通路与时钟周期之间关系

- 当第一个时钟周期到来之前,寄存器A进行数据锁存,寄存器A也必须满足前面讲到的定时机制,先必须稳定一个建立时间,然后稳定一个保持时间

- 当时钟上跳沿到来之后,经历一个触发器延迟时间,寄存器A的新值将会传输到组合逻辑的输入端,由于对应的输入在这里发生了变化,所以经过组合逻辑最终会反应在寄存器B的输入端

- 经过一个关键路径延迟,寄存器B端所有数据都会更新为新值

- 要想将新值稳定的所存在寄存器B端,必须让新值也稳定一个建立时间,才能够在第二个时钟周期到来的时候将对应的数据所存在B端

- 1和2的时间间隔就是数据通路的最小时钟周期,包括触发器延迟时间CLK-to-Q,组合逻辑的关键路径延迟,寄存器B的数据建立时间

- 要想优化数据传输通路的频率,所以最主要优化关键路径延迟

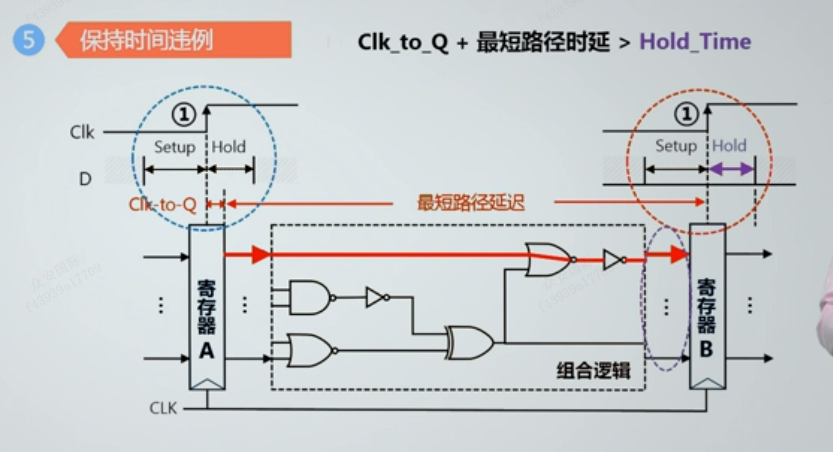

保持时间违例

今天的文章6.2-数据通路_数据通路分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/51248.html