今天来学习一下滑动缓冲器。

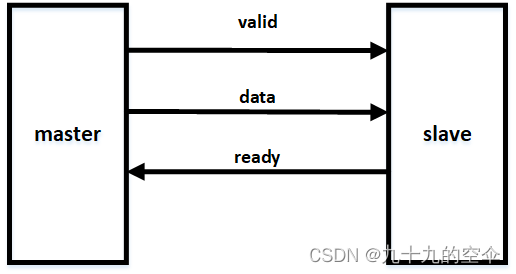

在总线协议中,反馈握手信号是很常见的。最典型的就是axi总线中的valid-ready信号对。

有数据要发送时,master就将valid拉高, 如果slave可以接收数据,则将ready信号也拉高,因此数据在valid=1且ready=1的时候完成一次传输。

如果slave暂无法接收数据,就将ready拉低,这时若master如果拉高了valid,那么需要保持valid和data的数据不变,直到ready信号拉高。

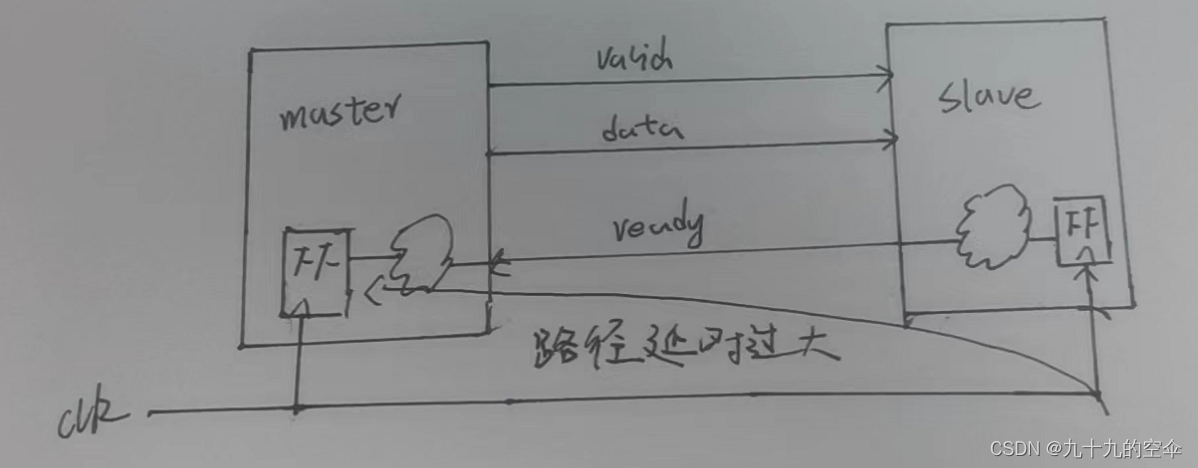

在这个方案下,可能会产生一个问题,如果ready信号出现时序违例了怎么办?

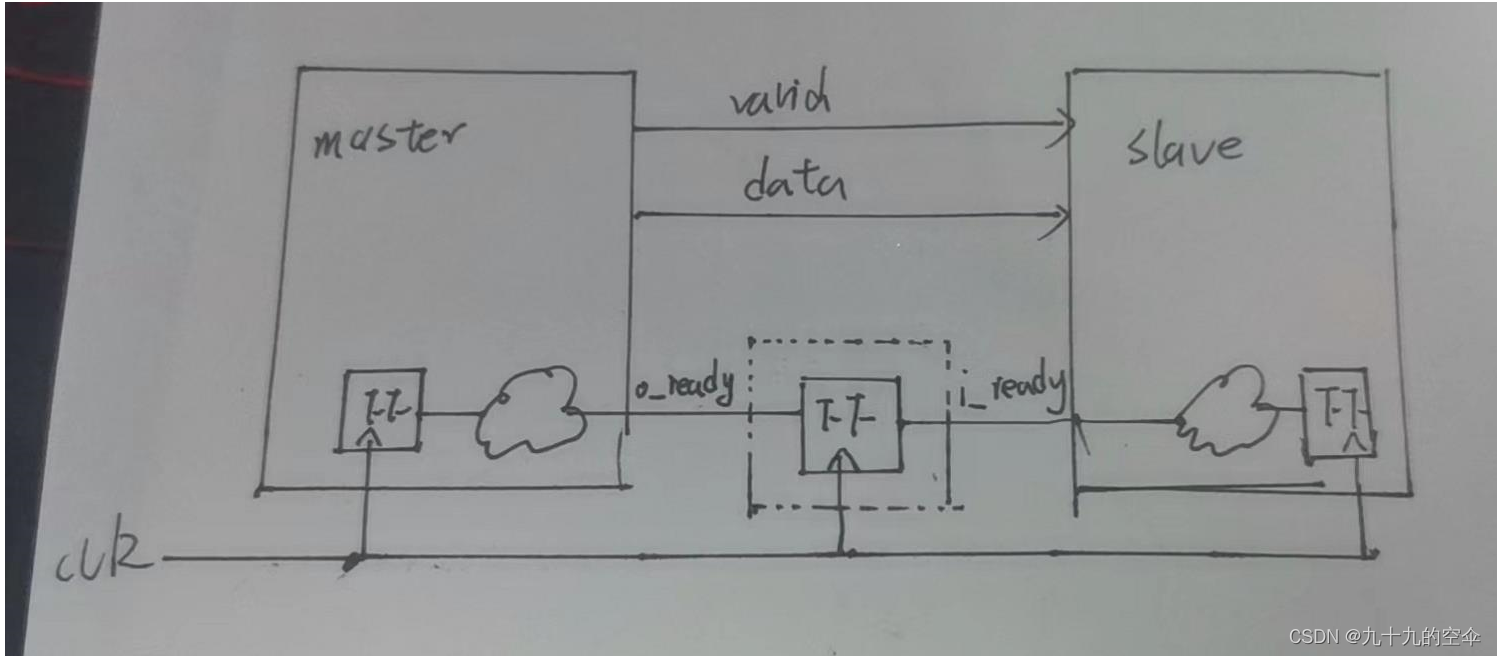

最常见的方法是在ready路径中加一级寄存器,将其组合逻辑隔断。

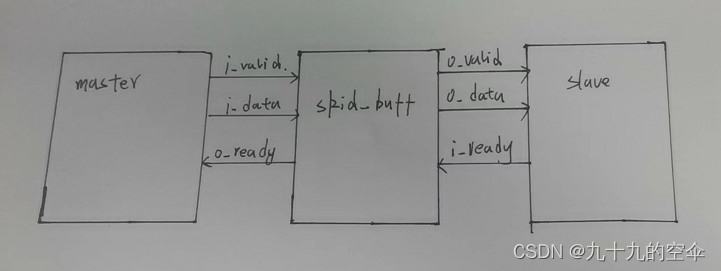

这样子我们就产生了两个ready信号,一个是slave输出的信号i_ready,一个是打一拍后给到master的信号o_ready。

这种做法造成的最直接后果就是master接收slave的ready信号会晚一拍,进而会引发至少两个问题。

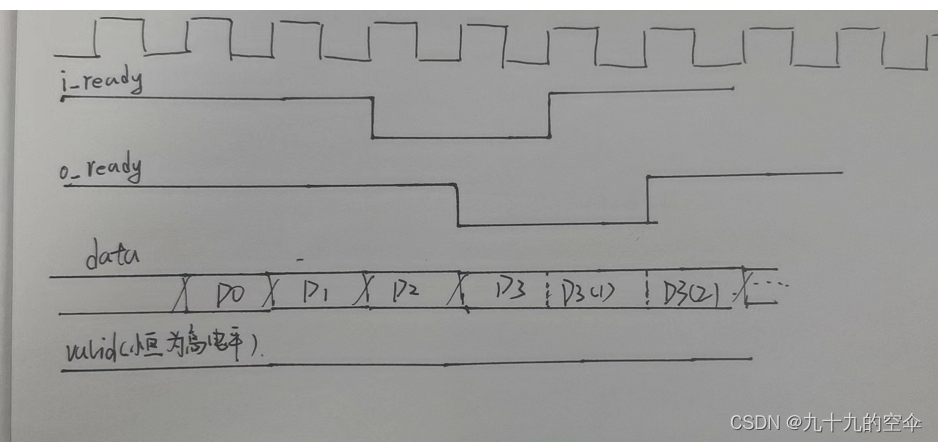

对于master端而言,它只能看见o_ready,因此输出的data也是跟着o_ready来的,o_ready为低时,保持当前数据D3不变,直到o_ready拉高。

但数据传到slave后,和slave端真正的ready信号(即i_ready)产生错位。

①D2数据时,i_ready为低,因此该D2数据被slave所忽略。

②D3数据持续了三个周期,后两个周期时,i_ready都为高,因此D3数据传输了两次,即图中D3(1)、D3(2)。

那么这是个功能上的错误,解决的方法就是skid_buffer。核心思想就是在D2时刻,将数据保存到skid buffer的一个内部寄存器中,然后在i_ready拉高后的第一个周期输出,顶替图中D3(1)的周期,这样子可以使数据D2不丢失同时避免了传输两次D3的现象。

moudle skid_buff(

input clk,

input rstn,

//master to skid_buff

input i_valid,

input [63:0] i_data,

output o_ready,

//skid_buff to slave

output o_valid,

output [63:0] o_data,

input i_ready

);

reg[63:0] r_data;

reg r_valid;

always @ (posedge clk or negedge rstn)begin

if(!rstn)

r_valid <= 'b0;

else if (i_valid && (!i_ready))

r_valid <= 1'b1;

else if (i_ready)

r_valid <= 1'b0;

end

always @ (posedge clk or negedge rstn)begin

if(!rstn)

r_data <= 'b0;

else if (i_valid && (!i_ready) && (!r_valid))

r_data <= i_data;

end

assign o_data = (r_valid)?r_data:i_data;

assign o_valid = r_valid | i_valid;

endmodule可以看到在内部我们首先对i_ready进行了一次打拍,然后声明了一个内部的r_data用来暂存数据,并声明了一个r_valid用来只是r_data是否暂存了数据。该模块主要的逻辑如下:

①如果master传输了一个数据(i_valid),但是slave的i_ready为0,则将数据暂存,防止丢失。同时拉高r_valid,说明内部寄存器已经暂存了一个来自master的数据。

②如果i_ready拉高,那么首先要将r_data的数据输出,这时由于内部寄存器的数据已经输出,那么需要拉低r_valid。

③如果内部寄存器有数据,或者master有数据要发送,那么slave都将收到来自skid buff的valid信号。同时内部寄存器的数据是要永远优先于master的数据发送的。

今天的文章skid buffer分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/60483.html