VHDL实现全加器

1.一位全加器

全加器是能够计算低位进位的二进制加法电路,一位全加器(FA)的逻辑表达式为:

F=A⊕B⊕Ci

Co=Ci(A⊕B)+AB

其中A,B为要相加的数,Ci为进位输入;F为和,Co是进位输出

真值表如下:

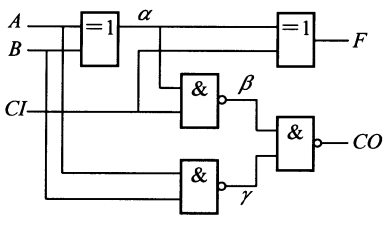

原理图如下:

因此在设计实体时,选定三输入二输出:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED;

ENTITY homework5 IS

PORT(

a,b,ci:IN STD_LOGIC;

f,co:OUT STD_LOGIC

);

END homework5;

ARCHITECTURE yejiayu OF homework5 IS

BEGIN

f<=(a XOR b)XOR ci; --F=A⊕B⊕Ci

co<=((a XOR b)AND ci)OR(a AND b); --Co=Ci(A⊕B)+AB

END yejiayu;

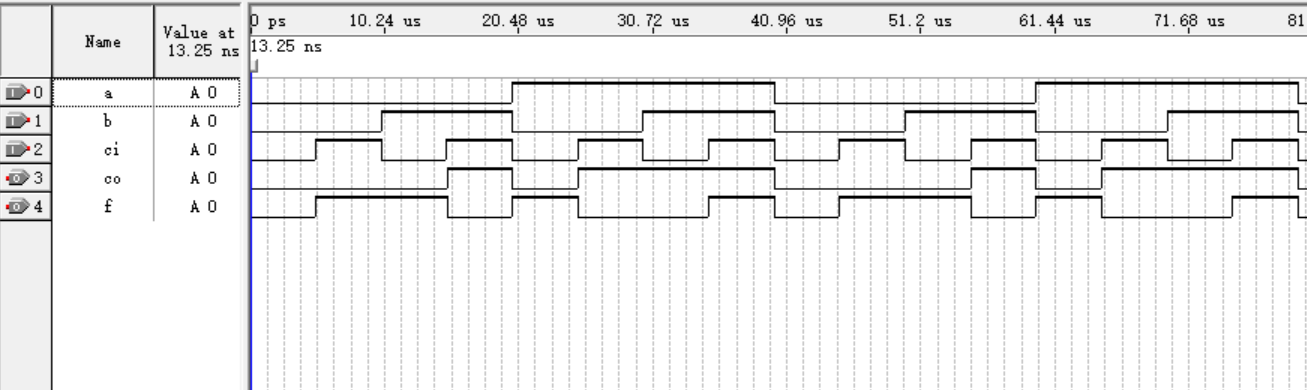

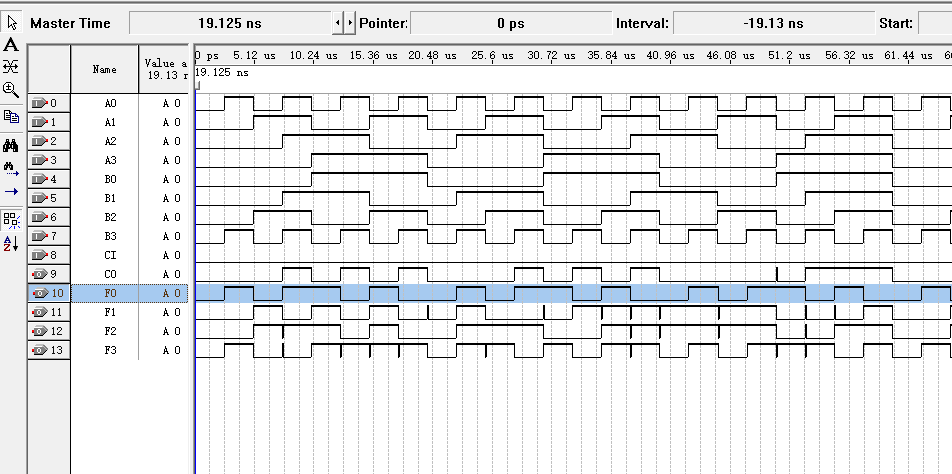

保存编译后仿真如下:

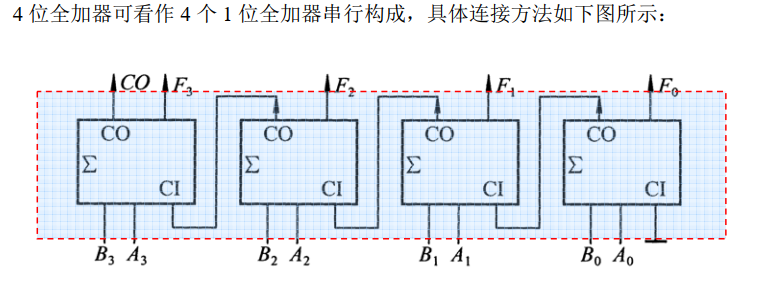

2.四位全加器

(1)元件例化方法实现:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY homework6 IS

PORT(

A0,A1,A2,A3,B0,B1,B2,B3:IN STD_LOGIC;

F0,F1,F2,F3:OUT STD_LOGIC;

CI:IN STD_LOGIC;

CO:OUT STD_LOGIC

);

END homework6;

ARCHITECTURE yejiayu OF homework6 IS

COMPONENT homework5 --COMPONENT语句来实现元件例化方法

PORT(

a,b,ci:IN STD_LOGIC;

f,co:OUT STD_LOGIC

);

END COMPONENT homework5;

SIGNAL S0,S1,S2:STD_LOGIC;

BEGIN

U1:homework5 port map(A0,B0,CI,F0,S0);

U2:homework5 port map(A1,B1,S0,F1,S1);

U3:homework5 port map(A2,B2,S1,F2,S2);

U4:homework5 port map(A3,B3,S2,F3,CO);

END yejiayu;

其中的homework5为上方一位全加器的实体文件

(接下来注意!!!)

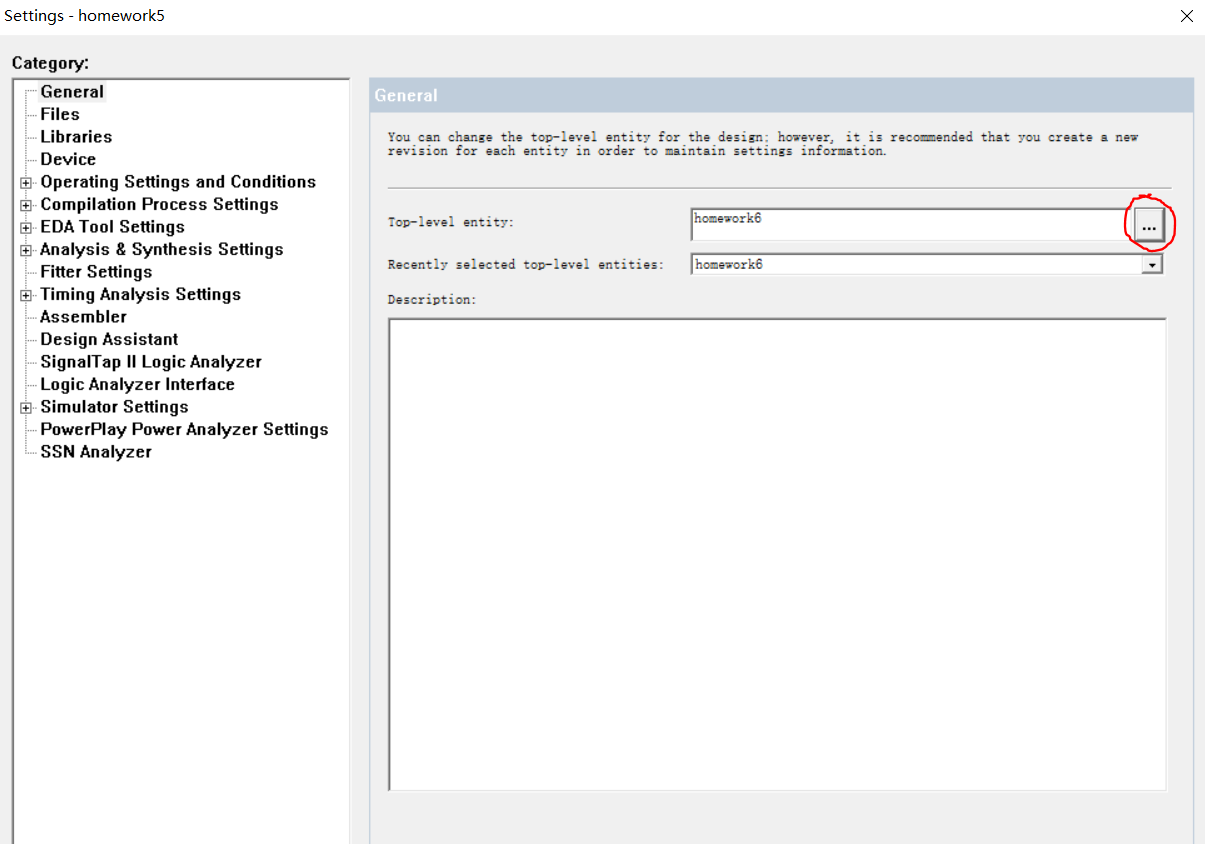

首先,打开quratusII点击打开homework5文件

接着新建VHDL文件,写入四位全加器代码,保存至同一文件夹(必须在同一文件夹!!!)

接着在编译前点击settings按钮改变顺序(不然编译的是homework5当时我就倒在了这里)

选择homework6

再进行编译仿真

(2)简化实现四位全加器

通过调用 STD_LOGIC_UNSIGNED 包中的“+”号方法设计一个4位全加器

代码如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY homework7 IS

PORT(

A,B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

F:OUT STD_LOGIC_VECTOR(4 DOWNTO 0));

END homework7;

ARCHITECTURE yejiayu OF homework7 IS

BEGIN

PROCESS(A,B)

BEGIN

F<="00000"+A+B;

END PROCESS;

END yejiayu;

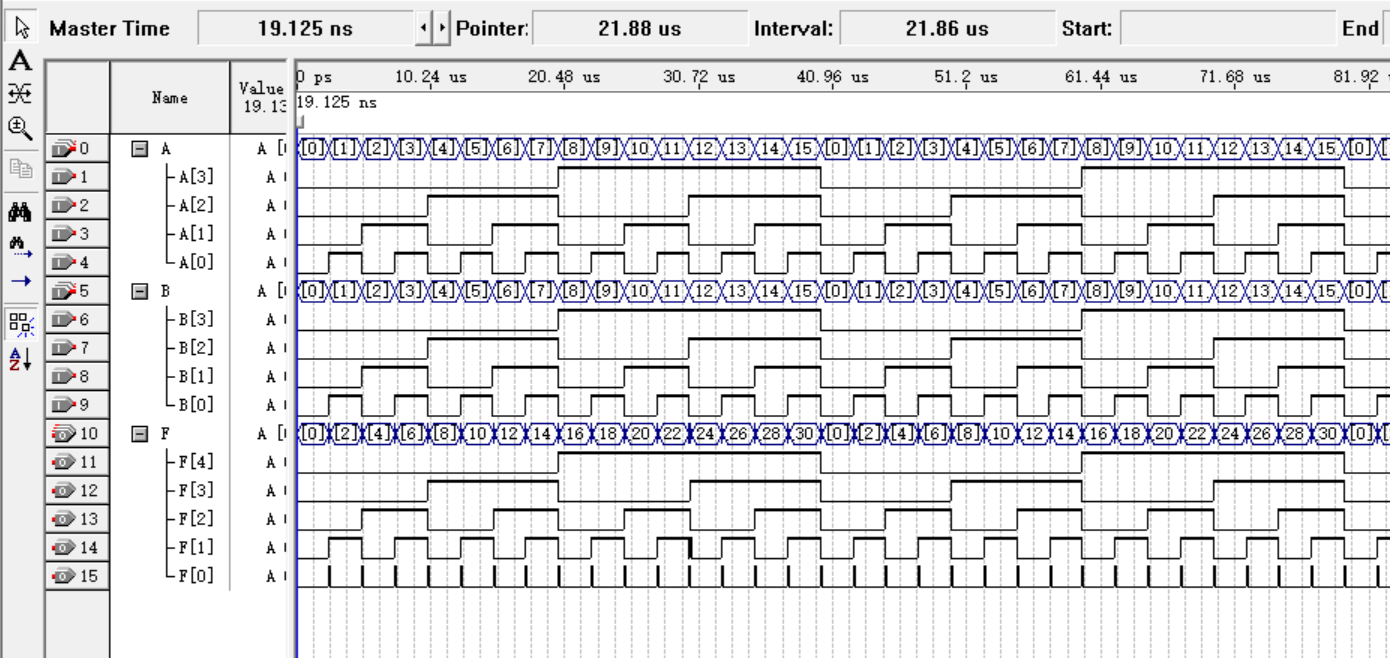

编译仿真:

ᵎ(•̀㉨•́)و ̑̑ 加油

今天的文章VHDL实现全加器分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/7366.html