一.基础概念

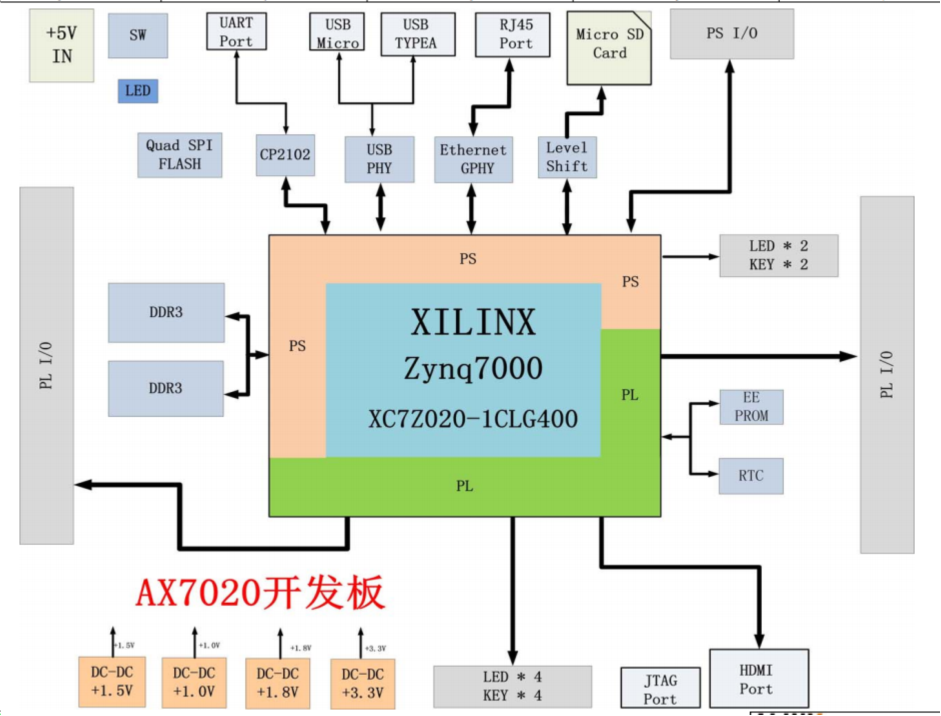

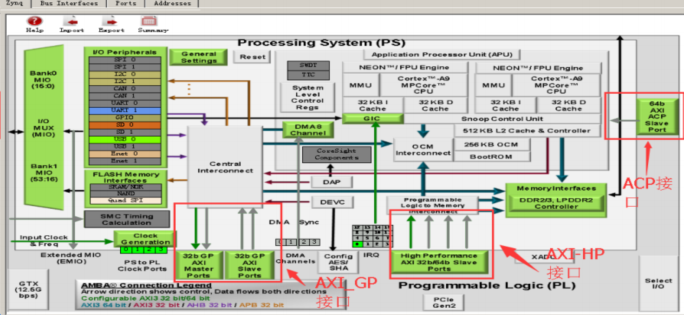

AX7020 包含两大部分ps(集成两个ARM cortex-a9处理器),和pL(FPGA)

PS:主频 1GHZ,256KB片内RAM,8Gbit SDRAM(以太网, 串口, usb, spi flash,SD,IO,LED,KEY)

PL:可编程逻辑块,可编程IO块等(eeprom RTC HDMI LED KEY ADC)

互联:

PS内和PS到PL高宽带连接

基于ARM AMBA AXI总线

传输质量控制和带宽控制

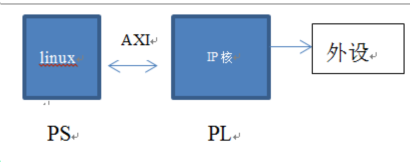

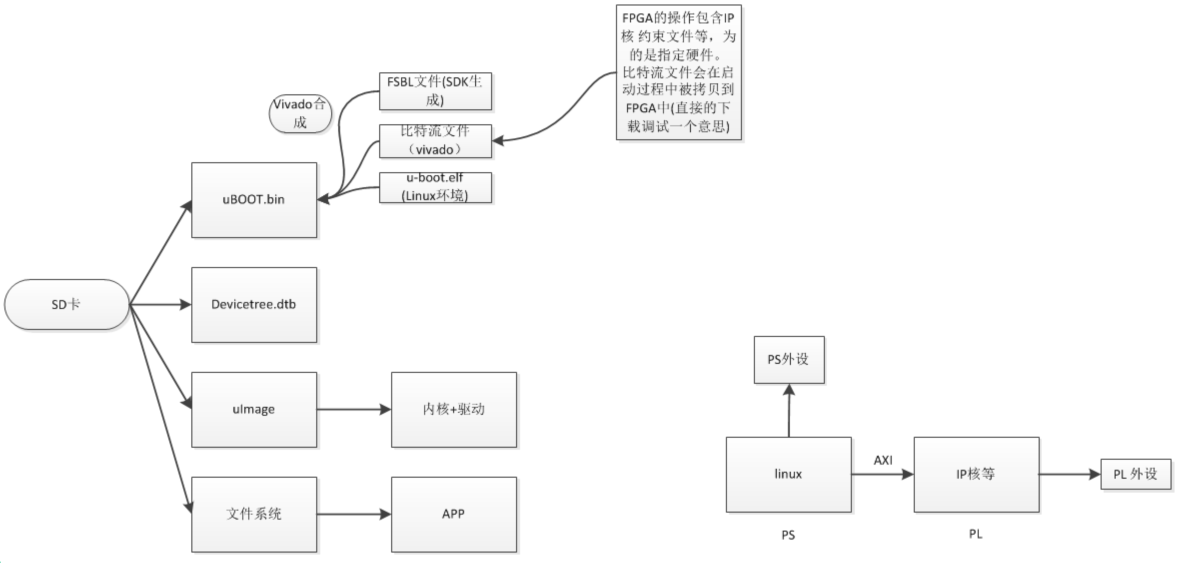

上图很明确的标出了硬件接口,不同的部分需要通过不同开发手段开发。

1.环境搭建

(1)Xilinux FPGA开发环境 Vivado

(2)linux环境搭建 (工具链和linux版本需要注意)

FPGA编程

verilog行为描述语言是什么??(fpga开发专用语言??)

芯片上电后,先运行的是ARM系统,然后通过ARM系统软件部分加载FPGA的比特流文件.bit至FPGA,启动FPGA逻辑功能。

vivado可用于FPGA逻辑编写和ARM裸机的编写(集成SDK)

二.开始学习

在之前接触的芯片中,要不只需要linux开发的ARM,或者是FPGA芯片。像这种集成两部分的芯片还是第一次遇到,所以在学习的过程中,一会linux编程,一会fpga编程,他们之前怎么配合

也是整的迷迷糊糊。

其实这个芯片和我们平时的应用也是很相似的,3500方案既包括arm linux部分也包括单片机部分,他们自己通过不同的软件和方法编写自己的,然后通过通讯接口进行数据交互,这个芯片

道理也是一样的,在这款芯片的学习中,设计到许多之前没接触过的名词和工具,接下来快速引入。

|

开发工具 |

说明 |

|

Xilinx Vivado |

Vivado设计套件实现FPGA部分的设计和开发,管脚和时序的约束,编译和仿真,实现RTL到比特流的设计流程 |

|

Xilinx SDK(Software Development Kit) |

SDK是Xilinx软件开发套件(SDK),在Vivado硬件系统的基础上,系统会自动配置一些重要参数,其中包括工具和库路径、编译器选顷、JTAG和闪存设置,调试器连接已经裸机板支持包(BSP) |

|

交叉编译工具(linux虚拟机 工具链) |

要在x86的体系的主机上编译出可以在ARM体系结构中运行的可执行文件,必项要用交叉编译工具链来完成 |

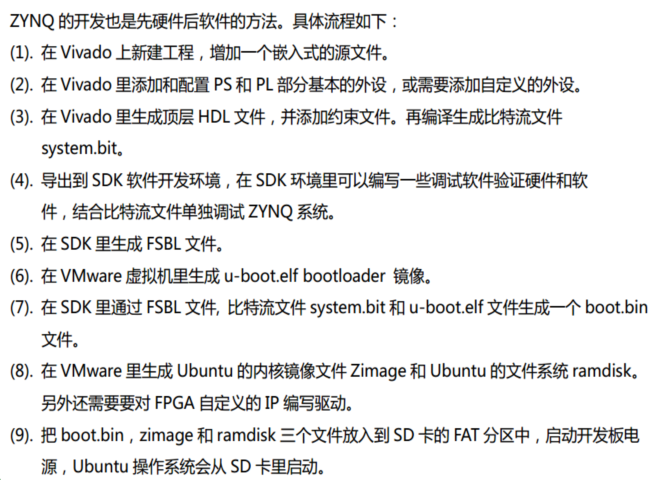

1.ZYNQ芯片开发流程

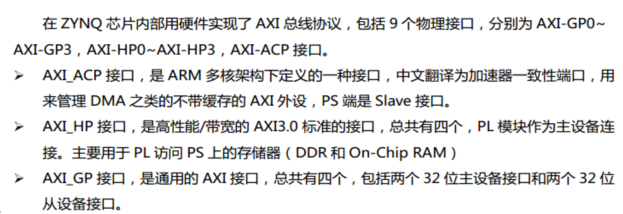

PS和PL连接,加入IP核后,系统自动使用AXI接口将我们的IP核与处理器连接起来。

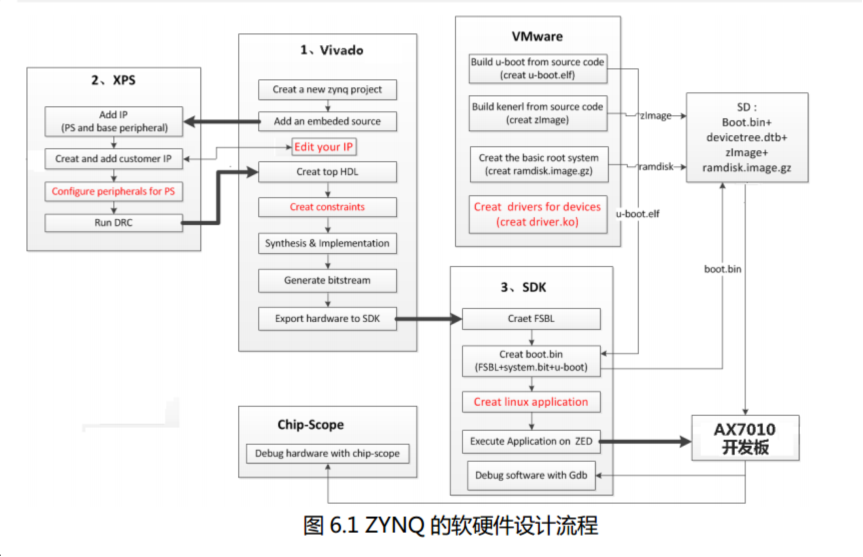

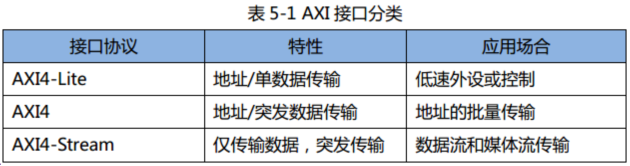

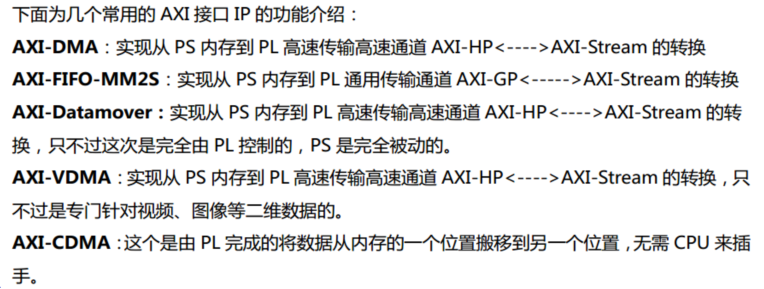

AXI接口

一种接口协议,主要描述主设备和从设备之间的数据传输方式

位于PS端的ARM直接有硬件支持AXI接口,而PL则需要使用逻辑实现相应的AXI协议。Xlinx在Vivado开发环境里提供现成的IP

如 AXI-DMA AXI_GPIO 等,使用的时候直接从IP列表中添加即可。

上电有要求?为什么,怎么做到上电顺序。。。

开启一个电源然后用这个当做使能脚,来使能下一路电源。上电顺序有要求应该和板卡部分器件特性有关。

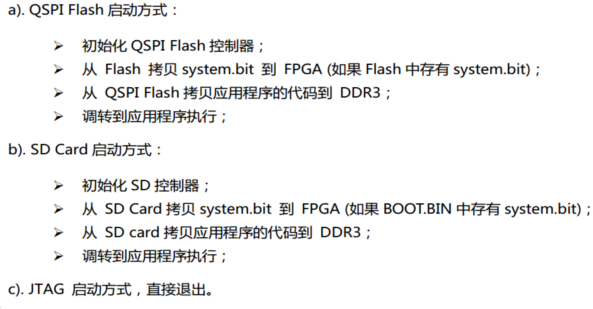

AX7020 开发板支持三种启动模式

1.JTAG 调试模式

2.QSPI flash

3.sd 卡启动模式

PS时钟源:33.333MHZ(有源)

PL时钟源:50MHZ(有源)

举例应该是最快理解流程的最好方式:

PS端控制 PL端的灯

添加AXI GPIO的IP 用于与PS通讯

PL部分需要加约束文件来告诉连在哪个管脚上

生成FPGA的比特流文件,导出SDK

在SDK里面建立工程

在我们的stm32芯片中,一个管脚也支持很多个功能,普通IO功能或者spi等其他功能,通过配置然后调用不同的

文件来实现功能,这里的形式应该是一样的通过调用不同的API函数来调用文件,IP核 sdK等相当于自己配置硬件环境然后

生成出一个SDK,通过API来调用内容。加上linux和加上一个rtos系统调用方式应该是一样的。VIVado生成SDK的过程就相当于

硬件配置的过程并没有什么神秘的。

是否可以理解为PL部分为硬件桥接转化功能(软件IP核编程+约束配置),达到PS控制pL端外设的目的。

开发板启动流程

一.第一阶段

1.上电后首先执行片内boot ROM 代码,boot ROM读取boot mode寄存器来决定是哪种启动方式

2.确定好启动方式后,BOOT ROM从相应的启动设备中加载First Bootloader(FSBL)到RAM,并且将

执行权交给FSBL。

二.第二阶段

FSBL开始执行

1.初始化CPU,初始化串口

2.PS一些控制器的初始化(PLL DDR CLK等)

3.禁止L1 DATA Cache

4.注册ARM中断向量

5.通过Boot mode寄存器,判断是哪种启动方式

linux下通过工具链编译生成 u-boot(elf)文件

BOOT.bin文件包括:第一级启动代码FSBL(SDK生成),硬件比特流文件(vivado生成)和u-boot(elf)

IP核类似于封装好的函数,有各种各样的IP核可进行调用。

历程中都是裸机程序操作IP核,那内核驱动程序和裸机程序意思是相同的,u-boot阶段其实已经将硬件已经映射好了,

现在做的就是在内核部分添加驱动,驱动可以通过AXI操作相应的外设模块。

在裸机中可以看到操作IP核的函数,而内核中没看到操作IP核的函数啊?怎么访问到的,是不是都是通用的总线协议,通过ID号进行操作的?

platform_driver_register 注册函数中看到了platfrom

platfrom是一种虚拟的地址总线。

今天的文章ZYNQ-AX7020学习笔记「建议收藏」分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/74374.html