一位全减器设计

1.逻辑抽象

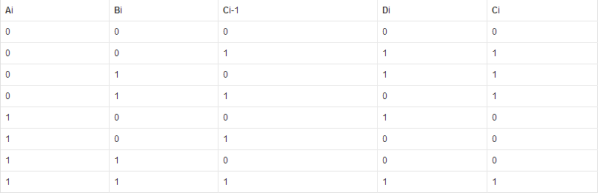

确定输入变量:被减数Ai,减数Bi,低位向本位的借位Ci。

由这三个变量我们就可以知道本位差Di以及本位向高位的借位Ci+1。(根据二进制数减法规律)

Di与Ci+1就是输出变量。

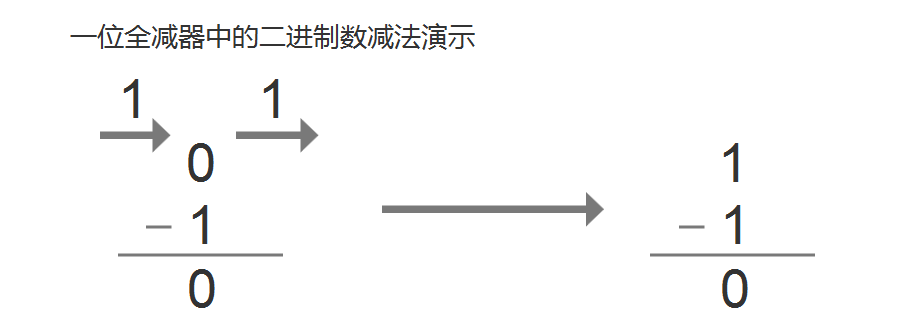

比如输入变量Ai=0,Bi=1,Ci=1,

0被借走1之后再-1显然不够减,到高位借1,所以输出的本位到高位的借位Ci+1就是1,二进制数中向高位借1当成2,再被低位借走1就是1,1-1=0,所以本位差Dn=0

由此规律得到真值表。

2.逻辑函数式

由得到的真值表写出输出变量的逻辑函数式

分别画出Ci+1与Di的卡诺图,逻辑函数式就等于卡诺图上填1的最小项之和。

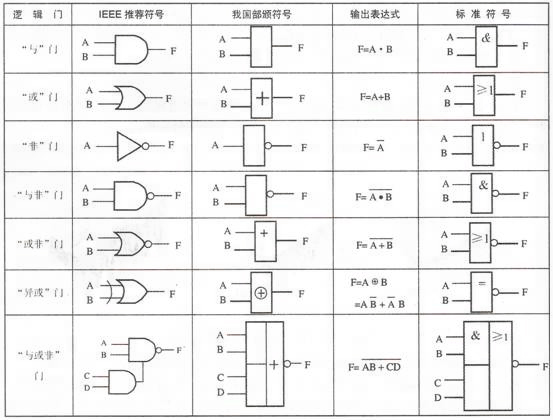

将逻辑函数化简或变换成适当形式:如与非-与非式,或非-或非式等

3.电路连接

根据得到的逻辑函数式画出电路。

此处附门电路对照表一张:

今天的文章组合逻辑电路全减器设计实验报告_用与非门设计一个全减器,其步骤是分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:http://bianchenghao.cn/76478.html