本文对BUFG/BUFGCE/BUFH/BUFHCE简单介绍,便于后续查看。

原语的使用:在vivado中找到所要用的原语,直接将其实例化到设计中即可。

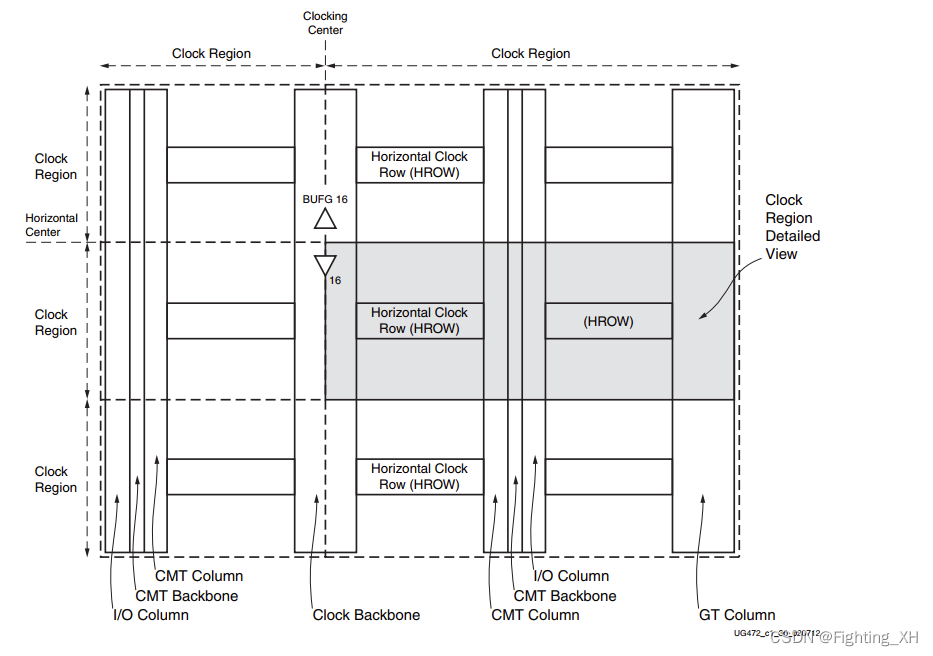

下图为 7 系列 FPGA 时钟架构图:

BUFG

全局时钟缓冲。它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。BUFG连接的是芯片中的专用时钟资源,能减少信号的传输延时,提高驱动能力。BUFG可以到达设备上的任何时钟点。

注意:如果内部产生的时钟,只在局部模块使用,可以考虑不使用BUFG。一个BUFG只能驱动一个时钟。

BUFG BUFG_inst (

.O(CLK0), // 1-bit output: Clock output.

.I(CLK) // 1-bit input: Clock input.

);

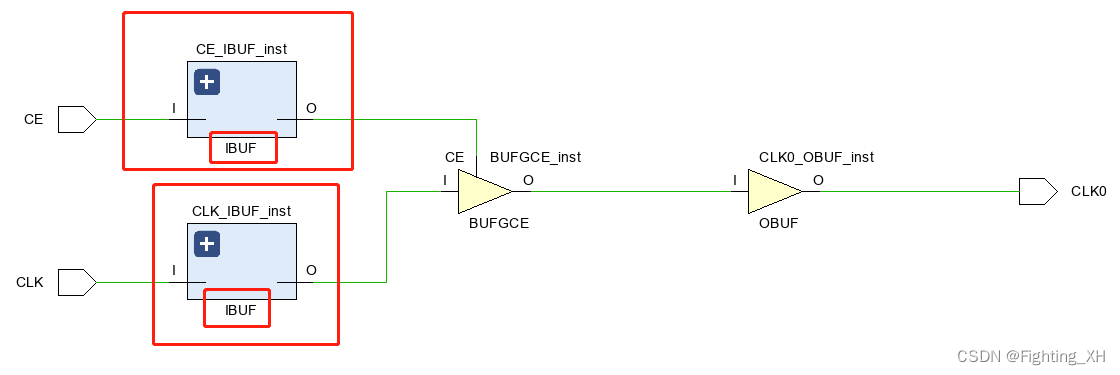

BUFGCE

带有使能端的全局时钟缓冲,使能端为高电平有效,即CE=0,Q=0.否则,Q=I。

除此之外,还有BUFGCE_1,和BUFGCE区别在于,当CE=0时,Q=1。

BUFGCE #(

.CE_TYPE("SYNC"), // ASYNC, HARDSYNC, SYNC

.IS_CE_INVERTED(1'b0), // Programmable inversion on CE .IS_I_INVERTED(1'b0), // Programmable inversion on I

.SIM_DEVICE("ULTRASCALE") // ULTRASCALE

)

BUFGCE_inst (

.O(CLK0), // 1-bit output: Buffer

.CE(CE), // 1-bit input: Buffer enable

.I(CLK) // 1-bit input: Buffer

);

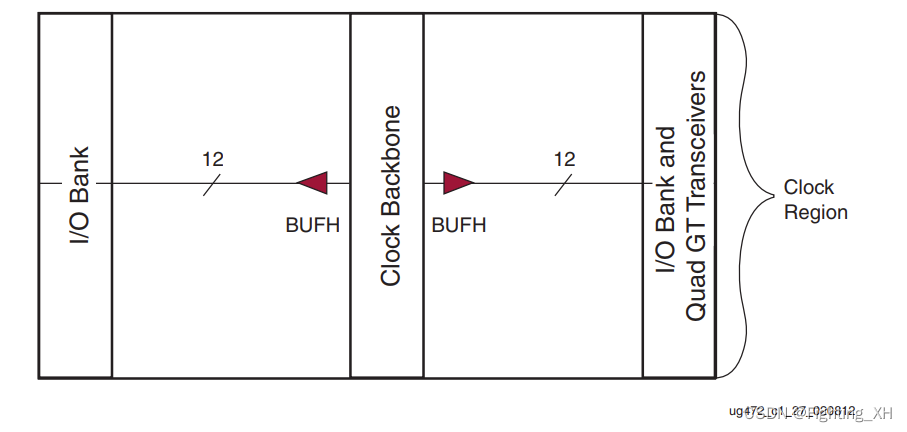

BUFH

水平时钟缓冲器,其允许通过水平时钟行访问单个时钟区域中的全局时钟线。 水平时钟缓冲器 (BUFH) 通过 HROW 驱动到该区域中的每个时钟点。

BUFH BUFH_inst (

.O(CLK0), // 1-bit output: Clock output

.I(CLK) // 1-bit input: Clock input

);

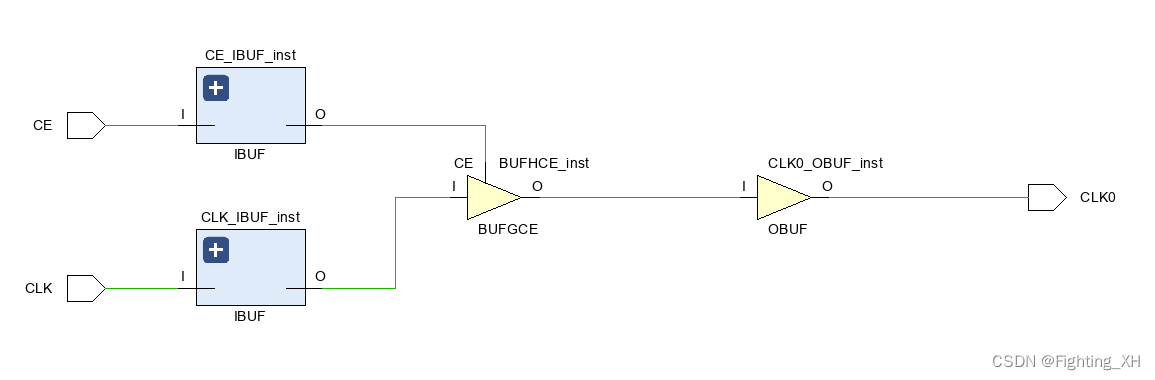

BUFHCE

带有使能端,以独立启用或禁用跨越单个时钟区域的时钟。每个时钟区域最多可支持 12 个时钟。

BUFHCE #(

.CE_TYPE("SYNC"), // "SYNC" (glitchless switching) or "ASYNC" (immediate switch)

.INIT_OUT(0) // Initial output value (0-1)

)

BUFHCE_inst (

.O(CLK0), // 1-bit output: Clock output

.CE(CE), // 1-bit input: Active high enable

.I(CLK) // 1-bit input: Clock input

);

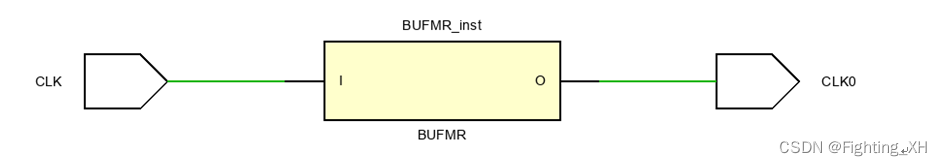

BUFMR

多时钟区域缓冲器。将时钟信号驱动到时钟区域内的专用时钟网络,与全局时钟树无关。

注意其允许区域和I/O时钟跨3个垂直相邻的时钟区域。

BUFMR BUFMR_inst (

.O(CLK0), // 1-bit output: Clock output (connect to BUFIOs/BUFRs)

.I(CLK) // 1-bit input: Clock input (Connect to IBUF)

);

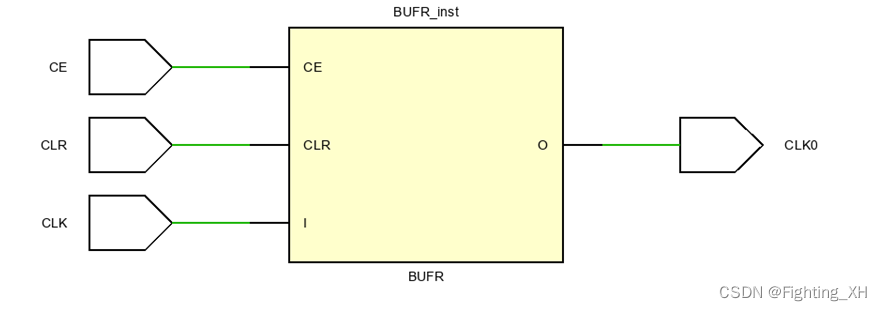

BUFR

区域时钟缓冲器,可以驱动现有时钟区域中的I / O逻辑和逻辑资源(CLB,Block RAM等)【驱动区域时钟树】

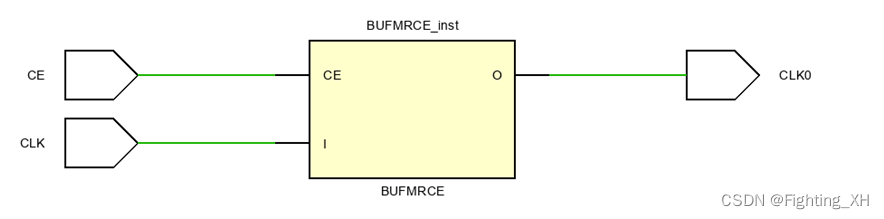

BUFMRCE

多了使能,如果在多个时钟区域中需要本地时钟,则BUFMRCE可以驱动相邻时钟区域中的多个BUFR组件,以进一步扩展该时钟功能。

IBUF

介绍

输入缓冲,综合的时候,工具会自动给输入信号连接IBUF。

IBUF IBUF_inst (

.O(O), // 1-bit output: Buffer output

.I(I) // 1-bit input: Buffer input

);

IBUFDS

重点是差分。

IBUFGDS的输入端仅仅与芯片的专用全局时钟输入管脚有物理连接,与普通IO和其它内部CLB等没有物理连接,因此差分信号进入片内之后不经过IBUFDS缓冲是无法直接处理的,即无法使用。

另外还有 IBUFDS、IBUFGDS和OBUFDS。这些都是差分信号缓冲器,均用于不同电平接口之间的缓冲和转换。

如下为IBUFDS原语:

两个电平接口,可认为是主从信号。主信号和从信号是同一个逻辑信号,但是相位相反

IBUFDS IBUFDS_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

今天的文章BUFG/BUFGCE/BUFH/BUFHCE/BUFH/BUFGHCE/BUFMR/BUFMRCE/BUFR/IBUF/IBUFDS分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/79588.html