单片机引脚简介

(本文中所有*均表示取非)

看图识物

AT89S51单片机实物

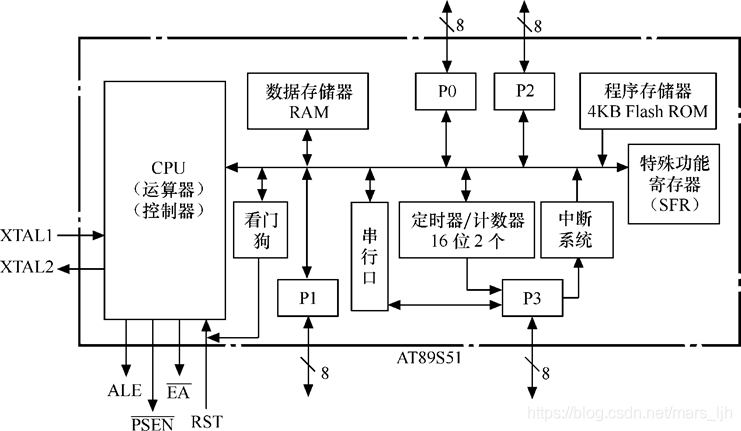

AT89S51单片机内部结构

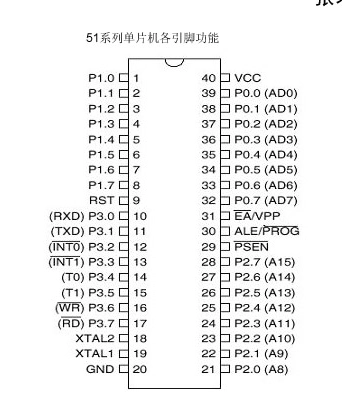

引脚简介

中央处理器CPU(运算器+控制器)8位

| 引脚 | 功能 | 作用 |

|---|---|---|

| 9引脚 | RST | 复位信号输入端,高电平有效。 引脚上有持续大于2个机器周期的高电平,单片机复位。 |

| 18引脚 | XTAL2 | 时钟引脚 |

| 19引脚 | XTAL1 | 时钟引脚 |

| 20引脚 | GND | 电源接地 |

| 29引脚 | *PSEN | 片内或片外存储的读选通信号,低电平有效 |

| 30引脚 | ALE/*PROG | ALE:CPU访问外部程序存储器或外部数据存储器提供低8位地址的锁存控制信号 *PROG:对Flash编程时,作为编程脉冲输入端 |

| 31引脚 | *EA/Vpp | *EA:外部程序存储器访问允许控制端。 Vpp:对片内Flash编程时,Vpp引脚接入编程电压 |

| 40引脚 | VCC | 电源+5v高电平 |

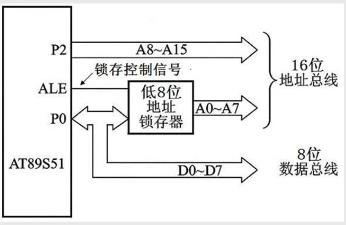

ALE功能

地址是16位的,分为高八位和低八位。它分别由P0引脚和P2引脚组合发送

为啥有ALE这个功能引脚呢?

首先:单片机的内存是很小的,并且它的引脚很少,但是有时候需要和外部进行数据传输,此时需要P0口作为地址总线发送地址,但是由于引脚太少了,P0口还需要发送数据,所以P0口在不同的时候功能是不一样的(分时复用的概念),此时需要一位信号来控制它的状态,在ALE这个引脚输出高电平的时候,激活和这个第一功能,锁住P0发送的低8位地址,随后和P2口发送的高8位地址结合

- 外部程序存储器:机器运行时程序存放的存储器:内存、缓存

- 外部数据存储器:机器停止后仍能保存数据的存储器:机械硬盘、固态硬盘、NAS

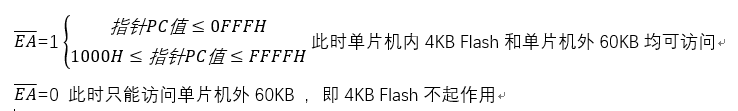

*EA

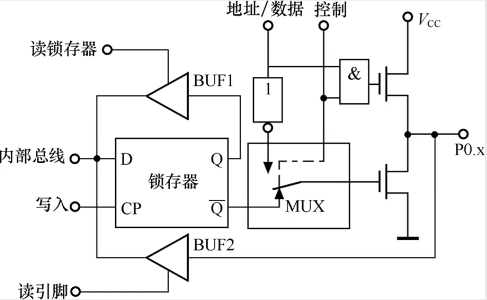

并行IO口P0 (P0.7~P0.0)8位

漏极开路的双向IO口

P0口有两个功能:

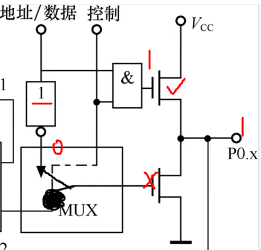

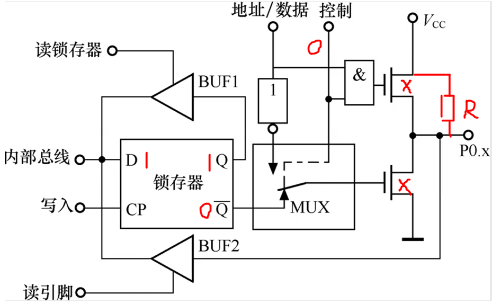

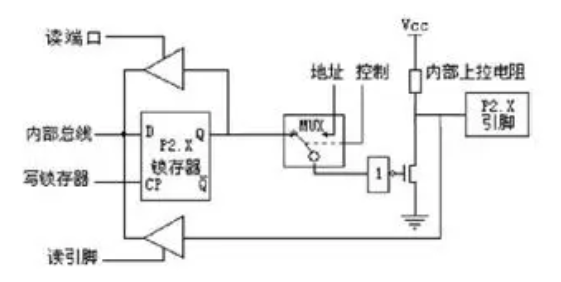

功能的选择取决于图中的“控制”信号,1的时,MUX打到上面和地址/数据相连,0的时候,MUX打在下面和锁存器相连

- 地址/数据发送“1”,控制是“1”,上方的与门输出结果为1,场效应管导通(√),下方的非门输出结果为0,场效应管关闭(×),最后P0.X输出为“1”

- 地址/数据发送“0”,控制是“1”,上方的与门输出结果为0,场效应管导通(×),下方的非门输出结果为1,场效应管关闭(√),最后P0.X输出为“0”

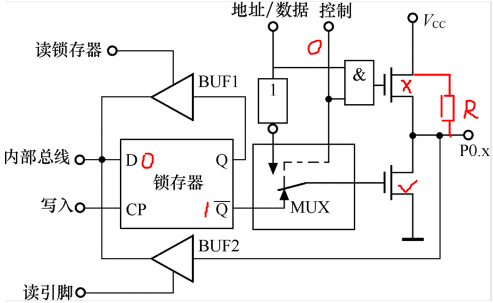

(2)通用I/O口

-

输出1:CPU在D写入“1”,*Q为“0”,下方场效应管关闭(×),控制是“0”,上方场效应管导通(√),此时需要接一个上拉电阻P0.X才可以输出“1”

-

输出“0”:CPU在D写入“1”,*Q为“0”,下方场效应管关闭(√),控制是“0”,上方场效应管导通(√),此时P0.X输出“0”

-

输入:两种方式(读锁存器、读引脚)

读锁存器:锁存器状态由Q端经上方的三态缓冲器BUF1进入内部总线

读引脚:锁存器*Q发出信号“0”,下方场效应管关闭,从P0.X经过三态缓冲器BUF2进入内部总线

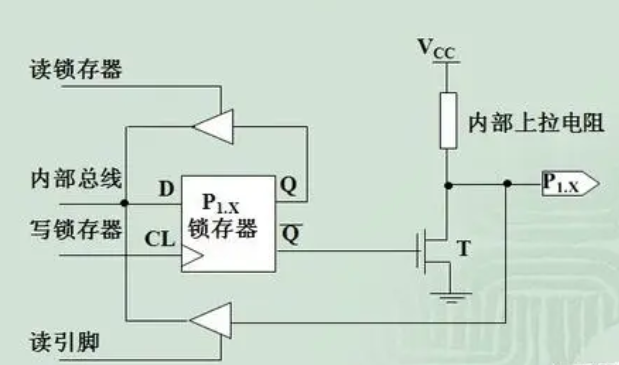

并行IO口P1 (P1.7~P1.0)8位

- D写入“1”,*Q为“0”,场效应管关闭,此时P1.X输出“1”

- D写入“0”,*Q为“1”,场效应管开启,此时P1.X输出“0”

作为输入端口:

- 读锁存器

- 读引脚

并行IO口P2 (P2.7~P2.0)8位

准双向口,即可以作为通用IO口使用,也作为高8位地址总线使用

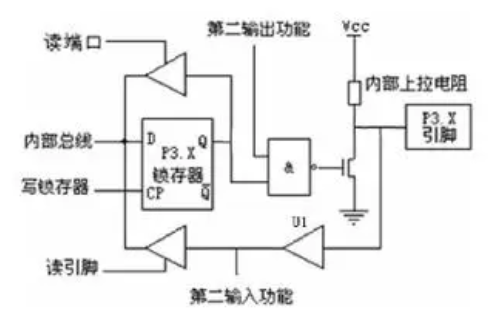

并行IO口P3(P3.7~P3.0)8位

| 引脚 | 第二功能 | 说明 |

|---|---|---|

| P3.0 | RXD | 串行数据输入口 |

| P3.1 | TXD | 串行数据输出口 |

| P3.2 | *INT0 | 外部中断0输入 |

| P3.3 | *INT1 | 外部中断1输入 |

| P3.4 | T0 | 定时器0外部计数输入 |

| P3.5 | T1 | 定时器1外部计数输入 |

| P3.6 | *WR | 外部数据存储器的写选通控制信号 |

| p3.7 | *RD | 外部数据存储器的读选通控制信号 |

今天的文章80c51单片机引脚图功能介绍_sta540sa各引脚功能分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/86041.html