在systemverilog仿真过程中经常会遇到采样数据差一拍的问题,当希望获取当下cycle的数据,却获取的是上一cycle的旧数据,当希望获取的是采样前的数据,却阴差阳错的获取了采样后的数据。

verilog实现的是硬件电路,systemverilog仿真其实不是真正的硬件行为,而是软件行为,用软件来模拟硬件的行为,而软件的事件处理其实是串行的,为了模拟硬件行为,仿真器需要根据一定的规则处理电路事件。

一、time-slot

仿真过程由许多连续的时间组成的,每个时间成为一个time-slot,每个time-slot又被划分为多个区域,每个区域顺序执行。

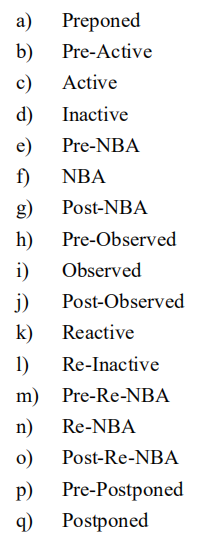

systemverilog标准将一个time-slot划分为了17个区域:

time-slot划分

每个time-slot的执行过程如下:

执行顺序

一个time-slot的17个region的执行顺序如上所示,其中绿色框中的部分为module事件的执行,红色框中的为program事件的执行,observed为断言的执行。

- Active region

执行和计算module当前活动:

- 阻塞赋值

- 非阻塞赋值表达式右值

- 连续赋值语句

- 计算输入并更新verilog原语输入

2.Inactive region

带有#0延时的事件被推迟到Inactive执行。

3. NBA region

非阻塞赋值左值更新在NBA生效。

4. observed region

断言在此region执行。

time-slot的细节可以参考systemverilog协议的“Scheduling semantics”章节。

二、仿真竞争冒险

1.仿真环境搭建在program中

program的一个重要作用就是将仿真环境和硬件代码分割开来,在program执行时,module的行为已经确定,避免了验证环境和RTL线程的竞争冒险。

所以在@rtl.clk时采样rtl.sig会得到更新后的“新值”。

2.仿真环境搭建在module中

由于program语法的限制在program中搭建仿真环境并不是很方便,更多的仿真环境是搭建在module中的。

分析一下下面两种情况:

- @rtl.clk时采样组合逻辑rtl.sig值,此时会出现竞争冒险导致采样值不确定是新值还是旧值。

rtl.sig在active region更新,环境使用rtl.sig也在active region,两个进程的顺序不确定。

- @rtl.clk时采样时序逻辑rtl.sig值,此时采样的值为更新前的旧值。

rtl.sig在NBA region更新,而环境使用rtl.sig在active region,顺序确定。

三、interface

上面提到在module中搭建仿真环境会存在冒险竞争的问题,interface的clocking block为解决这个问题提供了方案。

interface示例

在硬件电路中有一个很重要的概念建立时间和保持事件,如果希望电路功能正常,不出现时序问题,需要综合出的电路满足建立保持时间。

所谓的建立时间就是在时钟沿前数据要保持稳定的时间,保持时间是在时钟沿后数据要保持稳定的时间。

interface的clocking block实现原理也是类似的,clocking block会在时钟沿前一段时间采样信号值,在时钟沿后一段时间驱动信号值,避免了可能出现的采样和驱动冒险。

上图中的1step,对于input为上一个time-slot的postponed region,当然也可以设置为具体的时间,如1ps。如果不设置信号skew,则默认输入为1step,输出为0。

在使用@if.cb时,该时钟对齐在observed region。

对于时钟与信号的采样分为以下几种情况(这里只讨论验证环境搭建在module中的情况):

- @rtl.clk后采样rtl.sig,上面已经讨论过了,不赘述。

- @rtl.clk采样if.cb.sig

clocking block的输入信号采样发生在上一time-slot的最后,故采样的值为“旧值”。

- @if.cb后采样rtl.sig

时钟对齐在observed region,信号已经完成更新,采样的值为“新值”。

- @if.cb后采样if.cb.sig

采样值为“旧值”。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/bian-cheng-ji-chu/91931.html