目录

一、以太网通信简介

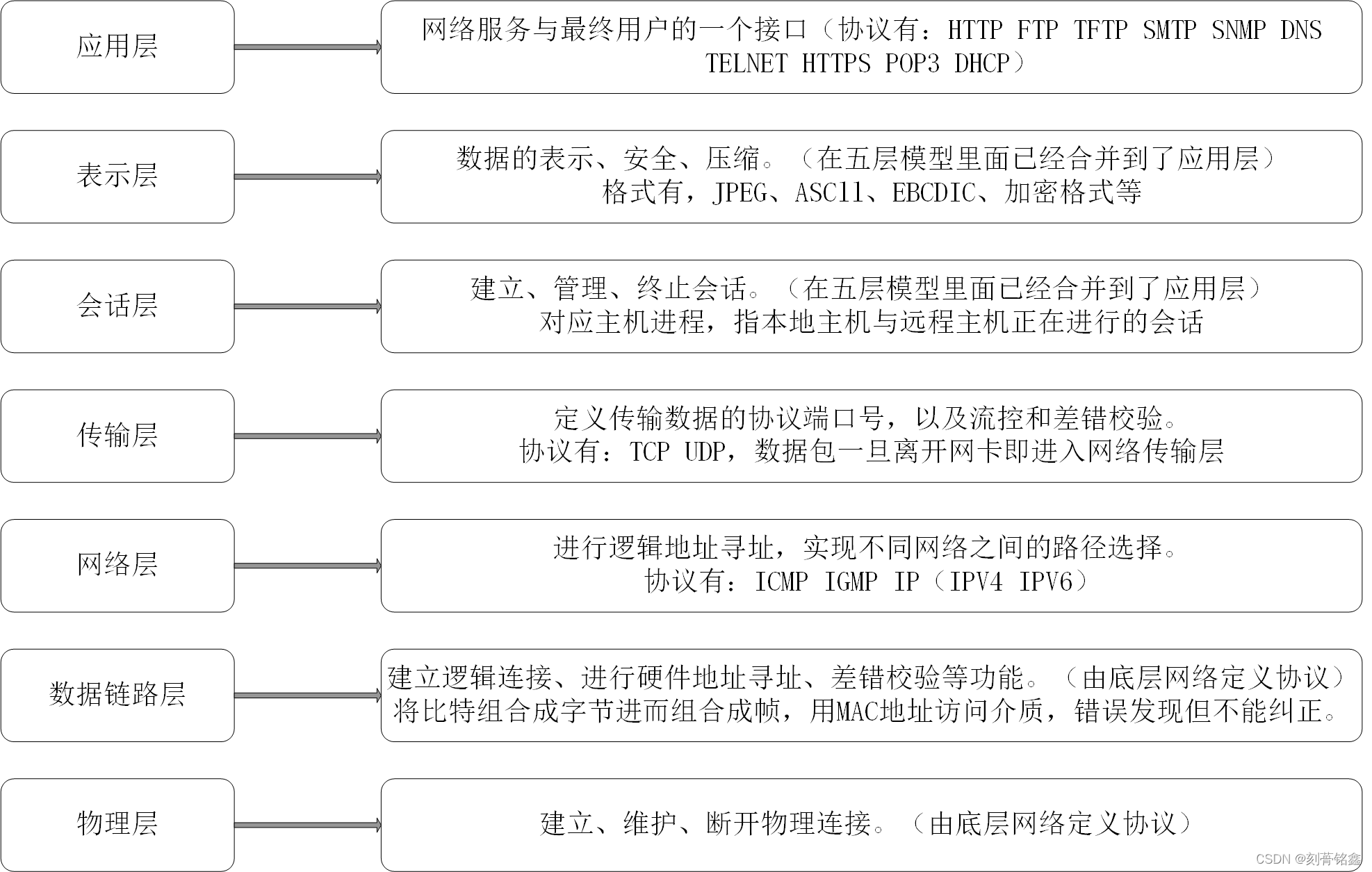

1.OSI七层模型

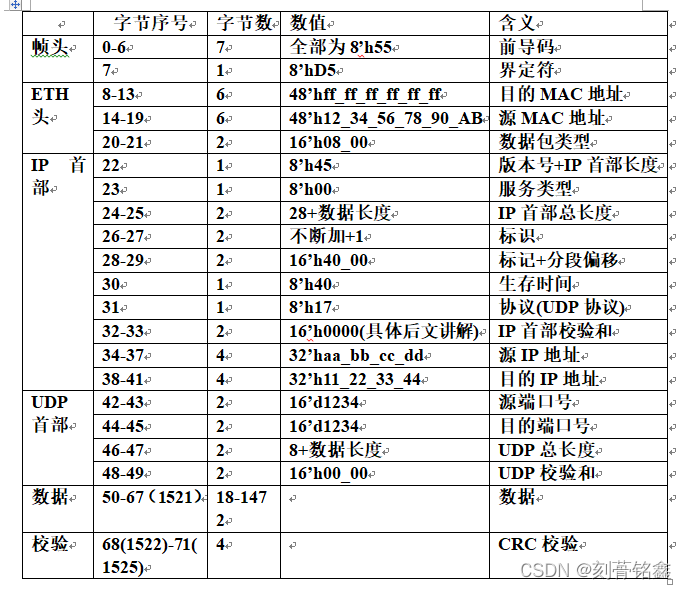

2.以太网数据包解析

3.IP首部校验和计算与检验

二、以太网通信实例

1.整体实验框图

2.发送部分时序图

3.实验代码及仿真结果

总结

前文我们讲述了多种通信协议(串口、IIC、SPI等协议),而以太网通信是相对比较高速的一种通信方式。目前,以太网是指遵守 IEEE 802.3 标准组成的局域网,由 IEEE 802.3 标准规定的主要是位于参考模型的物理层(PHY)和数据链路层中的介质访问控制子层(MAC)。讲到这,再简单的说一下国际标准化组织 (ISO)为了统一通信标准,将整个以太网通信结构制定了 OSI (Open System Interconnection)模型,译为开放式系统互联。

OSI 定义了网络互连的七层框架(物理层、数据链路层、网络层、传输层、会话层、 表示层、应用层),即 OSI 开放互连系统参考模型。每个层功能不同,网络通信中各司其 职,整个模型包括硬件和软件定义。 OSI 模型只是理想分层,一般的网络系统只是涉及其中几层。其各层的参考模型及简介如下图所示。

在物理层中,主要规定了以太网使用的介质(水晶头网线)、数据编码方式(曼彻斯特编码)和冲突检测机制(CSMA/CD 冲突检测)等,在实际应用中主要是通过一个PHY芯片实现其功能的。

在数据链路层中,主要规定了数据链路层的下半部分MAC子层,它主要是负责与物理层进行的数据交换,比如是否可以发送数据,发送的数据是否正确,对数据流进行控制等。它自动对来自上层的数据包加上一些控制信号,交给物理层。接收方得到正常数据时,自动去除 MAC 控制信号,把该数据包交给上层。

下面对以太网发送的一包数据进行解析,如下图所示:

上述协议中的IP首部校验和的其计算方法如下:

IP 首部校验和计算

校验字节强制置 0,将 IP 首部 20 字节 按 2 字节, 即 16 比特,分开分别相加,若如果 大于 FFFF 那么把高 16 位与低 16 位相加,直到最终结果为 16 比特数据。将计算结果取反作为 IP 首部校验和字节。

例:抓取 IP 数据包,取 IP 数据报报头部分(20B),数据如下,45 00 00 30 80 4c 40 00 80 06 b5 2e d3 43 11 7b cb 51 15 3d,计算 IP 首部校验和。

(1) 将校验和字段 b5 2e 置为 00 00,数据变为:

45 00 00 30 80 4c 40 00 80 06 00 00 d3 43 11 7b cb 51 15 3d

(2) 以 2 字节为单位,数据反码求和:

4500+0030+804c+4000+8006+0000+d343+117b+cb51+153d=34ace

(3) 将进位(3)加到低 16 位(4ace)上:

0003+4ace=4ad1

(4) 将 4ad1 取反得:checksum = b52e

对 IP 首部中每个 16 bit 进行二进制反码求和,将计算结果再取反码,若结果为 0,通过检验,否则,不通过检验。

例:验证 IP 首部 45 00 00 30 80 4c 40 00 80 06 b5 2e d3 43 11 7b cb 51 15 3d

(1) 对 IP 首部进行反码求和:

4500+0030+804c+4000+8006+b52e+d343+117b+cb51+153d=3fffc

0003+fffc=ffff

(2) 求和结果取反码:

~ffff=0 ,校验正确。

对于上述协议中的循环冗余码校验(CRC)校验,其详细内容可以参考V3学院——尤老师腾讯课堂FPGA从入门到实战最后一节课讲解的CRC循环冗余校验,个人感觉讲解的非常好,适合初学者学习。

要求:FPGA采集各路实验数据,并将各路数据打包好后通过网口上传到上位机进行数据分析。本实验仅仅是完成了FPGA与上位机之间通过网口通信的过程。

下边给出整个系统的实验框图:

输入信号:sys_clk,由外部 PHY 芯片传入时钟(eth_clk)分频得到;

sys_res,由外部复位按键传入

sys_en,数据发送开始信号,由外部传入

send_data,待发送的数据,由外部传入

下面给出实验代码:

1.发送部分

2.CRC循环冗余校验(该部分代码抄取了征途Pro《FPGA Verilog开发实战指南——基于Altera EP4CE10》2020.12.16(下)中的以太网数据换回实验中的CRC校验代码)

3.下边给出顶层及仿真tb文件,为了方便仿真观察时序,将两部分合成如下代码

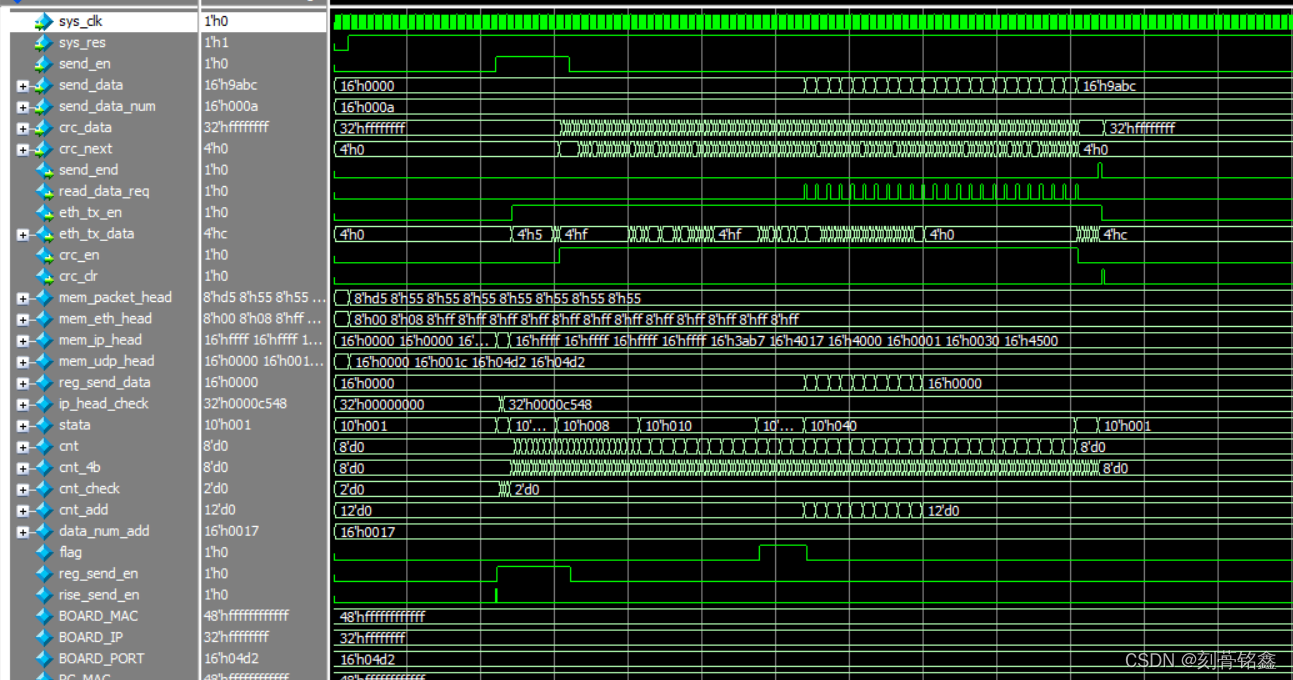

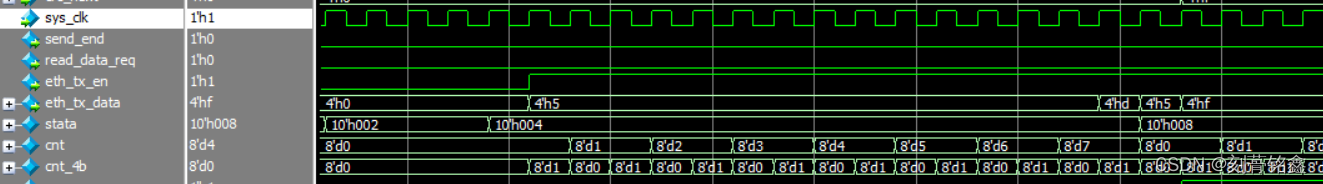

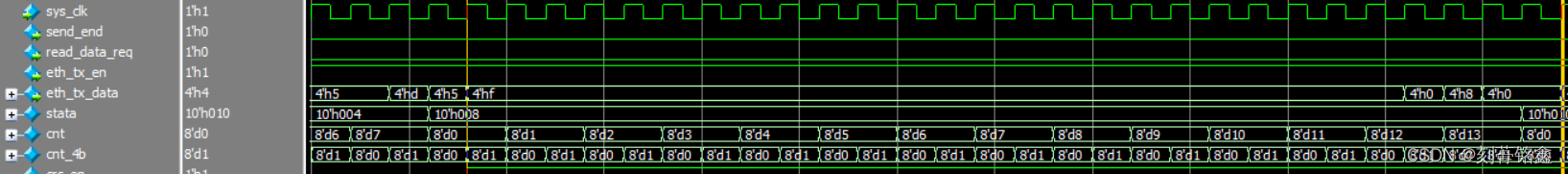

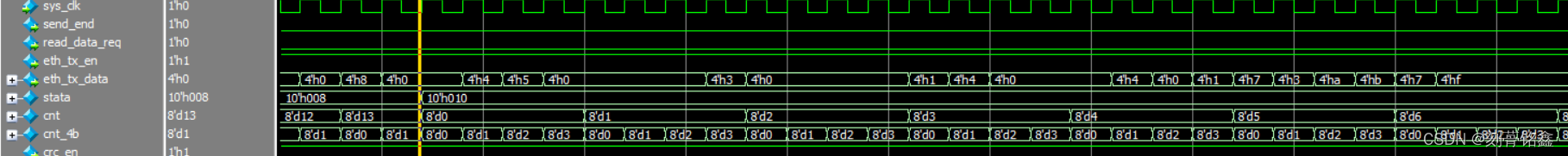

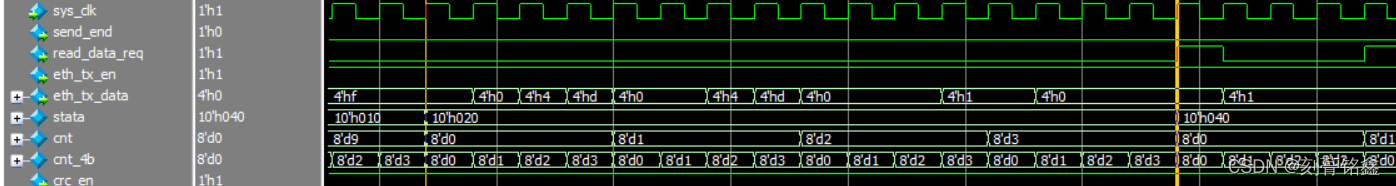

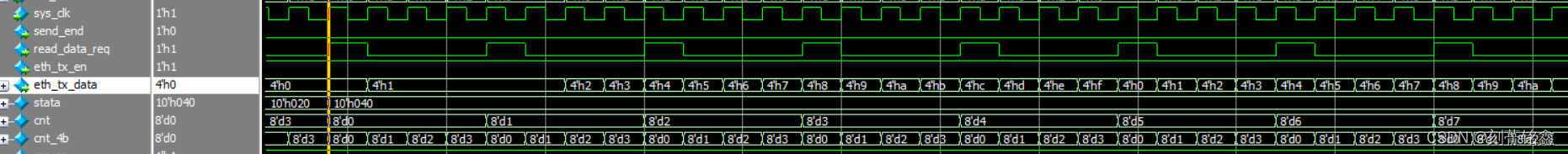

下图给出仿真的时序结果:图1是整体信号的时序图,图2对应PACK_HEAD状态输出的信号,图3对应ETH_HEAD状态输出的信号,图4对应IP_HEAD状态输出的信号,图5对应UDP_HEAD状态输出的信号,图6对应DATA状态输出的信号,图7对应CRC状态输出的信号。

图1

图2

图3

图4

图5

图6

图7

图7

对于以太网通信而言,更多的还是趋向于单片机的控制,其程序代码比Verilog要简单许多,读者可以尝试着做一下该实验。通过FPGA控制以太网通信,其时序逻辑相对比较复杂,本文仅仅给出了FPGA通过网口进行发送的时序、代码,由于疫情在家,身边没有硬件设备,后期将会对该程序应用于实践。

初次创作,难免文章中存在错误,希望读者能够及时纠正并给予私信,望大家共同进步!

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/bian-cheng-ri-ji/54103.html