1芯片与开发板

2.技术指标

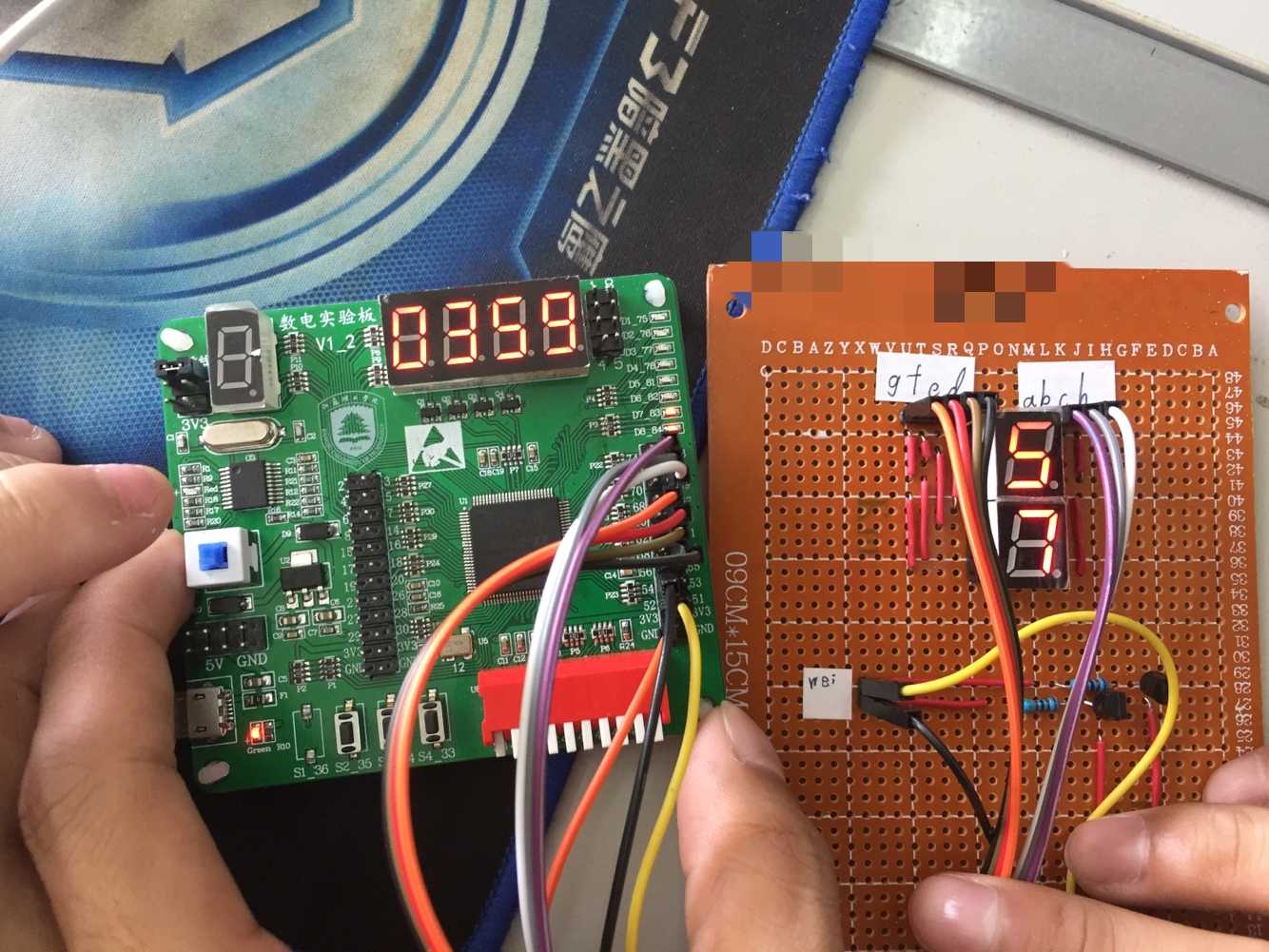

- 具有正常的时、分、秒计数显示功能,用六个数码管分别显示小时,分钟,秒钟

- 按键实现校时,校分功能

- 利用指示灯实现整点报时功能

- 路灯功能:晚上六点到早上五点亮

- 起始时间03:59:55

3.底层代码

分频器FDIV250

Library ieee;

Use ieee.std_logic_1164.all;

Use ieee.std_logic_unsigned.all;

Use ieee.std_logic_arith.all;

Entity FDIV250 is

generic(N: integer:=250); --rate=N,N是偶数

port(

clkin: IN std_logic;

clkout: OUT std_logic

);

End FDIV250;

Architecture a of FDIV250 is

signal cnt: integer range 0 to n/2-1;

signal temp: std_logic;

Begin

process(clkin)

begin

if(clkin'event and clkin='1') then

if(cnt=n/2-1) then

cnt <= 0;

temp <= NOT temp;

else

cnt <= cnt+1;

end if;

end if;

end process;

clkout <= temp;

End a;

D触发器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY D_DD_RS IS

PORT (D,CLOCK:IN STD_LOGIC;

Q:OUT STD_LOGIC);

END ENTITY D_DD_RS;

ARCHITECTURE BEHAVIOURAL OF D_DD_RS IS

BEGIN

PROCESS(CLOCK)IS

BEGIN

IF (CLOCK'EVENT AND CLOCK = '1') THEN

Q <= D;

END IF;

END PROCESS;

END;

根据D触发器制作的消抖电路

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY HOUR IS

PORT (KEYIN,CLK: IN STD_LOGIC;

hour_1,hour_0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE BHV OF HOUR IS

SIGNAL hour1 :STD_LOGIC_VECTOR(3 DOWNTO 0):="0000";

SIGNAL hour0 :STD_LOGIC_VECTOR(3 DOWNTO 0):="0011";

SIGNAL CLOCK :STD_LOGIC;

BEGIN

CLOCK <= CLK or (not KEYIN);

--由于键盘未按下是高电平,所以用非门和或门制作一个触发信号,上升沿进位

PROCESS(CLOCK)

BEGIN

IF(CLOCK'event and CLOCK = '1') THEN

IF(hour1 = 2 AND hour0 = 3) THEN

hour1 <= "0000";

hour0 <= "0000";

ELSIF (hour0 = 9) THEN

hour1 <= hour1+1;

hour0 <= "0000";

ELSE

hour0 <= hour0+1;

END IF;

END IF;

END PROCESS;

hour_1 <= hour1;

hour_0 <= hour0;

END;

MIN(初值59)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY MIN IS

PORT (CLK,KEYIN: IN STD_LOGIC;

RCO:OUT STD_LOGIC;

min_1,min_0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE BHV OF MIN IS

SIGNAL min1 :STD_LOGIC_VECTOR(3 DOWNTO 0):="0101";

SIGNAL min0 :STD_LOGIC_VECTOR(3 DOWNTO 0):="1001";

SIGNAL CLOCK:STD_LOGIC;

BEGIN

CLOCK <= (not KEYIN) or CLK;

PROCESS(CLOCK)

BEGIN

IF(CLOCK'event and CLOCK = '1') THEN

IF(min1 = 5 AND min0 = 9) THEN

min1 <= "0000";

min0 <= "0000";

RCO <= '1';

ELSIF(min0 = 9) THEN

min1 <= min1+1;

min0 <= "0000";

ELSE

min0 <= min0+1;

RCO <= '0';

END IF;

END IF;

END PROCESS;

min_1 <= min1;

min_0 <= min0;

END;

SEC(初值55)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SEC IS

PORT (CLK: IN STD_LOGIC;

RCO:OUT STD_LOGIC;

sec_1,sec_0: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE BHV OF SEC IS

SIGNAL sec1:STD_LOGIC_VECTOR(3 DOWNTO 0):="0101";

SIGNAL sec0:STD_LOGIC_VECTOR(3 DOWNTO 0):="0101";

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK = '1') THEN

IF(sec1 = 5 AND sec0 = 9) THEN

sec1 <= "0000";

sec0 <= "0000";

RCO <= '1';

ELSIF(sec0 = 9) THEN

sec1 <= sec1+1;

sec0 <= "0000";

ELSE

sec0 <= sec0+1;

RCO <= '0';

END IF;

END IF;

END PROCESS;

sec_1 <= sec1;

sec_0 <= sec0;

END;

六进制计数器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT5 IS

PORT(CLK: IN STD_LOGIC;

Q:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

END;

ARCHITECTURE BAV OF CNT5 IS

SIGNAL Q1:STD_LOGIC_VECTOR(2 DOWNTO 0);

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK = '1') THEN

Q1 <= Q1+1;

IF(Q1 = 5) THEN

Q1 <= "000";

END IF;

END IF;

END PROCESS;

Q <= Q1;

END;

CONTROL

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY CONTROL IS

PORT (hour_1,hour_0,min_1,min_0,sec_1,sec_0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DD:IN STD_LOGIC_VECTOR(2 DOWNTO 0);

Q1,Q2:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END;

ARCHITECTURE BAV OF CONTROL IS

BEGIN

Q1 <= min_0 WHEN DD = "000" ELSE

min_1 WHEN DD = "001" ELSE

hour_0 WHEN DD = "010" ELSE

hour_1 WHEN DD = "011" ELSE

"1111";

--由于开发板上只有4位数码管,所以外接延伸两个数码管显示秒的个位十位

Q2 <= sec_0 WHEN DD = "100" ELSE

sec_1 WHEN DD = "101" ELSE

"1111";

END;

位选

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY WEI IS

PORT (Q: IN STD_LOGIC_VECTOR(2 DOWNTO 0);

DD:OUT STD_LOGIC_VECTOR(5 DOWNTO 0));

END;

ARCHITECTURE BAV OF WEI IS

BEGIN

PROCESS(Q)

BEGIN

CASE Q IS

WHEN "000" => DD <= "001110";

--外接数码管位选高电平触发,内接数码管位选低电平触发

WHEN "001" => DD <= "001101";

WHEN "010" => DD <= "001011";

WHEN "011" => DD <= "000111";

WHEN "100" => DD <= "101111";

WHEN "101" => DD <= "011111";

WHEN OTHERS => DD <= "001111";

END CASE;

END PROCESS;

END;

内接数码管段选(共阳极)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DUAN IS

PORT (AA: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

YY:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END;

ARCHITECTURE BAV OF DUAN IS

SIGNAL TEMP:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(AA,TEMP)

BEGIN

CASE AA IS

WHEN "0000" => TEMP <= "00111111";

WHEN "0001" => TEMP <= "00000110";

WHEN "0010" => TEMP <= "01011011";

WHEN "0011" => TEMP <= "01001111";

WHEN "0100" => TEMP <= "01100110";

WHEN "0101" => TEMP <= "01101101";

WHEN "0110" => TEMP <= "01111101";

WHEN "0111" => TEMP <= "00000111";

WHEN "1000" => TEMP <= "01111111";

WHEN "1001" => TEMP <= "01101111";

WHEN OTHERS => TEMP <= "11111111";

END CASE;

YY <= NOT TEMP;

END PROCESS;

END;

外接数码管段选(共阴极)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DUAN2 IS

PORT (AA: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

YY:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END;

ARCHITECTURE BAV OF DUAN2 IS

SIGNAL TEMP:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(AA,TEMP)

BEGIN

CASE AA IS

WHEN "0000" => TEMP <= "00111111";

WHEN "0001" => TEMP <= "00000110";

WHEN "0010" => TEMP <= "01011011";

WHEN "0011" => TEMP <= "01001111";

WHEN "0100" => TEMP <= "01100110";

WHEN "0101" => TEMP <= "01101101";

WHEN "0110" => TEMP <= "01111101";

WHEN "0111" => TEMP <= "00000111";

WHEN "1000" => TEMP <= "01111111";

WHEN "1001" => TEMP <= "01101111";

WHEN OTHERS => TEMP <= "11111111";

END CASE;

YY <= TEMP;

END PROCESS;

END;

报时电路

思路:当读取时间读到59分55秒时,EN使能,截取频率1HZ的CLK作为LED灯信号,闪烁。

当读取时间到00分00秒时,EN不使能,LED=0,不亮

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY BAOSHI IS

PORT(CLK:IN STD_LOGIC;

min_1,min_0,sec_1,sec_0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

LED:OUT STD_LOGIC);

END;

ARCHITECTURE BAV OF BAOSHI IS

SIGNAL EN:STD_LOGIC;

SIGNAL min1,min0,sec1,sec0:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

min1 <= min_1;

min0 <= min_0;

sec1 <= sec_1;

sec0 <= sec_0;

PROCESS(min1,min0,sec1,sec0)

BEGIN

IF(min1 = 5 AND min0 = 9 AND sec1 = 5 AND sec0 = 5) THEN

EN <= '1';

ELSIF(min1 = 0 AND min0 = 0 AND sec1 = 0 AND sec0 = 0) THEN

EN <= '0';

ELSE

EN <= EN;

END IF;

END PROCESS;

PROCESS(EN)

BEGIN

IF(EN = '1') THEN

LED <= CLK;

ELSIF(EN = '0') THEN

LED <= '0';

ELSE

LED <= '0';

END IF;

END PROCESS;

END;

路灯电路

与报时电路思路相同,不过更简单

读取时间,当时间到达18:00:00时,灯亮

读取时间,当时间到达05:00:00时,灯灭

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LUDENG IS

PORT(hour_1,hour_0,min_1,min_0,sec_1,sec_0:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

LED:OUT STD_LOGIC);

END;

ARCHITECTURE BAV OF LUDENG IS

SIGNAL hour1,hour0,min1,min0,sec1,sec0:STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL LED1:STD_LOGIC:='0';

BEGIN

hour1 <= hour_1;

hour0 <= hour_0;

min1 <= min_1;

min0 <= min_0;

sec1 <= sec_1;

sec0 <= sec_0;

PROCESS(hour1,hour0,min1,min0,sec1,sec0,LED1)

BEGIN

IF(hour1 = 1 AND hour0 = 8 AND min1 = 0 AND min0 = 0 AND sec1 = 0 AND sec0 = 0) THEN

LED1 <= '1';

ELSIF(hour1 = 0 AND hour0 = 5 AND min1 = 0 AND min0 = 0 AND sec1 = 0 AND sec0 = 0) THEN

LED1 <= '0';

ELSE

LED1 <= LED1;

END IF;

END PROCESS;

LED <= LED1;

END;

4.顶层设计

注意:开发板NE555频率发生器引脚为PIN_12,产生的频率为50Mhz

今天的文章根据VHDL语言制作的的数字钟分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/11952.html