为了实现FPGA和HPS之间的存储器共享和数据传输,Altera SoC FPGA提供了两种方式用于FPGA和HPS通信。分别是FPGA to SDRAM和AXI bridge。

FPGA to SDRAM接口是HPS内部的SDRAM控制器提供给FPGA访问HPS内存的接口,AXI bridge是FPGA和HPS之间数据交互的接口,包括f2h、h2f和lw_h2f。

下面分别做简要概述:

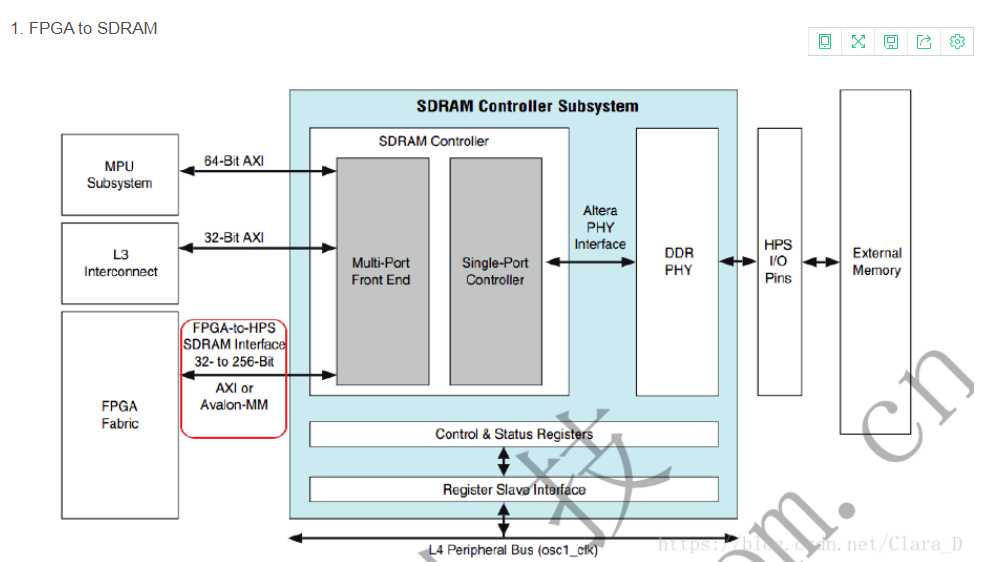

1、FPGA to SDRAM

由图可知,FGPA可以通过FPGA to SDRAM接口直接访问HPS端的内存区域。

支持AXI-3/4协议和Avalon-MM协议。

此时FPGA是master而HPS是slave。

2、AXI bridge

AXI bridge在HPS端使用的是AMBA AXI协议,用户在FPGA中逻辑设计时可以使用AXI协议与HPS通信。

Qsys interconnect实现了AXI协议到Avalon-MM协议的自动转换。

在通信过程中,如果使用了FPGA-to-HPS Bridge,FPGA 作为Master不仅可以访问HPS的内存,还能访问到HPS的外设。

(AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持Outstanding传输访问和乱序访问,并更加容易进行时序收敛。

引用来源于http://blog.sina.com.cn/s/blog_13f7886010102x2iz.html

FPGA-to-HPS Bridge

地址位宽时32-bit,数据位宽32-bit/64-bit/128-bit用户可以自行设置,ID时8-bit

HPS-to-FPGA Bridge

址位宽时30-bit,数据位宽32-bit/64-bit/128-bit用户可以自行设置,ID时128-bit。有0x3FFF0000,接近1G

的寻址空间。

Lightweight HPS-to-FPGA Bridge

地址位宽时21-bit,数据位宽只有32-bit,ID时8-bit。寻址空间只有2M,适合数据量不大、速度不快的数据传输。

今天的文章关于HPS和FPGA之间的桥接学习笔记(一)分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/24699.html