目录

1. 前言

平台是XCKU040,Vivado版本2019.1,不同的平台和软件IP配置界面会有些许不同哦。

官方文档:MicroBlaze Processor Reference Guide

MicroBlaze在FPGA的设计中经常被用到,MicroBlaze可以理解为使用FPGA逻辑资源实现的一个处理器软核。处理器所具有的功能,MicroBlaze也具有。

优点:

- 在完成控制任务时,处理器有FPGA无法比拟的优势

- 传统的FPGA+ARM外接方式还需要解决FPGA和ARM通信的问题。这是个非常麻烦的过程。

- 强大的开发库支持,大大节省开发时间

- 开发灵活

在带有MicroBlaze设计中,所有外设都通过AXI接口挂在总线上,可供MicroBlaze进行访问

Xilinx官方为MicroBlaze所能挂载的所有外设几乎都提供了基于C语言的Example Deign,Example Deign中的函数可以稍加修改就能直接使用。这极大地方便了软件工作者的开发。

FPGA工程师必须能够完成简单的C语言程序的开发。

注1:除了MicroBlaze软核方式,Xilinx官方还提供了ZYNQ的解决方案,它将FPGA与ARM硬核封装到了同一块芯片中,ARM和FPGA之前存在几种高速通信总线可选,ARM有自己的外设可选,处理速度更快,功能更加强大。这个以后有时间也会写博客说说ZYNQ。

注2:在MicroBlaze开发中也个人习惯用ZYNQ中PL(Progarmmable Logic)和PS(Processing System)的概念用来代指FPGA端的硬件开发和ARM端的软件开发。

2. 介绍

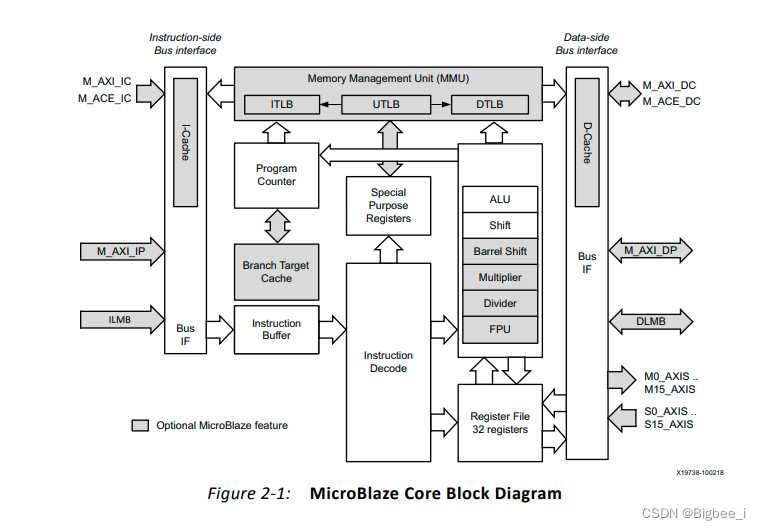

2.1 核架构介绍

有时间单独写一篇博客介绍MicrBlaze

2.2 工程介绍

本文章更多是从个人笔记的角度编写。从0开始搭建一个能够使用各种外设的简单设计。

包含一下内容:

- AXI_UARTLite

- AXI_GPIO

- AXI_CAN

- BARM

- 带中断功能

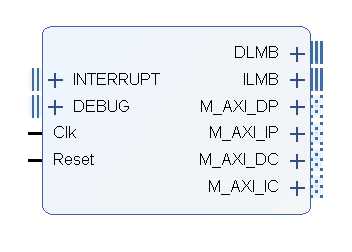

2.2 接口介绍

MicroBlaze接口中常见的有如下几种:

| 接口名 | 作用 |

|---|---|

| INTERRUPT | 中断控制器接口,用来连接中断控制器 |

| DEBUG | DEBUG接口,用来连接MDM,方便开发中进行DEBUG |

| Clk | MicroBlaze系统运行时钟 |

| Reset | 系统复位,高有效 |

| DLMB | 处理器数据接口 |

| ILMB | 处理器指令接口 |

| M_AXI_DP | MB外围数据接口,可以用来连接片内的BARM,AXI-Lite类型 ,非必选 |

| M_AXI_IP | MB外围指令接口,用来挂载AXI总线形式的接口外设IP,AXI-Lite类型,必选 |

| M_AXI_DC | 外部存储器数据接口,AXI-FULL类型 ,非必选 |

| M_AXI_IC | 外部存储器指令接口,AXI-FULL类型 ,非必选 |

3. 工程搭建

- 创建一个Block Design。

- 在Block design中添加MicroBlaze IP后,双击,进入配置页。

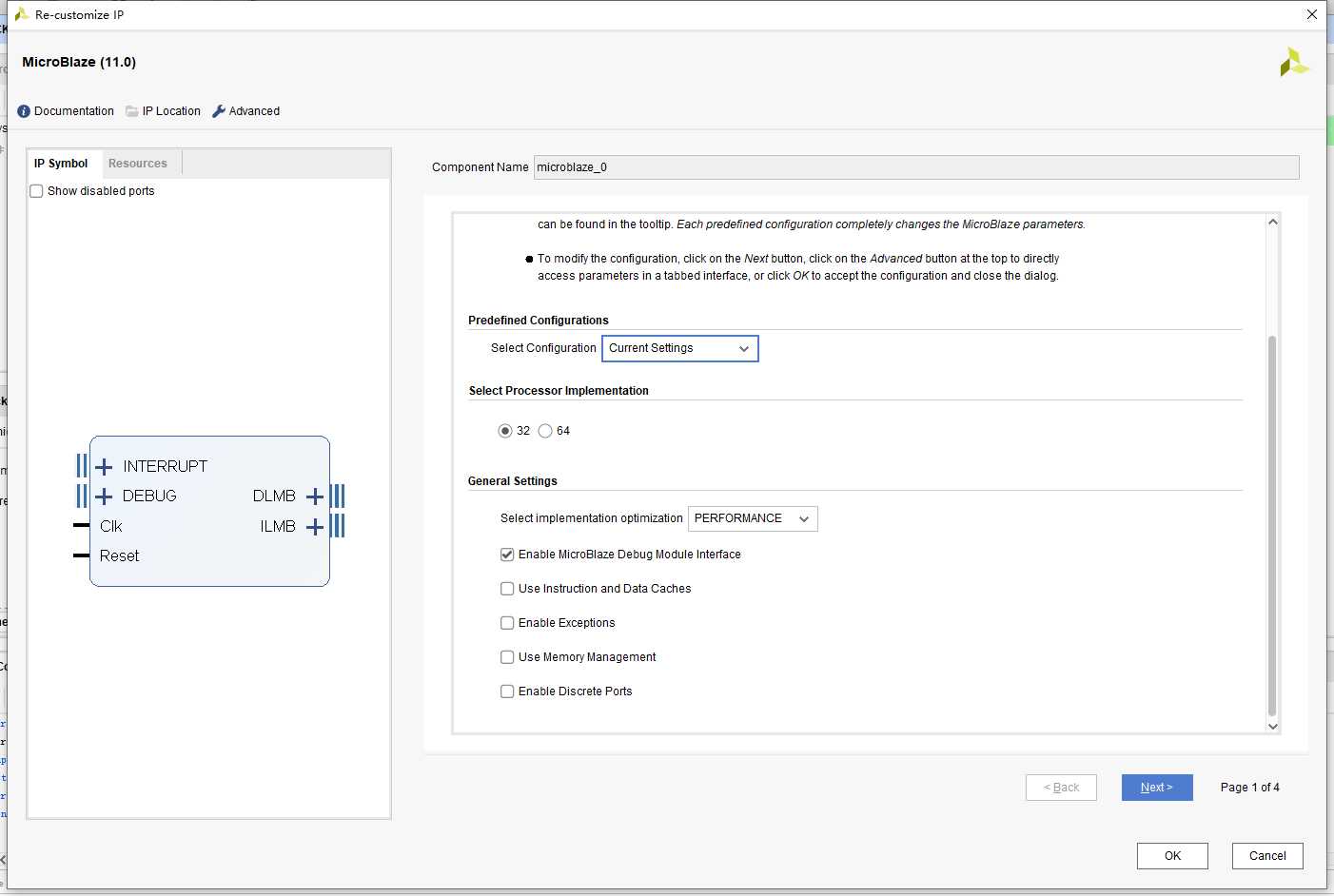

3.1 MicroBlaze IP设置

3.1.1 欢迎页

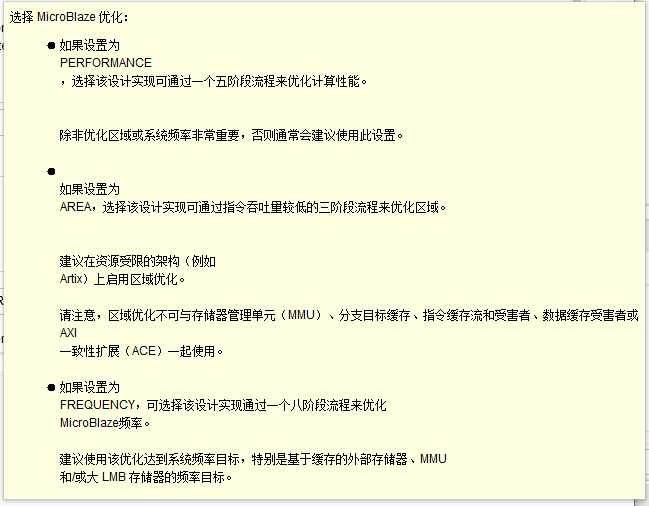

- 下面为第一页保持默认就好,模式选择PERFQRMANCE,位宽选择32位。

- 布局布线的规则,可以根据自己设计的需求来确定。通常选择PERFORMANCE即可。

- 如果要挂载外部存储器(如DDR),就要勾选Use Instruction and Data Caches。

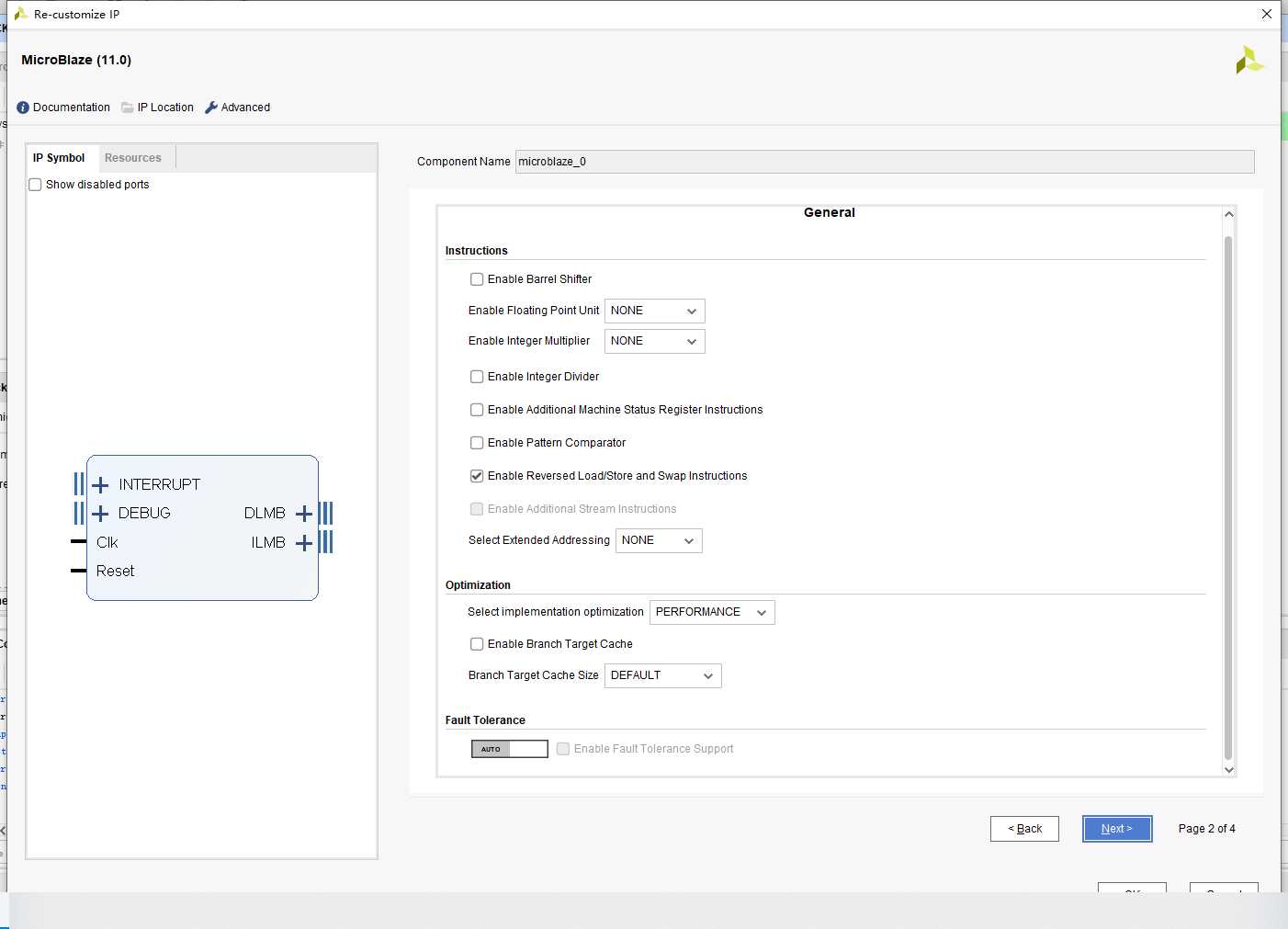

3.1.2 General和Debug

- General页和Debug页保持默认即可。

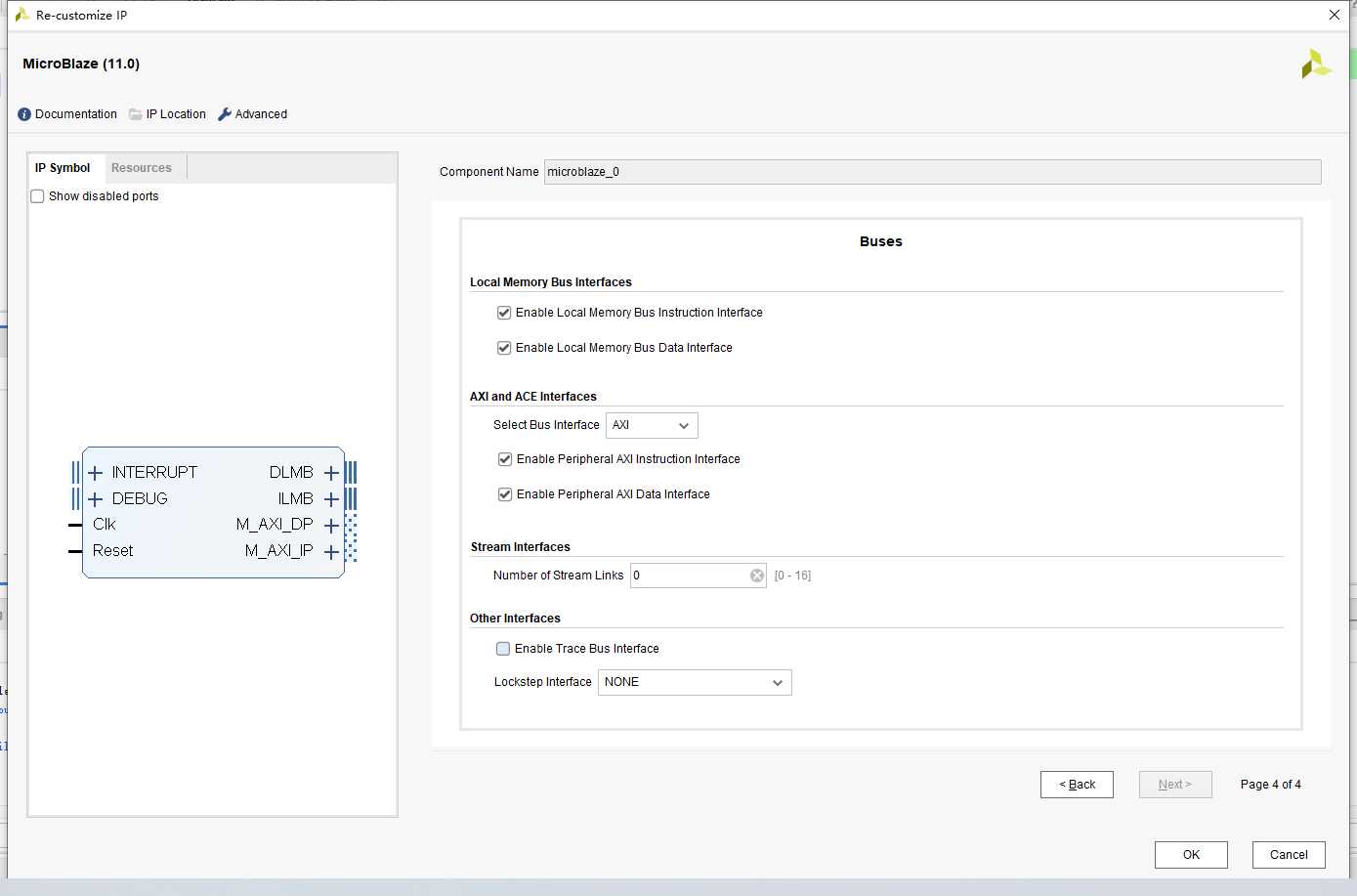

3.1.3 Buses

- 这里就是选择处理器内部存储指令接口(ILMB),处理器内部存储数据接口(DLMB),AXI指令接口(M_AXI_IP)和AXI数据接口(M_AXI_DP)的地方。按照需要选择,本设计都勾选上。

最好点击OK。

3.2 MicroBlaze互联(最小系统)

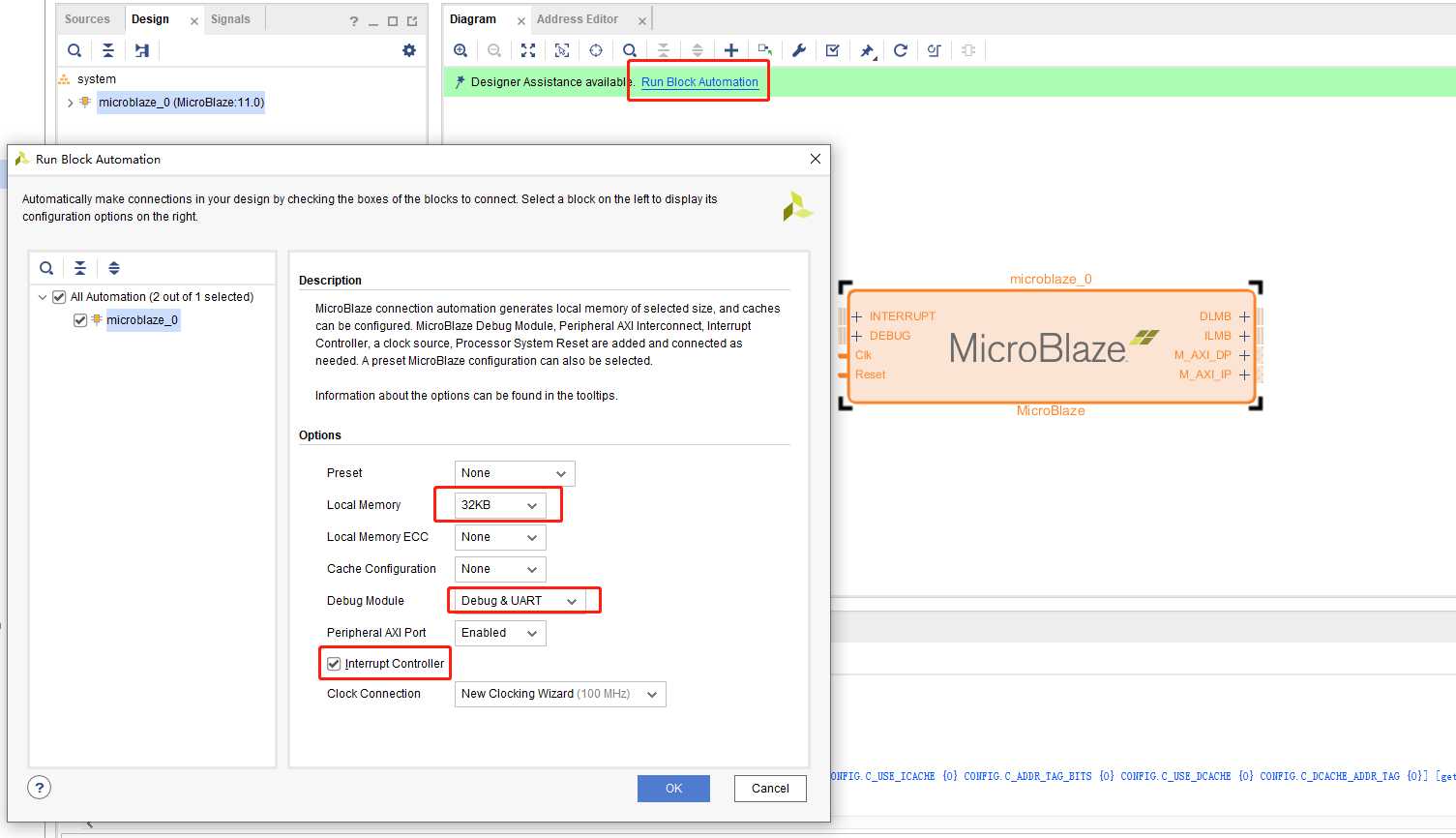

选择Run Block Automation,自动生成MicroBlaze最小系统。

配置页修改以下几个参数:

- Local Memory: 选择处理器本地内存的大小,越大越好,我们选择32K。(但是片内的BARM也是有限)

- Debug Module: 选择Debug &UART可以使用一个虚拟的调试串口,能够在SDK开发中打印部分信息,方便调试。(逻辑资源够用的时候选上就好了,会方便很多!)

- Interrupt Controller: 添加中断控制器,可以自行添加。

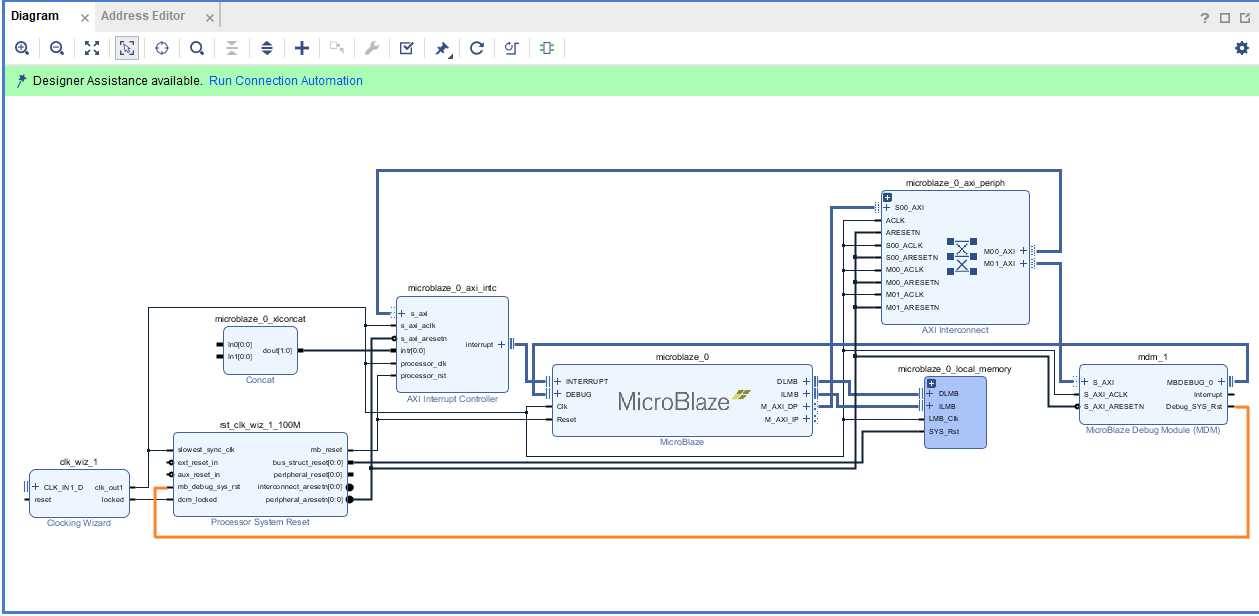

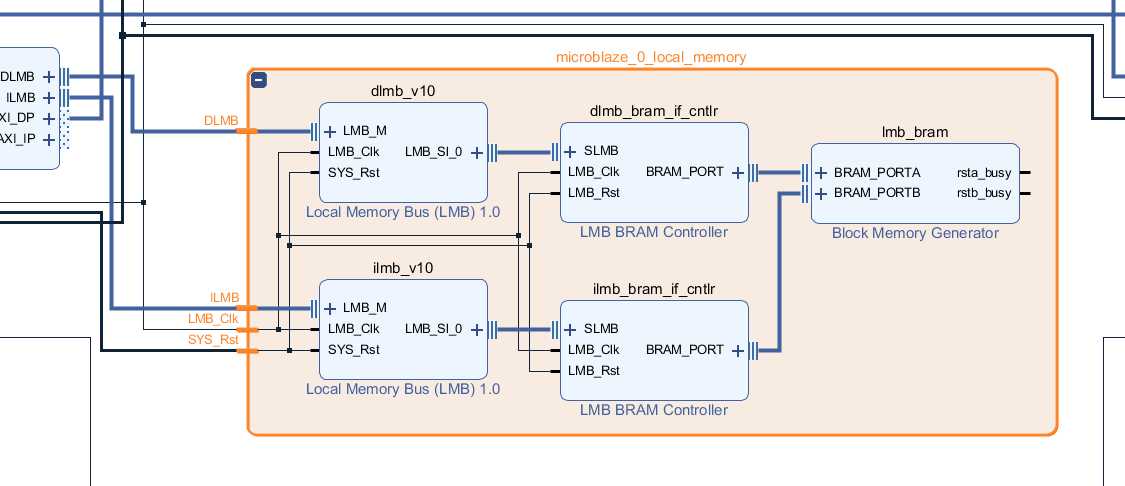

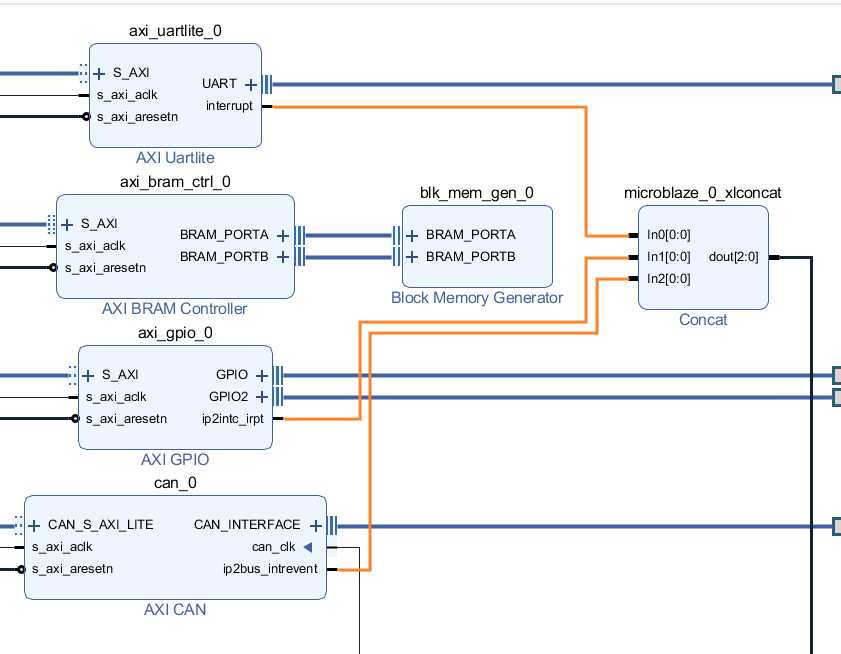

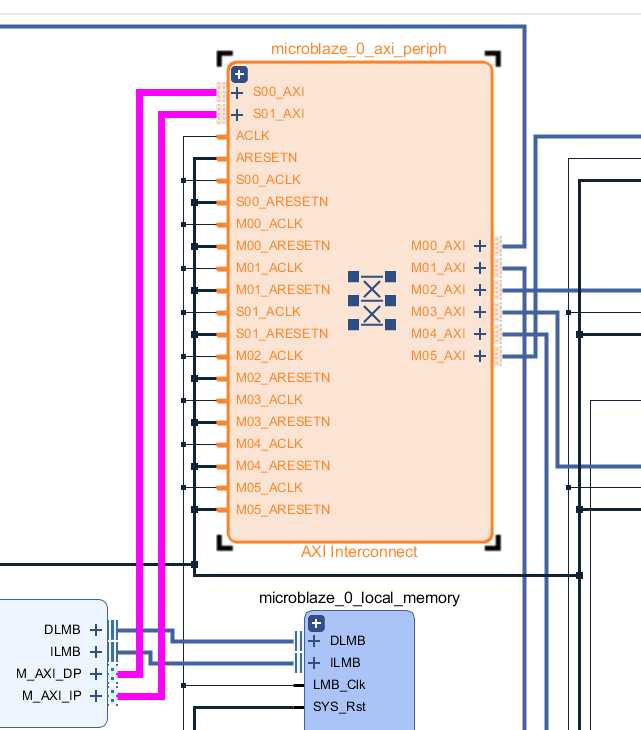

连接效果图如下:表格分别介绍图中IP的作用。

| IP名 | 作用 |

|---|---|

| Clocking Wizard | 生成时钟 |

| Processor system Reset | 生成复位 |

| Concat | 将多个信号转换成一个多位的信号 |

| AXI interrupt Controller | 中断控制器,管理中断信号,可以设置触发模式 |

| AXI interconnect | AXI连接器,连接多个AXI总线的IP,管理数据的收发,仲裁 |

| MicroBlaze Debug Module(MDM) | MB调试模块,方便进行调试。 |

| Local memory | 本地存储* |

3.2.1 By the Way

那个深蓝色的模块其实是封装起来的,可以展开看一下:无非通过两个LMB BARM Controller连接了一块BRAM。

BARM Controller的作用就是实现总线的切换,毕竟总线格式不同。

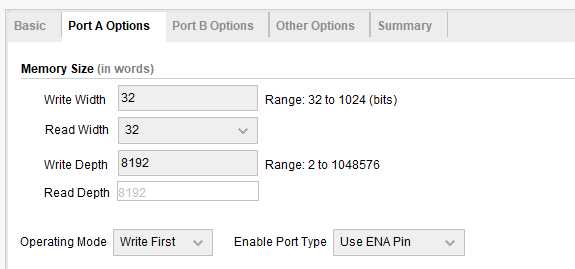

点开Block Memory Generator 发现它的大小刚好等于之前设置的值32KB。32乘以1024乘以8bit=32KB。

3.3 添加AXI 外设

这部分内容大家可以根据自己的需求和硬件进行筛选。没有硬件电路是不可能能够正常工作的。

对于MicroBlaze来说,不同的外设可能存在配置上的不同(协议不同),但是数据的读写都是对指定基地址的读写。

3.3.1 UART

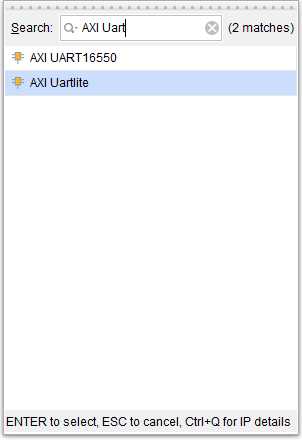

有两个IP可以选择

- AXI UART16550 可以在PS端对UART的波特率等参数进行修改。

- AXI Uartlite 参数定死无法修改。

按照需求确定,在PS端的开发略有不同。本文选择AXI Uartlite,怎么简单怎么来。

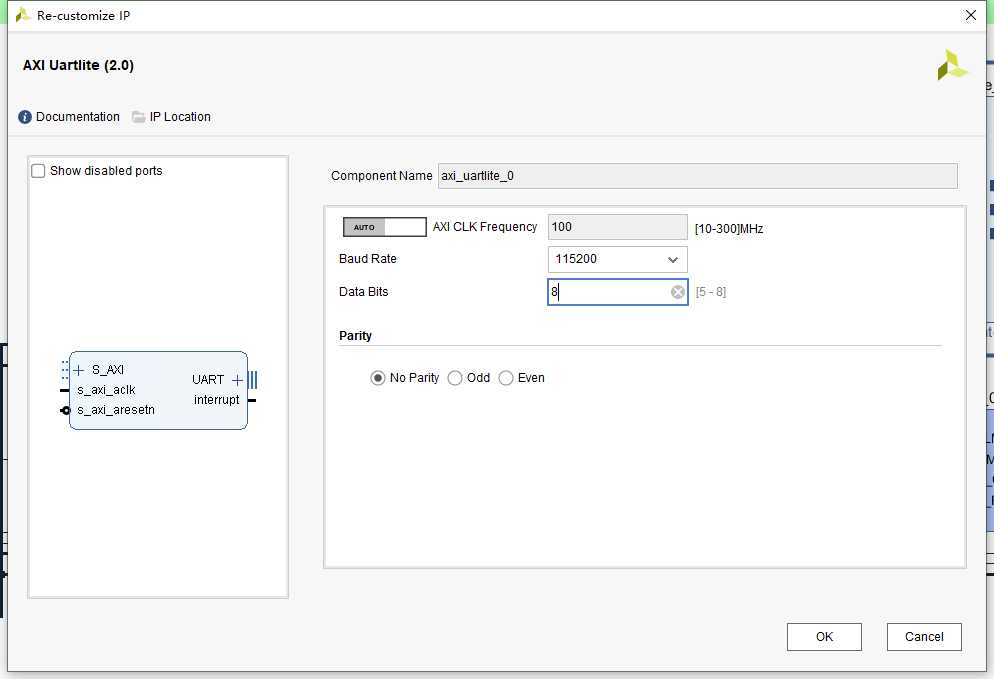

- IP配置详情页,选择时钟,波特率,数据位宽,奇偶校验。

注意:对于RS485其实也能够使用,如何处理呢,加一组AXI GPIO即可。

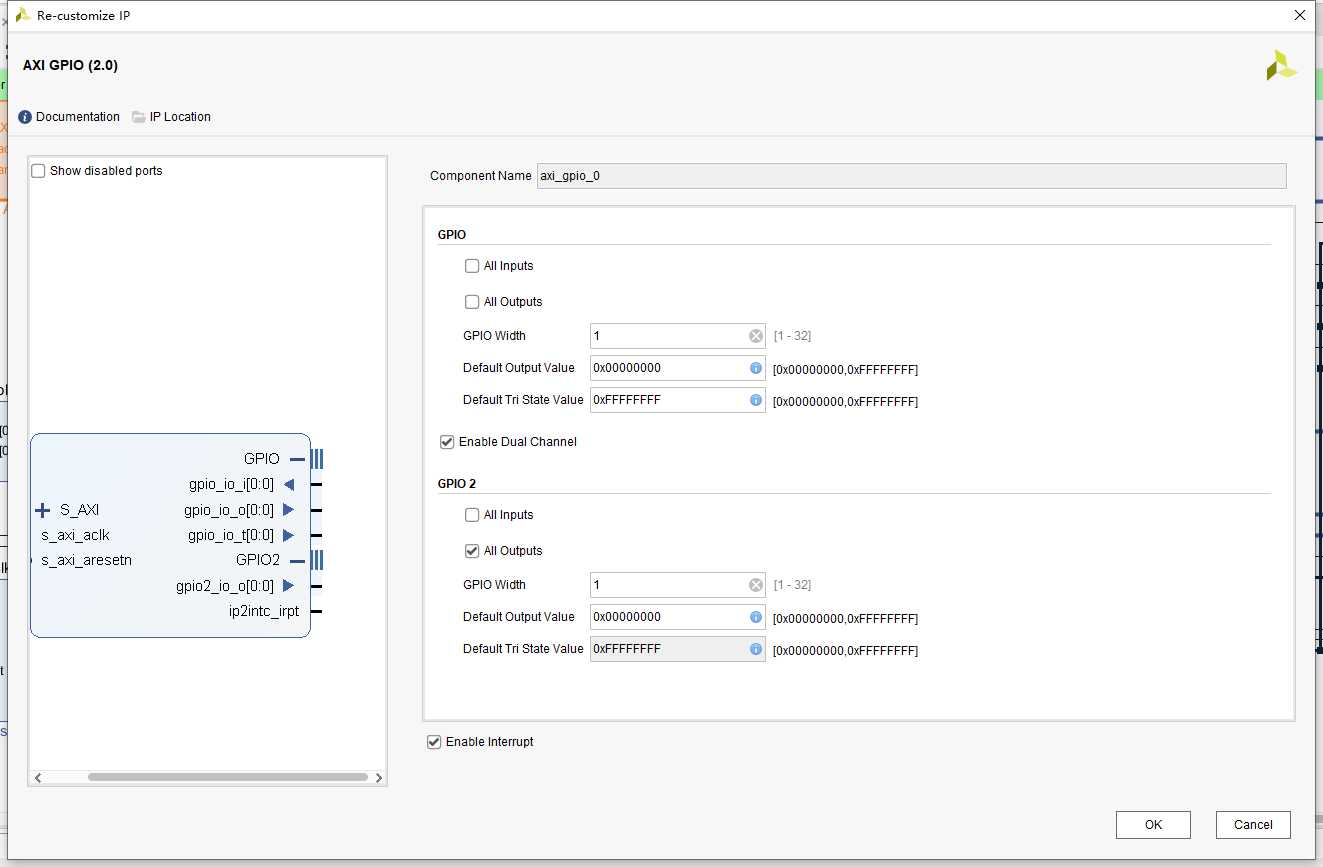

3.3.2 GPIO

AXI GPIO的配置主要由几个点。

- GPIO的类型,如果不选择All input/output,则IO的类型为inout类型,对比图如左边的展示栏。

- GPIO Width GPIO的位宽,有多少个IO选多少

- Enable Dual Channel 是否使能两个通道,按照需求选择就好。

- Enable interrupt GPIO通常是作为中断的形式使用的,一般都勾选。硬件开发要保证可能要用的时候有得用

注意:当GPIO上的电平发送变化时,IP会输出中断信号。但是是那个IO有数据进来要读数据寄存器。

-

在PS端的开发中会提到。

-

GPIO除了触发中断,很多时候还用来做按键和LED控制。

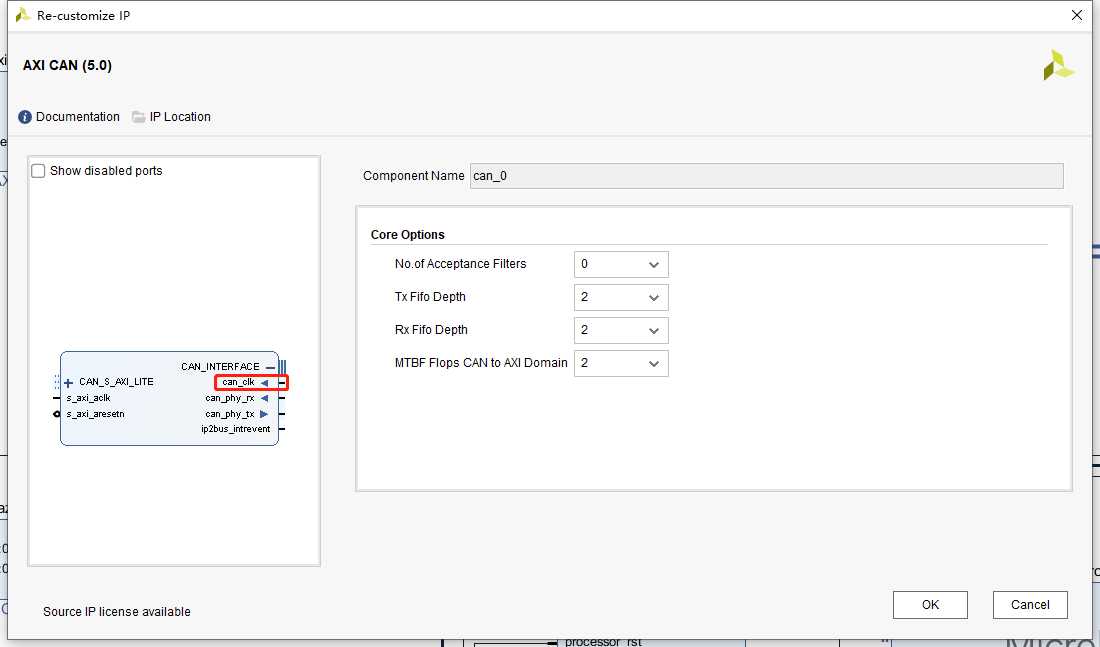

3.3.3 CAN

CAN也有多个IP,但是绝大多数场合大家应该用不到CANFD,CANFD是CAN协议的升级版,具体介绍可以查看我的另一篇博客CAN协议笔记

- 这里我们选择 AXI CAN。

- 这里可以选择CAN IP TxRx的FIFO深度,越大越好。但是我们选择2即可。

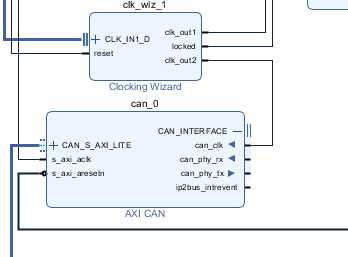

注意: CAN总线的can_clk是需要从CAN_INTERFACE输入的。根据需求选择,这个值必须被设计师确定,因为在PS端的开发中时钟的频率要被用来计算波特率,这与CAN协议有关!

懒得算的可以直接用Clocking Wizard生成一个24Mhz的时钟,因为PS端的Example使用的就是24M,相当于CAN的初始化可以直接使用Example中的设置。

3.3.4 BRAM

BRAM在FPGA有特定的资源,数量是有限的,所以我们在使用时也要注意资源的使用。

BARM的学习可以参考这篇知乎:BARM是什么-知乎

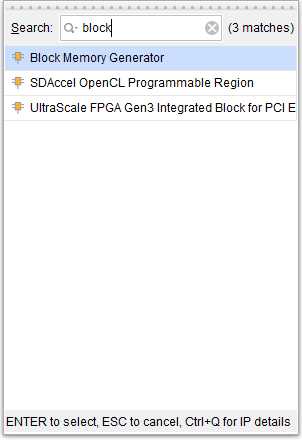

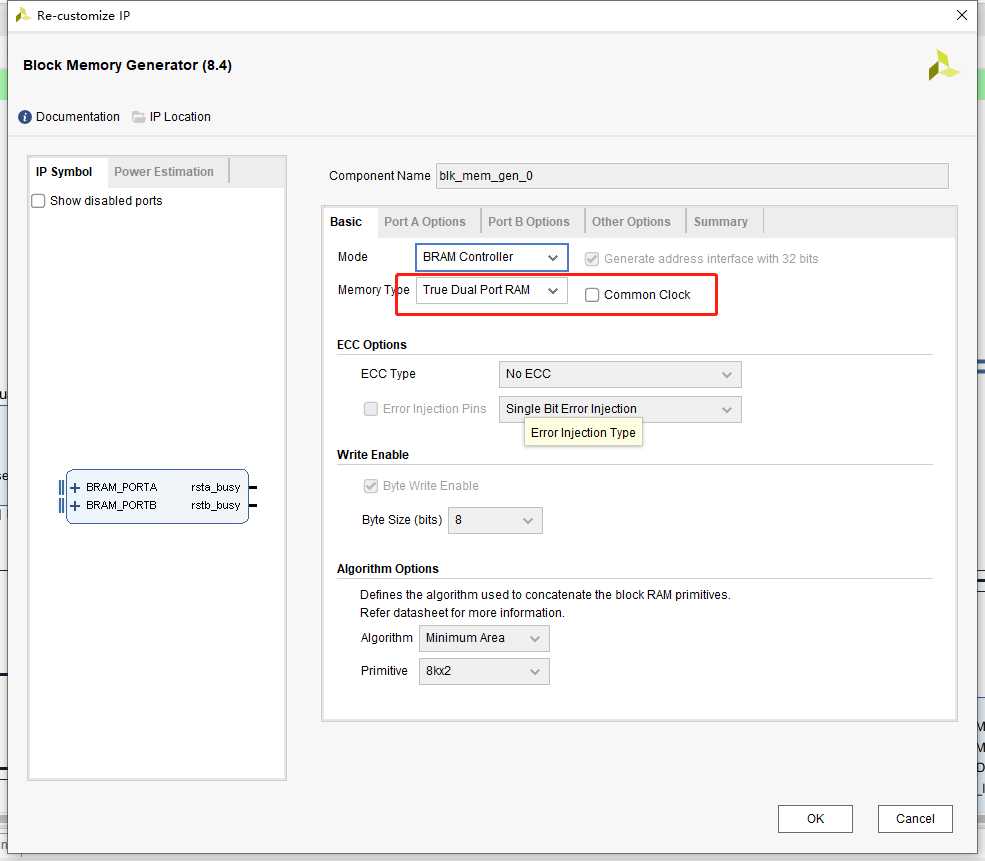

搜索Block,选择Block Memory Generator,双击进入。

通常习惯设置为真双口RAM,其余保持默认即可

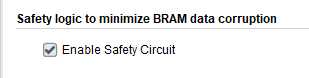

- 要想去除rsta_busy信号,可以在Other Options中取消下图的勾选。

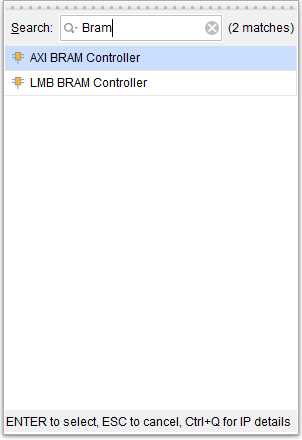

- 像之前的Local Memory一样添加一个AXI BRAM Contraller,将BARM也挂载在AXI总线上。IP设置保持默认即可。

注意:对于PS端来说,一个BARM Contraller对应一个的基地址,PS端无法控制数据从PORTA还是PORTB读出或写入数据。

这个是个人经验,之前用到多块BARM时候发现的。

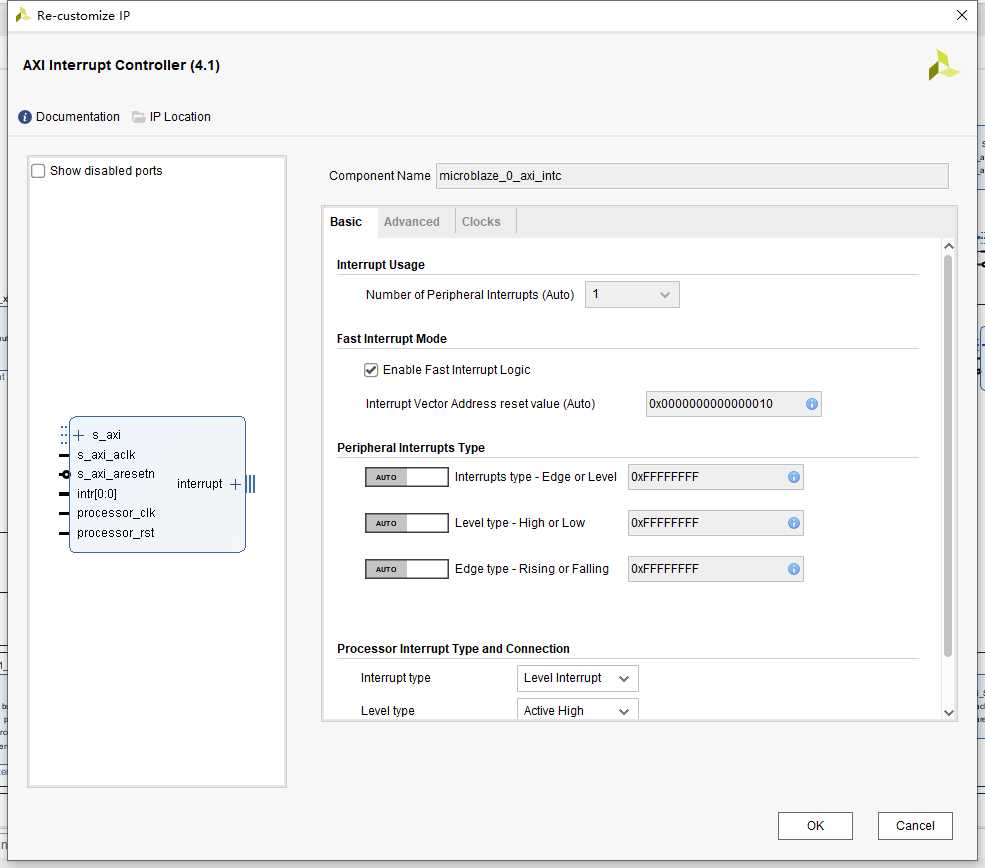

3.3.5 中断

- 点击Concat,我有三个外设,所以将number of ports修改为3。然后在将线连起来

-

点开AXI Interrupt Controller。可以选择外部输入中断的触发方式,点击AUTO开关后,可以单独进行配置,对应位为1表示前面的模式,如下图中为:Edge 触发,

高电平有效,上升沿触发。(边沿处触发时,Level的设置无效)。 -

MicroBlaze的中断方式在下面的下拉列表中选择。

注意:这里可以看到一个中断控制器最多支持32个中断,如果想要多个的话,可以采用中断控制器级联的方式

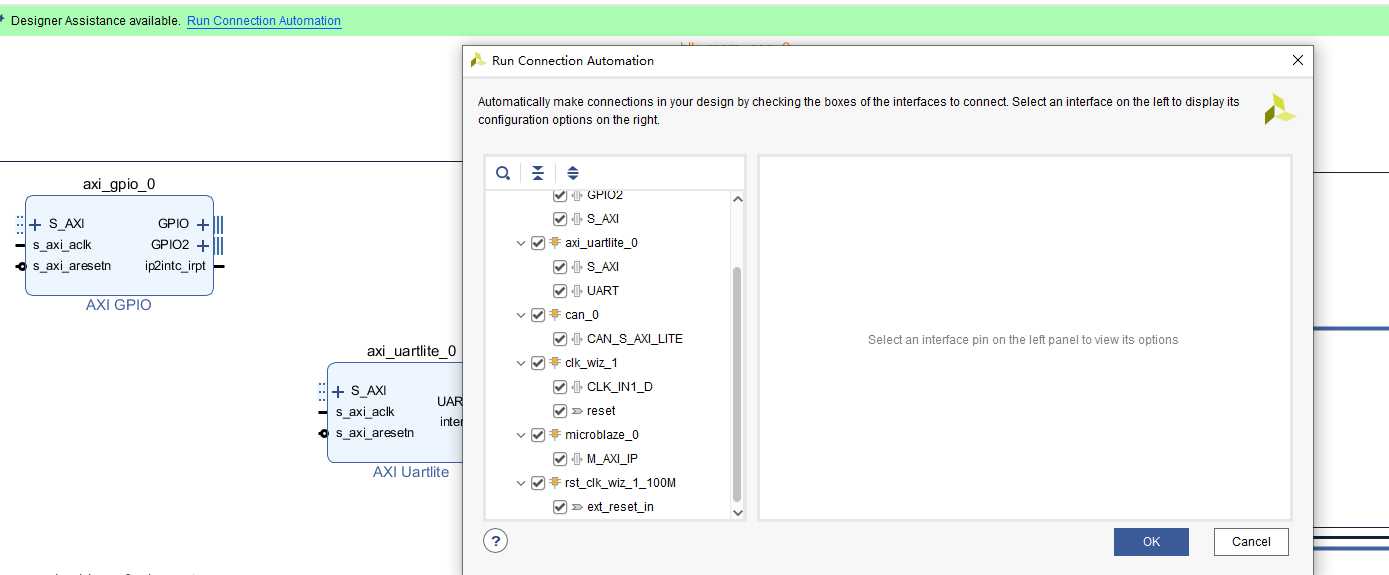

3.4 连接IP

都添加完成后点击Run Connection Automation。

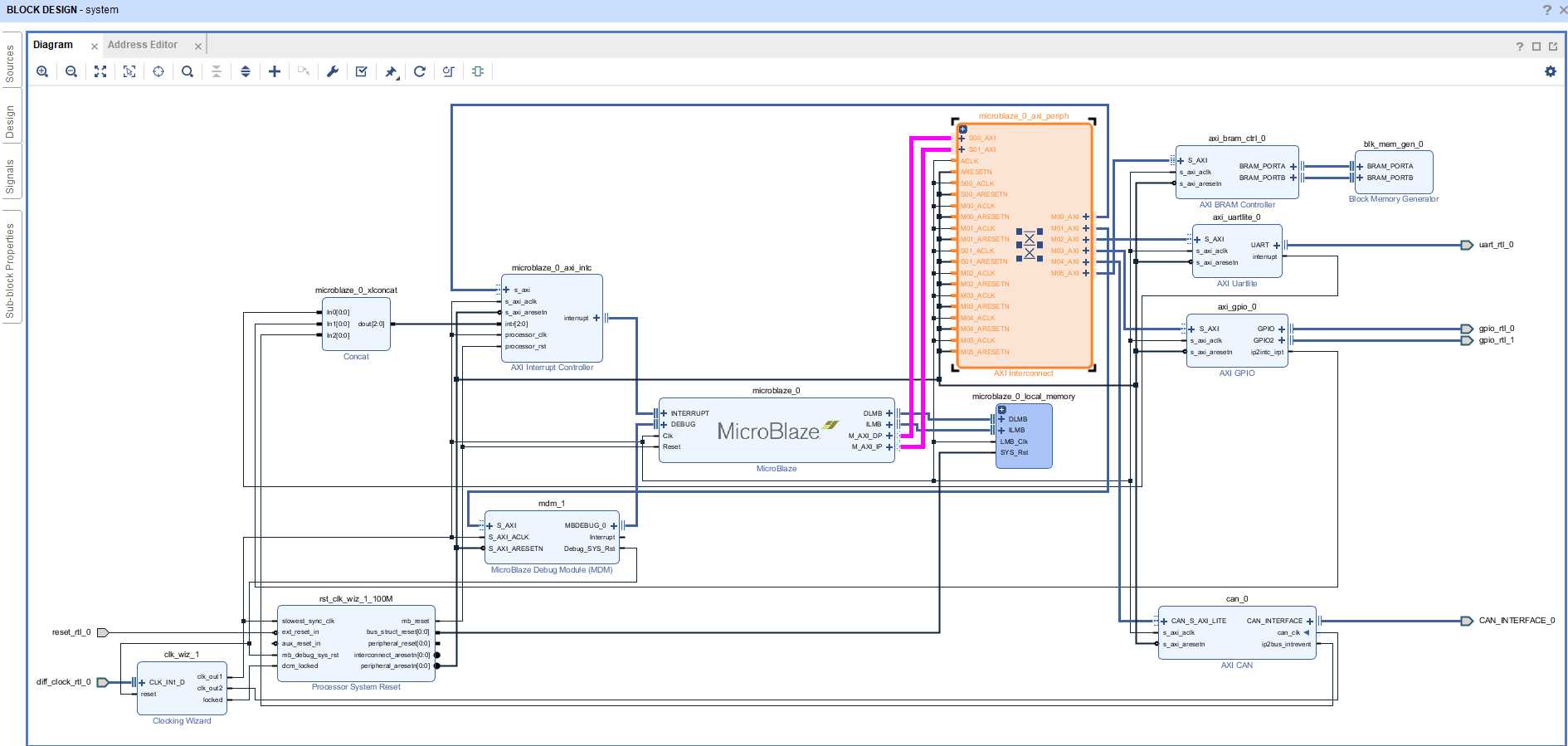

我的最终工程架构如下图:

注意:AXI总线的互联自动完成了,但是有些时候得自己连接,最好保持各个IP运行在同一个时钟域下。

- 可以清楚的看到M_AXI_DP和M_AXI_IP通过名为microblaze_0_axi_preiph的AXI Interconnect将所有外设都连接到了MicroBlaze核。

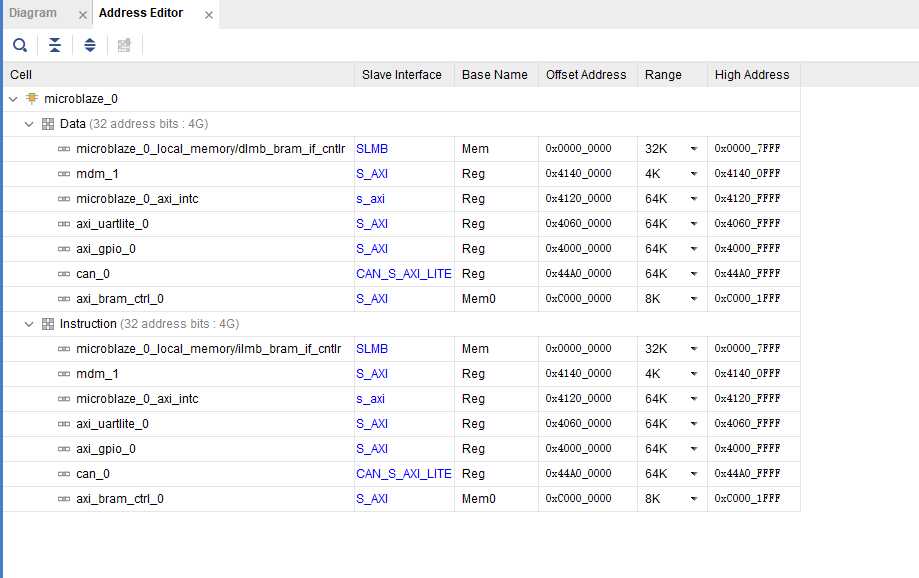

3.5 地址分配

- 最后点击Address Editor,可以看到每个外设的基地址已经被自动分配了,还是那句话,对哪个外设操作就是对哪片基地址写值。

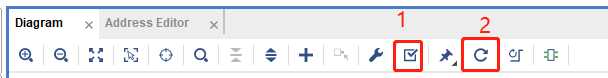

- 点击2可以自动整理设计的排版

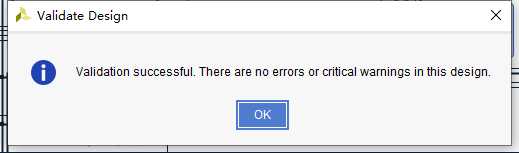

- 完成所有设计以后要点击1。完成设计的实现,这个过程可能会报错,根据提示完成修改即可。

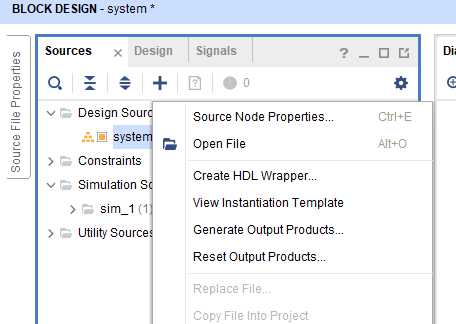

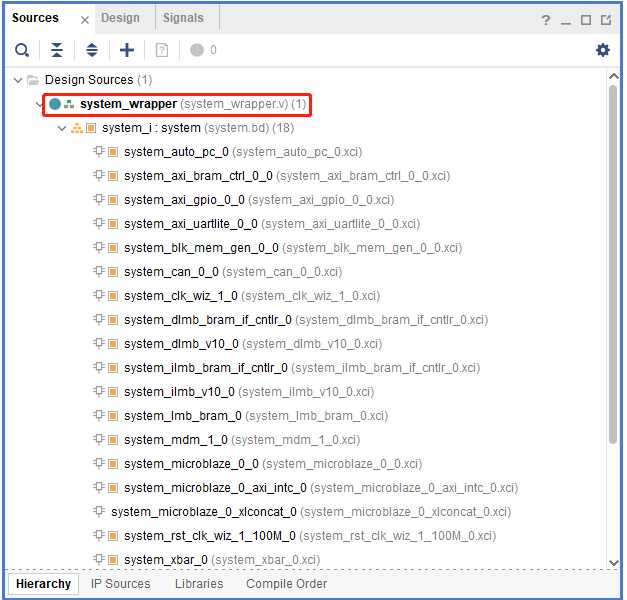

3.5 生成HDL文件

- 生成HDL Wrapper。

- 通常会在Wrapper外面再包一层,因为很多时候Block Design并不是主要的设计,还需要在外部添加一些设计。

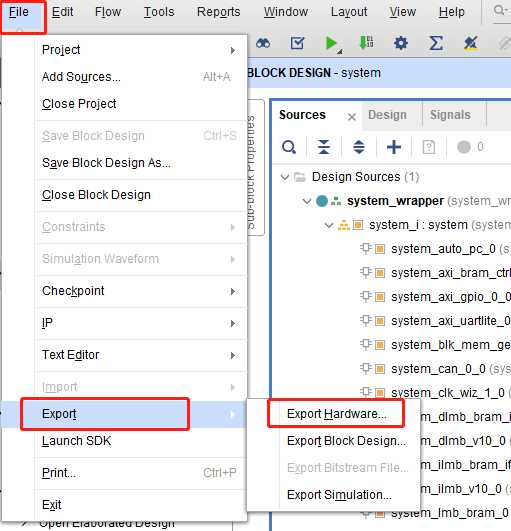

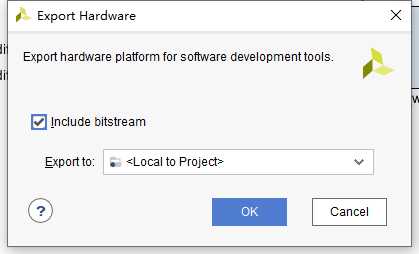

- 生成Bit文件之后,我们要导出硬件。还要勾选include bitstream。

4. 结语

PL端的开发完成后,接下来就是PS端的开发,我会在下一篇博客中进行论述。

今天的文章MicroBlaze最小系统+UART/CAN/GPIO分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:http://bianchenghao.cn/24728.html