基于《Applying Dual-Core Lockstep in Embedded Processors to Mitigate Radiation-induced Soft Errors》文章总结

RISC-V双核锁步DCLS Lockstep技术参考之前文章:

RISC-V双核锁步DCLS Lockstep技术总结_远古架构师alanwu的博客-CSDN博客https://blog.csdn.net/heyuming20062007/article/details/123329537ARM+RISC-V异构双核锁步DCLS Lockstep技术参考之前文章:

一、ARM双核Lockstep架构

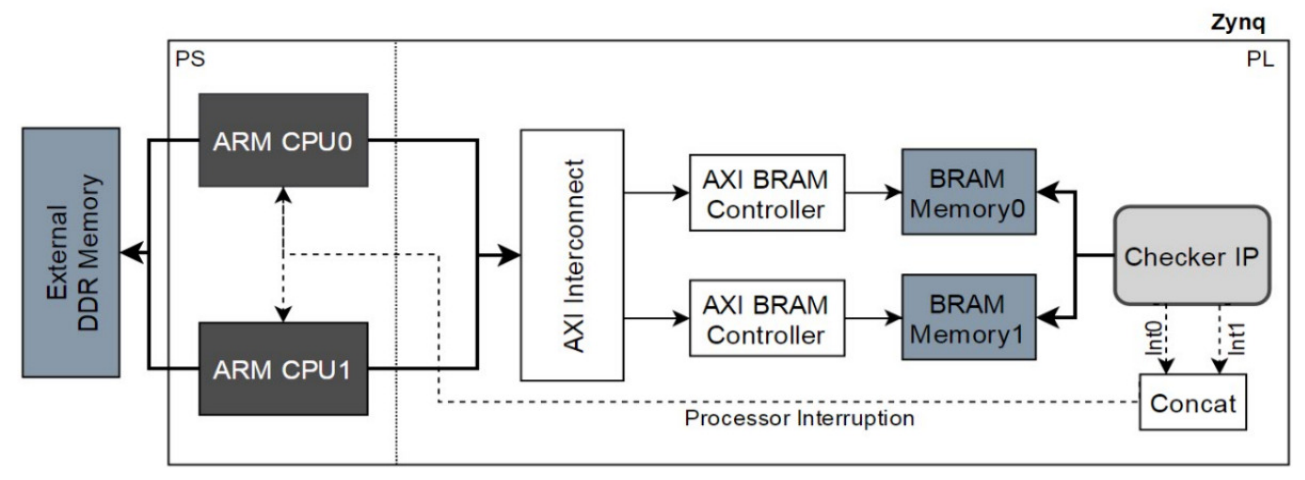

文中提出的ARM双核lockstep架构如下图所示,该架构中有两个CPU、两个BRAM、一个checker和一个DDR Memory。为了防止两个CPU同时竞争DDR中的资源,每个CPU均配置了一个最大64KB大小的BRAM。

所有的CPU输出的数据均缓存在该BRAM中,大小可根据应用程序情况配置。BRAM通过AXI总线互连,BRAM控制器用来处理AXI接口的通信。外部的DDR Memory存储了两个CPU的程序指令,尽管两个CPU运行的程序相同,但在DDR中各自存放两段不同物理地址的程序。除此之外,DDR还被用来存储checkpoint到达时的处理器内部信息,方便程序回卷。Checker用来验证对比CPU是否出错,如果出错需要通过中断及时通知两个CPU进行处理。由于cache使能将导致CPU0和CPU1输出不写穿到BRAM,从而无法保证系统的可靠性,因此该结构中的cache必须关闭使能。

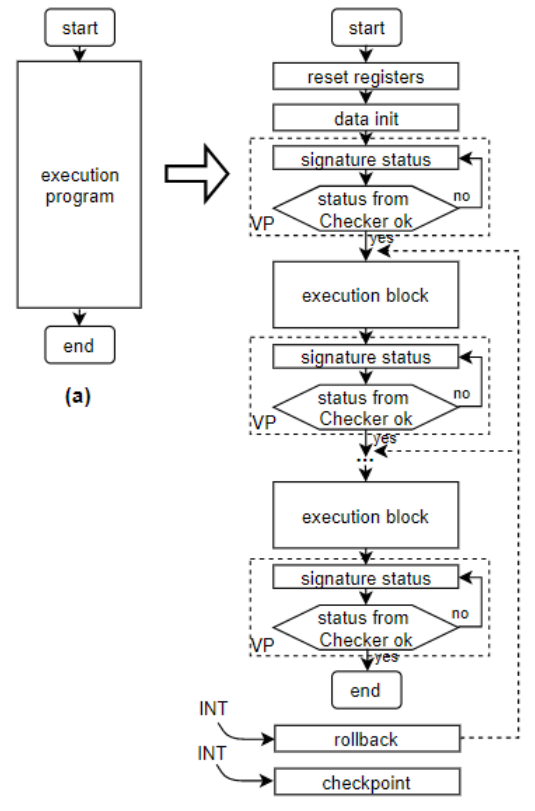

二、程序执行过程

带有lockstep的程序流程如下图b所示,a为原始不带lockstep功能的程序。所有a中execution program将全部放入execution block中,中间通过VP(Verification Point)隔断。复位完成后,程序会对数据和寄存器进行初始化,然后会进入VP程序,此时程序会被stall住。VP阶段首先会发送程序的应用签名,该方法在应用程序上附加代码,通过计算发送给BRAM用于Checker对比。签名值是当前CPU状态和内部信息的表征,可以通过校验位、XOR掩码等方式计算得到,能够使用的处理器内部信息包括CPU内部寄存器:R0-R12;SP;LR;PC等。

使用中断机制来访问处理器内部信息,由于中断过程会将寄存器的值存储在堆栈中,这样中断服务程序可以方便的观察checkpoint时的寄存器数值差异。当CPU接收到中断后,将会执行下述步骤:

- 实际的执行程序会被中止;

- 处理器的寄存器数值保持到堆栈中,执行程序现场被保存;

- 中断服务程序被执行;

- 中断服务程序结束时,处理器从堆栈中恢复现场;

- 继续执行程序。

在VP阶段时,Checker产生中断进入中断服务程序,然后等待BRAM中的数据ready,随后完成两个BRAM中的应用签名对比或寄存器数值对比。如果对比没有错误,表示当前两个CPU运行一致,继续执行下一段程序直到checkpoint。如果对比错误,则Checker会产生错误异常中断,告知CPU回卷程序并恢复之前程序。在Checker对比完成后,Checker会将对比结果重新写回BRAM来解锁程序,让程序继续执行。

三、Checker模块

Checker使用RTL硬件实现,负责对比程序一致性和控制lockstep前进。为了识别是否有错误,Checker会比较两端CPU的所有输出。对比可以使用两种方法实现:一种是对比所有CPU输出到BRAM中的数据;另一种是只对比应用签名。如果使用前者,对比过程可能需要更多的硬件逻辑来实现,但能保证所有数据没有错误;如果使用后者,需要提前计算好应用签名,但能够有效的提高对比速率和降低硬件逻辑资源。

四、检查点和回卷操作

当Checker验证系统出错时,它会产生中断请求CPU访问BRAM,并修改CPU堆栈内容。根据是否允许访问DDR,将回卷过程分为两种:

- 只允许访问BRAM:处理器内容只保持在BRAM中,回卷时会将BRAM中的数值覆盖CPU内部寄存器。

- 可访问BRAM和DDR:CPU信息会同时存入BRAM和DDR中,回卷时首先从BRAM中读取信息覆盖CPU内部寄存器,如果多次回卷仍然无法通过该checkpoint,那么程序会启动去DDR读取信息。

如果程序连续出现两次回卷,且中间没有checkpoint,则表明checkpoint出现了错误。如果多次尝试失败,此时系统需要恢复到第一次保存的程序位置,从数据初始化完成后重新运行程序。如果还是不能解决问题,那么需要产生硬件复位重新初始化两边寄存器和程序数据。

五、设计总结

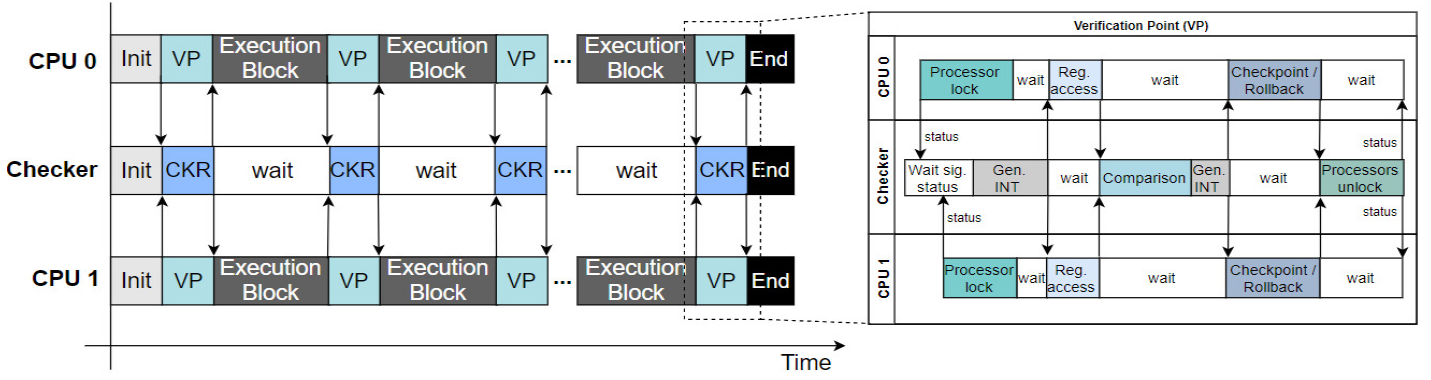

上图是整个过程的总结,程序的整个流程如上左图所示,其中VP阶段的具体流程如上右图所示。

今天的文章ARM双核锁步DCLS Lockstep技术研究(FPGA实现)分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/4704.html

https://blog.csdn.net/heyuming20062007/article/details/123400073

https://blog.csdn.net/heyuming20062007/article/details/123400073