一、电路-版图-掩膜-光刻之间关系

1.什么是版图

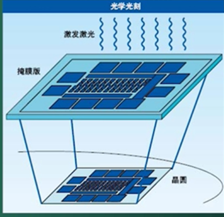

集成电路制造工艺中, 通过光刻和刻蚀将掩膜版上的图形转移到硅片上。这种制造集成

电路时使用的掩膜版上的几何图形定义为集成电路的版图。

集成电路制造厂家根据版图提供的信息来制造掩膜( Mask )

所以,版图是从设计走向制造的桥梁。

2.掩膜的作用

掩模是用来制造集成电路的。掩膜上的图形决定着芯片上器件或连接物理层的尺寸。

因此版图上的几何图形尺寸与芯片上物理层的尺寸直接相关。

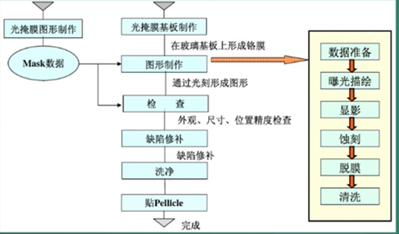

图形数据:版图的gds数据

掩膜制作流程

(一般有20层mask)

3.光刻:图形转移到晶圆上。

是对半导体晶片表面的掩蔽物(如二氧化硅)进行开孔,以便进行杂质的定域扩散的一种加工技术。

二、版图设计与验证

1.版图设计环境

建立数据库通道,确定版图与工艺对应关系。

2.芯片版图布局

■布局图应尽可能与电路图一致。

■设计布局图的一个重要的任务是安排焊盘。

■集成电路必须是可测的。

3.基于版图设计EDA工具设计版图的基本步骤:

1 )运行版图编辑工具,建立版图文件;

2 )在画图窗口内根据几何参数值调元器件和子单元的版图;

3 )在不同的层内进行元器件和子单元之间的连接;

4 )调用DRC程序进行设计规则检查,修改错误;

5 )调用电路提取程序提取版图对应的元件参数和电路拓扑;

6)与分析阶段建立的电路图文件结合进行版图与电路图对照分析,即LVS

( Layout-vs-Schemetic ) ;

4.注意:

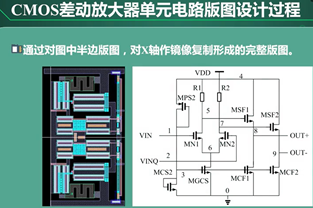

(1)在正式用Cadence画版图之前,一定要先构思,也就是要仔细想一想,每个管

子打算怎样安排,管子之间怎样连接,最后的电源线、地线怎样走。

(2)对于差分形式的电路结构,最好在版图设计时也讲究对称,这样有利于提高电路性能。

为了讲究对称,有时候需要把一个管子分成两个,比如为差分对管提供电流的管子就

可以拆成两个、四个甚至更多。

(3)差分形式对称的电路结构,一般地线铺在中间,电源线走上下两边,中间是大片的元件。

(4)当采用的工艺有多晶硅和多层金属时,布线的灵活性很大。一般信号线用第

一层金属,信号线交叉的地方用第二层金属,整个电路与外部焊盘的接口用第三

层金属。但也不绝对,比如说某一条金属线要设计允许通过的电流很大, 用一条

金属线明显很宽,就可以用两条甚至三条金属线铺成两层甚至三层,电流在每一

层金属线上流过去的量就小了二分之一。层与层是通过连接孔连接的,在可能的

情况下适当增加接触孔数,确保连接的可靠性。

(5)输入和输出最好分别布置在芯片两端,例如让信号从左边输入,右边输出,这样可以

减少输出到输入的电磁干扰。对于小信号高增益放大器,这一点特别重要,设计不当会

引起不希望的反馈,造成电路自激。

(6)应确保电路中各处电位相同。芯片内部的电源线和地线应全部连通,对于衬底应该保

证良好的接地。

(7)对高频信号,尽量减少寄生电容的干扰,对直流信号,尽量利用寄生电容来旁路掉直

流信号中的交流成分从而稳定直流。第一层金属和第二层金属之间,第二层金属和第三

层金属之间均会形成电容。

(8)对于电路中较长的走线,要考虑到电阻效应。金属、多晶硅分别有各自不同的方块电

阻值,实际矩形结构的电阻值只跟矩形的长宽比有关。金属或多晶硅连线越长,电阻值

就越大。为防止寄生大电阻对电路性能的影响,电路中尽量不走长线。

(9)图形应尽量简捷,避免不必要的多边形,对连接在一起的同一层应尽量合并,这不仅可

减小版图的数据存储量,而且使版图一目了然。

(10)设计者在构思版图结构时,除要考虑版图所占的面积、输入和输出的合理分布、减小不

必要的寄生效应还应力求版图与电路原理框图保持一致(必要时修改框图画法) , 并力求版图美观大方(利用适当空间添加标识符)。

5.验证及检查

( 1 )设计规则检查DRC ;

(2)电路提取;

(3 )电气规则检查ERC ;

(4 )版图与电路图对照LVS ;

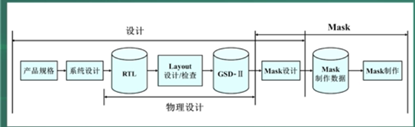

(5)版图数据输出:经过版图检查完全无错,将版图数据转换成GDS-1I格

式的码流数据,按照Foundry的要求或MPW要求,通过网络传送GDS-II文

件(一般为FTP )。

三、设计规则与图元

1.IC版图设计的主要是运用EDA设计工具,进行集成电路后端的版图设计和验证,最终生成送交供集成电路制造用的GDSII数据。

2.版图设计就是根据产品前端设计电路或文件要求,按照工艺设计规则,设计产品的版图;完成用于生产加工的产品最终设计。

3.

设计规则检查DRC ( Design Rule Check )

电气规则检查ERC ( Electrical Rule Check )

重版图与电路图对照LVS( Layout Versus Schematic )

重版图寄生参数提取LPE( Layout Parameter Extraction )

寄生电阻提取PRE( Parasitic Resistance Extraction )

4.设计规则

最小宽度

最小间距

最小交叠

5.版图图元

电路所涉及的每一种元件都是由一套掩模决定的几何形状和一系列物理、化学和机械

处理过程的一个有机组合。

举例:

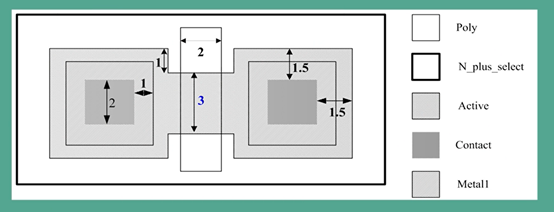

1). NMOS和PMOS

多晶硅( Poly )形成MOS管的栅极。N+扩散和有源区( Active )共同形成N型有源

区( NMOS ) , P+扩散和有源区共同形成P型有源区(PMOS)。

有源区分别在栅极两侧构成源区(S)和漏区(D)。

源区和漏区又分别通过接触孔( Contact )与第一层金属( Metal1 )连接构成源极和漏极。

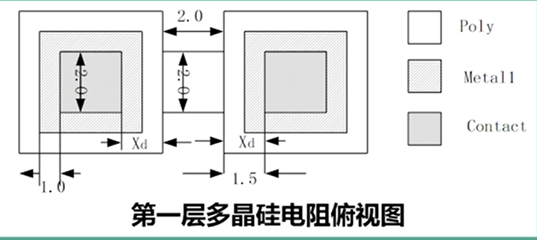

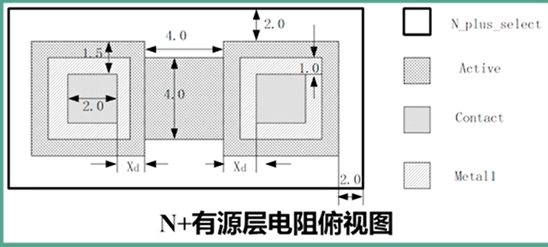

2).电阻resistor

多晶硅电阻、有源层电阻和阱区电阻

■其中, Rsh为方块电阻值, l和w分别是体电阻的长与宽, Rcom是单个接触区形成的电阻值,n是接触孔数。

■电阻的可变参数:电阻宽度( width)、电阻值®

由N+扩散与有源区形成N+有源层电阻。有源层通过接触孔与第一层金属连接,金属构成有源层电阻的两个电极。

N+有源层电阻的方块电阻值为79.1欧姆,每个接触孔形成的电阻为54.8欧姆。电阻一般为几百到几干欧姆。

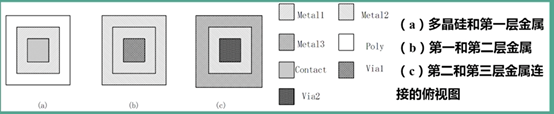

3)电容capacitance

三层介质组成:

导电层作为下电极;

绝缘层作为平板电容两电极间的介质;

导电层作为上电极。

4)互联interconnect

不同导电层之间由绝缘介质隔离。导电层之间的相互连接需要通过打孔实现。

有源层、多晶硅( Poly )和第二层多晶硅( Electrode )都通过接触孔( Contact )与第一层金属( Metal1 )连接。

5)焊盘pad

电路的输入和输出需要通过适当的导体结构(焊盘)来实现与外部电路的连接,它同时

用于电路的在芯片测试。焊盘的尺寸通常远大于电路中其它的元器件,焊盘的尺寸是固定的。

今天的文章版图设计_版图设计工具分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/53385.html