Verilog HDL 的基本功能之一是描述可综合的硬件电路。

HDL语言的三大特点:互连(Connectivity):wire型变量描述各个模块之间的端口与网线的连接关系。

并发(concurrency):可以有效地描述并行的硬件系统,除了initial语句块内的语句是顺序执行的,其余的语句都可以认为并发执行的。

时间(time):定义了绝对和相对的时间度量,如有延时的阻塞赋值和非阻塞赋值。

只有四个关键字可综合:always、if-else、case、assign。除此之外的其他关键字可以用于写testbench。

可综合语法与硬件的映射关系:

1、 if-else通常会被逻辑综合为多路选择器,使用if…else if…else if…可以建立无优先级的判断语句,而使用if…if…if…会建立有优先级的语句,对于到达时间不同的信号可以使用有优先级的语句。

2、 case是无优先级的判断语句,与单if语句相比,case的条件互斥,多用于译码电路。在verilog语言中,case和if语句需要放在always语句块中,不可以单独使用。

3、 assign为连续赋值语句,实际上是连续驱动的过程,不管等式右边各变量的值如何变化,该驱动过程是一直存在的。

4、 always语句既可以综合为组合逻辑,也可以综合为时序逻辑,具体要看括号内的敏感信号列表。所有的组合逻辑或锁存的 always 结构必须有敏感信号列表。这个敏感信号列表必须包含所有的输入信号。 综合过程将产生一个取决于除敏感列表中所有其它值的结构,它将可能在行为仿真和门级仿真见产生潜在的失配。

注意事项:

1、 (latch)在使用if或者case语句时,注意要将敏感信号所有的可能都列出来,否则会产生latch,除非特殊用途,一般电路里不要引入latch。解决方法有,使用完备的if..else语句,case语句要加上default操作,仔细检查综合器生成的报告,latch会以warning的形式报告出来。

2、 (load)在电路设计的过程中, 如果发现某个电路的负载比较多,则可以通过逻辑复制,降低关键信号的扇出,进而降低该信号的传播延迟,提高电路性能。

3、 (area)如果我们发现电路中存在较多的公共单元,也可以通过资源共享的方式,减小面积。但是,一般来说,共享会导致性能下降,所以还要根据性能和面积进行取舍。

4、 (time)在设计电路的时候,我们也可以根据数据的延迟,对这些资源进行顺序重排,降低传播延迟。例如A 信号到来比较晚,我们就可以把它尽可能放到后面,隐藏其延迟。

5、 最后一个小建议。在代码书写过程中,尽可能使用 always 描述电路, assign 仅仅用来连线。少用:?这种形式,因为这种形式通常难以阅读,且多层嵌套后很难被综合器解释。

6、 在时序电路中必须使用非阻塞赋值(<=),组合逻辑电路必须使用阻塞赋值(=),这个一定要注意,严格按这个要求写。分开异步逻辑与同步逻辑。 避免综合和静态时序时碰到问题,简化约束和编码难度。

7、 分开控制逻辑和存储器, 建议控制逻辑和存储器逻辑分成独立的模块。通常来说,存储器是用 memory compiler 生成的,其综合方式与 RTL 代码不同,所以混在一起,不利用综合,不利于很方便地更换工艺库和平台。

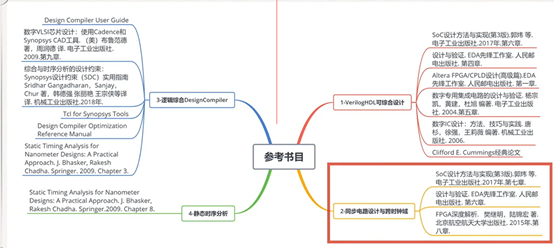

参考书籍:

参考课程:

西南交通大学邸志雄老师MOOC

今天的文章第二章——HDL语言学习笔记分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/55019.html