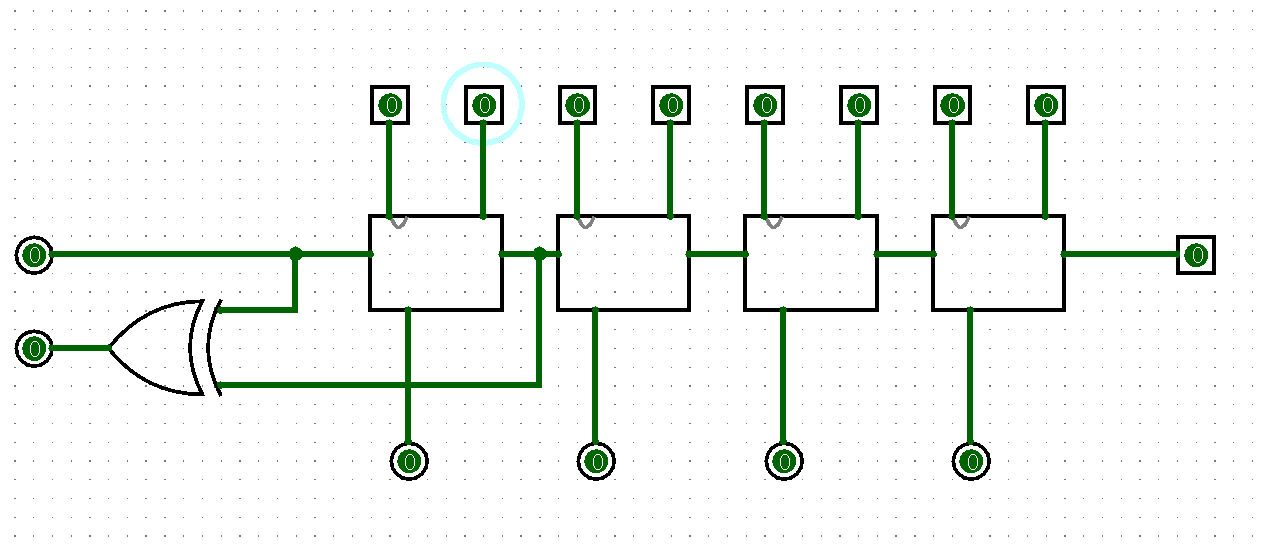

采用这篇博客里制作的全加器:

全加器

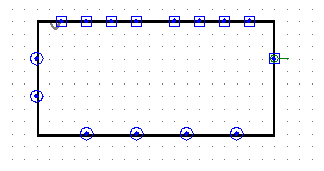

下面是电路元件外观:

上面的8个输入引脚是对应着输入的两个二进制数。没有按照电路图的顺序排列,而是按照数排列的。

比如说,电路里的是A3, B3, A2, B2, A1, B1, A0, B0,则外观图中是A3, A2, A1, A0, B3, B2, B1, B0。

A3~A0 组成一个数, B3~B0 组成一个数。

右边的一个引脚对应着输入的Cin进位。

左边的两个输出引脚代表了输出的Cout和V。

Cout是计算的进位,无符号数Cout进位即可表示溢出;V在有符号数进位时表示溢出。

下面的四个输出引脚分别代表了计算结果的4位S3、S2、S1、S0。

今天的文章四位行波加法器真值表_数字逻辑原理与FPGA设计分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/58150.html