[文献名] R. H. Krambeck, C. M. Lee, and H.-F. S. Law, “High-speed compact circuits with CMOS,” IEEE Journal of Solid-State Circuits, vol. 17, no. 3, pp. 614–619, Jun. 1982.

[相关观点]

(1)引文:指出了CMOS中有效的逻辑函数所使用的晶体管重复了一次,指出了这样设计逻辑阵列的好处是当输出或输入改变信号时没有电流从高电轨流向地,因此没有功耗消耗。这样使用CMOS设计的话其输入电容相对于伪NMOS或NMOS电路来说将会有相当可观的增量,而且,P型MOS管一般需要2倍于N管的面积去维持上升/下降时间的平衡,最后是导致总的栅电容变为3倍多。

尽管看起来伪NMOS或NMOS的速度会比CMOS快,但是由下拉时上拉网络总是导通,这样就会导致下拉网络变慢,最终两者的速度将会趋向接近。

(2)动态电路:动态电路都有一些共同的基本特征:对节点充电至一个特殊的电平在此期间改变输入的有效状态,然后时钟驱动上拉网络关闭并导通到地的路径,以此进行求值。

这样,输入的电容就可以与伪NMOS相比且提供全下拉电流,另外,也没有了静态电流的路径。

对于4相动态伪NMOS来说,时钟间隔必须足够长以使单级电路有效,因此各级存在客观的死区时间。

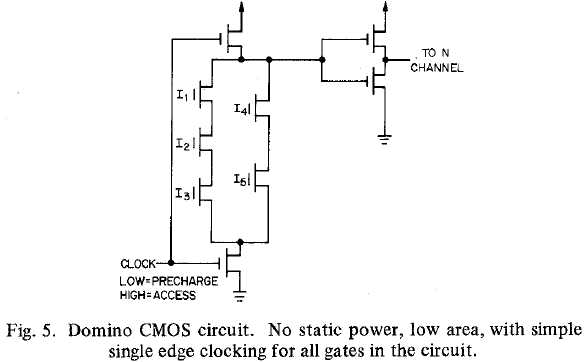

(3)多米诺电路:本文所设计的多米诺动态电路如下图所示:

电路的结构如图所示,由经典动态电路和一个反相缓冲器串接而成,动态电路的输出端接入反相器的输入端。当前端的动态电路进行预充电后,经反相器功能输出一个低电平。求值阶段,,某一输输入跳转为高电平后导致该电路输出变为高电平,引发“多米诺效应”,以模块的总延时作为时钟设计的参考。

多米诺电路的优点:没有静态功耗,低面积消耗,只需要简单的时钟沿触发。缺点:没有反相输出。

[文献名] L. Heller, W. Griffin, J. Davis, and N. Thoma, “Cascode voltage switch logic: A differential CMOS logic family,” in Solid-State Circuits Conference. Digest of Technical Papers. 1984 IEEE International, 1984, vol. XXVII, pp. 16–17.

[相关观点]

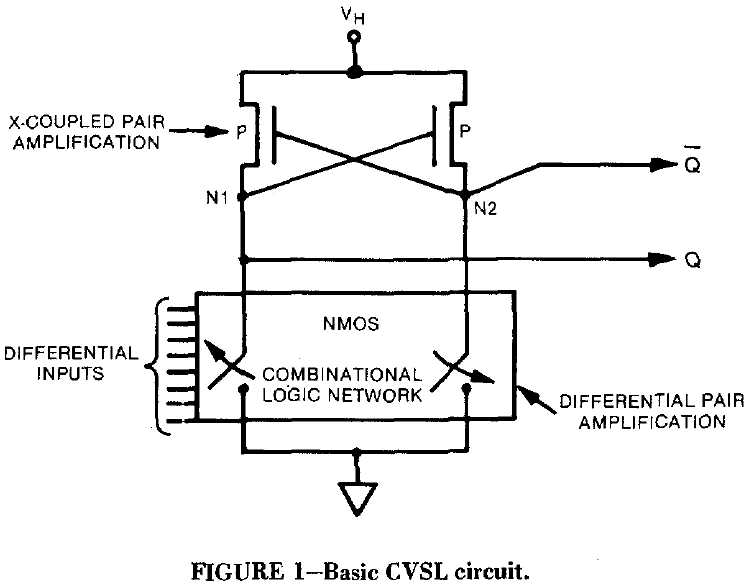

指出选择一个逻辑系列需要衡量功耗,延迟,逻辑密度,器件/制造复杂度,兼容度。下图为CVSL逻辑电路:

CVSL差分逻辑主要由差分上拉网络和互补组合逻辑网络构成,如上图所示,当左边的NMOS求值电路进行下拉功能时,Q输出为低电平,从而右侧上拉P管导通,而右侧NMOS阵列求值后不导通因此N2节点即Q非输出高电平,左侧P管上拉网络截止,从而输出互补信号。

该电路拓扑的优点有:经优化后,可以以低面积消耗进行复杂的布尔逻辑运算;提供差分信号输出,有利于后续逻辑应用;互补信号均在单电路延时里完成;同样在分析上不存在静态电流。缺点是需要在不需要互补信号时逻辑有冗余。

[文献名] L. C. M. G. Pfennings, W. G. L. Mol, J. J. J. Bastiaens, and J. M. F. van Dijk, “Differential split-level CMOS logic for subnanosecond speeds,” IEEE Journal of Solid-State Circuits, vol. 20, no. 5, pp. 1050–1055, Oct. 1985.

[相关观点]

(1)引言:指出经典原则“增强型耗尽型NMOS电路比CMOS要快”对于传统CMOS技术在速度上的改进是一个挑战。差分分离电平能够在E/D拓扑的NMOS逻辑的静态功耗和CMOS的动态功耗中找到折中。

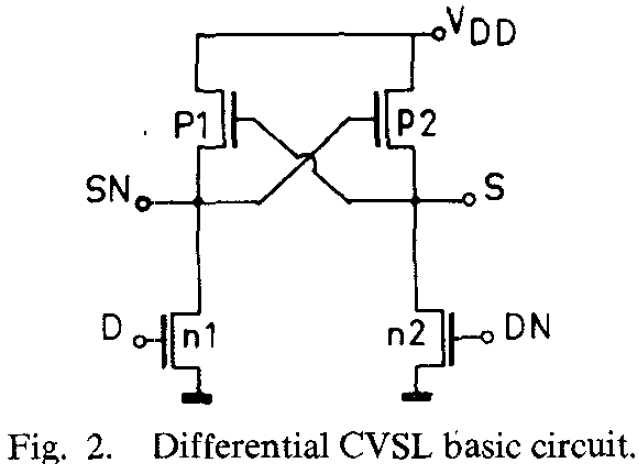

(2)对于CVSL的简要总结:如下图所示为CVSL的经典电路:

现在假设我们需要将D从低到高翻转,当D输入为低时,SN输出为高电平,S输出为低电平,当将输入D跳变至高电平后,n1导通SN的结点进行放电,但是在交变的过程中S电压虽然有所上升但是仍能使P1处于导通状态,因此N1和P1都处于导通状态,这样会出现一个相当大的电流和附加的延时。

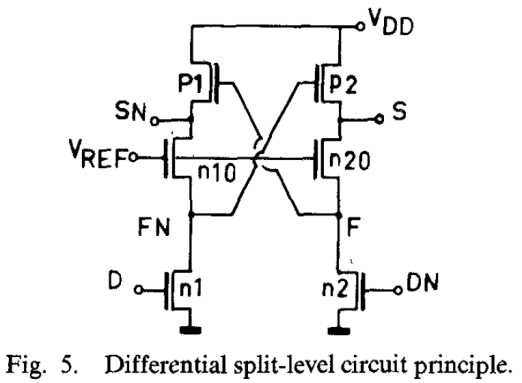

(3)DSL CMOS逻辑如下图所示:

如上图所示,在DSL逻辑中,嵌入了2只N管n10和n20,它们的栅极都被一个参考电压所控制,这个电压被设置为1/2VDD。当我们将D从低电平往高电平跳转,初始时,SN为高电平,由于参考电压的关系,结点FN只能被设置为1/2VDD,结点F的电压大约是100mV,因此P2管在FN的控制下弱导通,这样会造成一个静态功耗的消耗。此时,我们将输入信号翻转,处于1/2VDD电平的结点FN会被放电至地,此时会使P2管强导通,这样S和F结点的电平都将上升,此时,能够更快地使P1管进入弱导通状态。

(4)总结:差分分离逻辑CMOS电路有着10倍快速于以往的延时,但是需要以静态功耗作为代价。

[文献名] V. G. Oklobdzija and R. K. Montoye, “Design-performance trade-offs in CMOS-domino logic,” IEEE Journal of Solid-State Circuits, vol. 21, no. 2, pp. 304–306, Apr. 1986.

[相关观点]

(1)引言:多米诺逻辑由于其类nMOS的性能和类CMOS的功耗引起了研究者们的关注,但是多米诺逻辑存在一个电荷重分布的问题使它的应用受到了影响。指出了多米诺拓扑中反相功能不可行,因此设计异或逻辑相当困难。

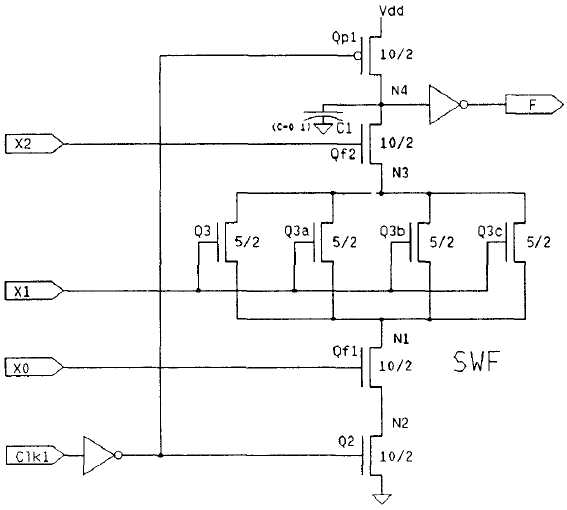

(2)电荷重分布问题,如下图所示:

从多米诺的操作我们可以看到,电荷将存储于结点N4,而结点N1,N2,N3在预充电时并没有电荷存储,也许是因为在前面的周期中进行放电而没有电荷的。因此,在预充电的过程中,就会存在一条电路径去不同的电荷结点,由于没有到地路径而造成电荷重分布,由未充电电容和反相器的阈值电流Ith可以得出以下公式:

其中Ct表示充电结点电荷,Ci表示分布电荷。

(3)解决电荷重分布问题的方法:第一,对分支进行反馈信号实现,在求值阶段通过对分支结点注入电荷以减弱电荷重分布问题。第二个方法,有选择性地增加存储电容的电容在结点以减弱电荷重分布问题所带来的影响。

[文献名] F. S. Lai and W. Hwang, “Differential cascode voltage switch with the pass-gate (DCVSPG) logic tree for high performance CMOS digital systems,” in 1993 International Symposium on VLSI Technology, Systems, and Applications, 1993. Proceedings of Technical Papers, 1993, pp. 358–362.

[相关观点]

(1)引言:CMOS器件的速度,由于快速换代和小型化,已经显著增长,将要赶上硅的双极工艺,但是,最近的实时数字信号处理也需要更快的CMOS的速度。

(2)CPL:概念和例子。以往出现过一些逻辑拓扑系列例如CVSL和DSL,但是,在实际中,CVSL带来的优势是少于原文所阐述的那样,这是因为pMOS交叉对管由于再生性能原因不能简易地进行反相操作,高速的P管锁存是可行的但只存在于当栅极宽度足够的小。但是小的栅极宽度又会降低上拉时间。DSL比传统CMOS快速,但是需要消耗静态电流。

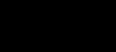

CPL主要的观点是使用nMOS传输门网络进行逻辑组织。如下图所示:

CPL的构成包括:互补的输入输出信号,nMOS传输门逻辑网络,CMOS输出反相器。传输晶体管的作用是作为下拉和上拉的的器件,因此就不需要pMOS锁存。由于N管传输的信号有衰减,因此最后通过反相器进行放大。

CPL一个有吸引力的地方就是其互补输出可以简单地通过4只晶体管产生,其原因是在传输管拓扑中一只晶体管采用栅极和漏源一端作为输入端,大大增加逻辑密度。由于采用传输管拓扑,其输出缓冲器可以根据级联情况进行取舍,大大减少晶体管数量,由此也减少了延迟时间。

(3)结论:在CPL中,差分输出被构建而且不需要pMOS锁存负载,在速度上两倍于传统CMOS,由于输入电容的变小,功耗也变小。

[文献名] M. Suzuki, N. Ohkubo, T. Shinbo, T. Yamanaka, A. Shimizu, K. Sasaki, and Y. Nakagome, “A 1.5-ns 32-b CMOS ALU in double pass-transistor logic,” IEEE Journal of Solid-State Circuits, vol. 28, no. 11, pp. 1145–1151, Nov. 1993.

[相关观点]

(1)引言:传输管对于CMOS来说有着速度优势因为其有着高密度逻辑利用率。但是对于这种架构来说,当利用其进行串联进位时,就会出现问题。

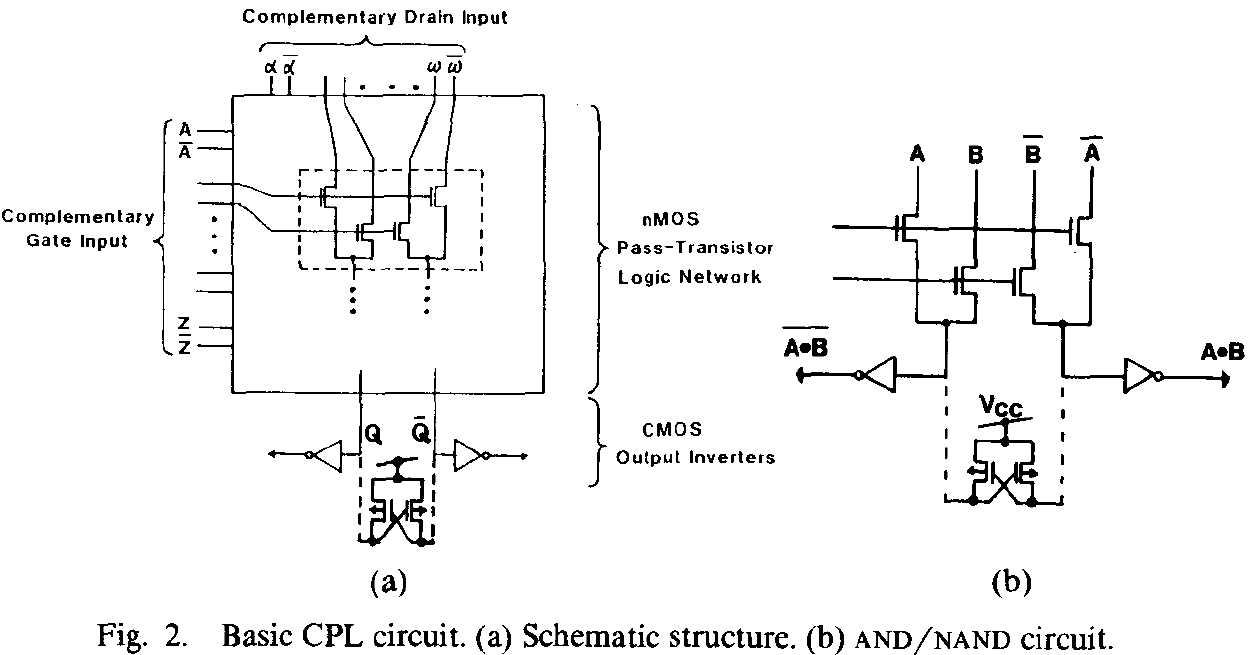

(2)双传输晶体管逻辑:当利用CPL特别是在低电压的情况下,对于噪声容限和速度的衰减是需要考虑进去设计的。双传输门逻辑如下图所示:

类似于CPL,DPL也有互补输出,且使用NMOS和PMOS,对比CPL,其只使用了NMOS。对于CPL,其只有CMOS构成传输阵列,有着较低的输入电容和高速运作,但是,这样做的话在输出端其输出电平就会比VCC少一个阈值电压Vth。利用CMOS作为传输管能获得全摆幅输出但是又以提高了输入电容作为代价。在DPL中,输入信号被平衡分配至栅极输入端,这样能够有一个更平衡的输入电容和减少对于数据延时的依赖。同时,由于其控制特性,驱动电流的能力也更好。

缺点:版图面积方面没有特别优势。

[文献名] V. G. Oklobdzija and B. Duchene, “Pass-transistor dual value logic for low-power CMOS,” in 1995 International Symposium on VLSI Technology, Systems, and Applications, 1995. Proceedings of Technical Papers, 1995, pp. 341–344.

[相关观点]

(1)引言:新的传输管逻辑家族有效地改进速度和功耗,对于DPL来说,其性能还没有完全发挥。

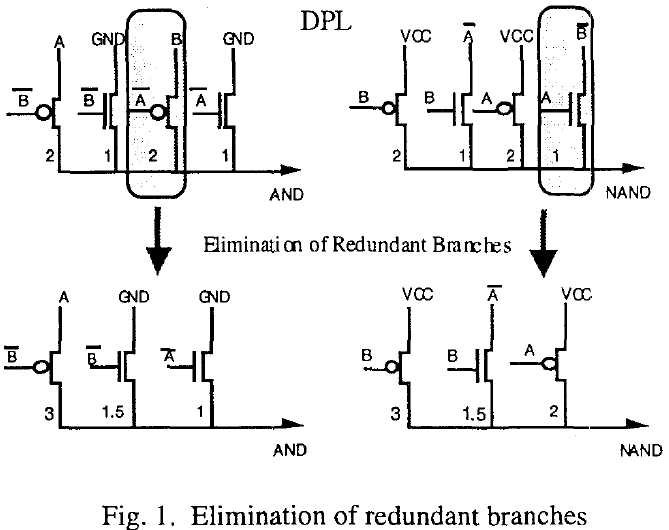

(2)新的逻辑门如下图所示:

在新的逻辑门设计中,冗余的P管被去除,这样得到的改善是:改善PMOS管所引起速度下降,继续保持全摆幅性能。去除PMOS后会出现一些情况,例如,PMOS的电流路径没有了,会造成输出不平衡,导致传输时间变差,为了解决这个问题,特别的晶体管管宽需要被增加。

在适当调节管宽后,对于DPL和DVL的NAND/AND门,结论是,在速度上有20%的提升,但是用了75%的管子;减少了25%的连接点和导线使用,在面积上只比DPL多4%。

(3)结论:在功耗的消耗对比传统CMOS减少了约30%-50%,对于DPL的设计也可以被综合工具所支持。

[文献名] A. Parameswar, H. Hara, and T. Sakurai, “A swing restored pass-transistor logic-based multiply and accumulate circuit for multimedia applications,” IEEE Journal of Solid-State Circuits, vol. 31, no. 6, pp. 804–809, Jun. 1996.

[相关观点]

(1)引言:时下最流行的设计技术是全CMOS设计,因为其有着极好的噪声容限。同时,一些新型的电路拓扑也出现了,大多数方法都变为静态方法因为动态电路有着电荷重分布的问题和噪声容限问题。

对于CPL来说,有着互补输出和输出缓冲器,但是,因为有传输管连接,就可能会有漏电流通过反相器特别当软上拉锁存没有使用。对于DPL来说,同时使用了NMOS和PMOS以获得传输中的全摆幅性能,但是有着高面积消耗和高功耗的缺点。对于DCVSPG来说,其通过传输管与层叠差分对进行运作,但是,这种逻辑风格当使用至长级联时就会出现下拉能力的问题,尤其是没有内部缓冲器的情况下。

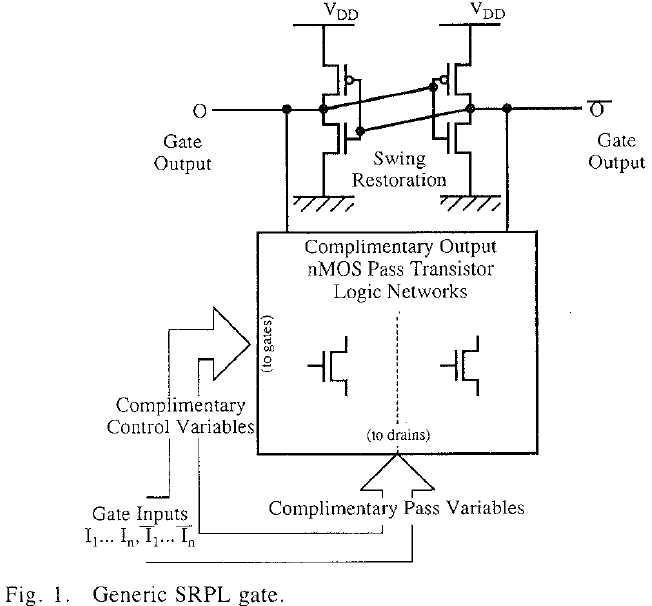

(2)摆幅恢复传输管逻辑,如下图所示

SRPL由2个主要部分组成,第一个互补交叉连接的一对反相器,第二是传输门阵列,这个阵列由两种输入变量构成,第一种输入变量接入传输管的漏极,第二种输入变量接入传输管的栅极,因此可以构成任意的逻辑函数。

性能比较:对于全CMOS设计来说,其有着最慢的速度,且其功耗也是相当高,主要的原因是因为PMOS的低效导致了高数量的晶体管设计,大面积的栅极消耗,大的输入电容,这些主要的问题都是由于PMOS的驱动能力所衍生的。DPL在速度上对比CMOS有着30%的改善,但这以高晶体管数量和高功耗为代价。DCVSPG也比CMOS要快,但是难应用于结构简洁的设计中去,主要原因是没有一个合适的下拉机制,除非在级联的过程中加入反相器进行缓冲。对于CPL来说,其有着5种逻辑拓扑中最快的速度表现,但这也是以高功耗为代价,另外CPL也没有做到全摆幅输出,没有全摆幅的输出意味着对于反相器输入来说其噪声容限是相当差的,而且晶体管的阈值电压对于工艺的变化也是相当敏感的,这反过来又更加影响了nMOS管对CPL性能的影响。

SRPL优点:采用反相器作为输出有着更好的扇出系数,更低的功耗,这是由于其低晶体管数量和低的输入电容所给予的,而且,快速的反相也使其不存在直接的DC通路。

今天的文章数字逻辑cmos_电子元器件数据手册搜索引擎分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/64387.html