文章目录

从嵌入式Linux到ZYNQ

之前的学习领域一直是ARM,从STM32到NXP iMX6, 从裸机开发到Linux操作系统开发。

机缘巧合之下,要开始接触使用xilinx的ZYNQ,对这款新的平台进行学习

因为ZYNQ本质上是ARM+FPGA,手上的这款是一个入门级别的AX7020,ARM是Cotex-A9架构,和之前使用的imx6是相同的架构,加上对于FPGA的学习有过一段Altera平台的Verilog学习和VHDL学习,也有一定的Matlab信号处理基础

所以,我将在学习过程中,引入更多我的理解,甚至一些类比来帮助有基础的开发者学习

学习过程中主要参考的资料就是 ALINX官方教程以及正点原子的教程

ZYNQ简介

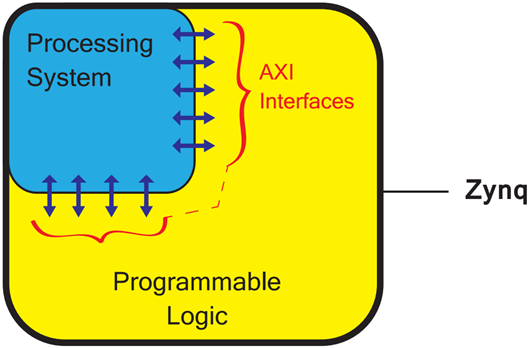

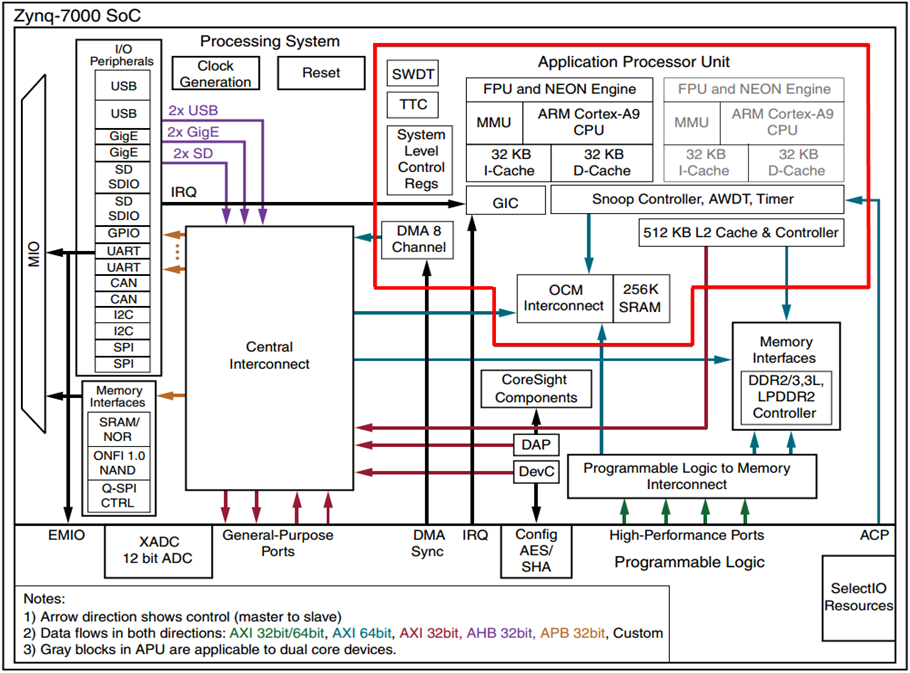

Zynq-7000 All Programmable SoC

ZYNQ是赛灵思公司(Xilinx)推出的新一代全可编程片上系统,它将处理器的软件可编程性与FPGA的硬件可编程性进行完美整合,以提供无与伦比的系统性能、灵活性与可扩展性。

ZYNQ旨在为视频监控、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理能力与计算性能。这款基于ARM处理器的SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力等要求。

ZYNQ的本质特征,是它组合了一个双核ARM Cortex-A9处理器和一个传统的现场可编程门阵列 (FPGA)逻辑部件。

为了实现ARM 处理器和 FPGA 之间的高速通信和数据交互,发挥 ARM 处理器和 FPGA的性能优势,需要设计高效的片内高性能处理器与 FPGA 之间的互联通路。因此,如何设计高效的 PL 和 PS 数据 交互通路是 ZYNQ 芯片设计的重中之重,也是产品设计的成败关键之一。

我们就将主要介绍 PS 和 PL 的连接,让用户了解 PS 和 PL 之间连接的技术。

其实,在具体设计中我们往往不需要在连接这个地方做太多工作,我们加入IP 核以后,系统会自动使用 AXI 接口将我们的 IP 核与处理器连接起来,我们只需要再做一点补充就可以了。

PL简介

早期生产的数字集成电路逻辑功能都是固定不变的。

要想改变它的逻辑功能,就必须改变内部各单元电路之间的连接,而这种连接在集成电路制作过程中已经固定下来了。

允许用户自行修改内部连接的集成电路:可编程逻辑器件(Programmable Logic Device)

1、PLD内部的电路结构可以通过写入编程数据来设置;

2、写入PLD的编程数据还可以擦除重写;

PLD的逻辑功能可以由使用者通过编程来设定。

常用的可编程逻辑器件:

CPLD:复杂可编程逻辑器件(Complex Programmable Logic Device)

FPGA:现场可编程门阵列(Field Programmable Gate Array)

本质差异:电路结构不同。

CPLD:基于“乘积项”的与或逻辑阵列

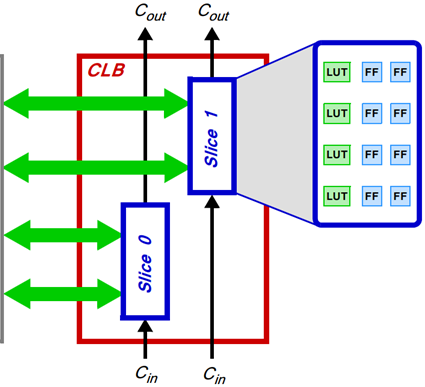

FPGA:基于“查找表”(LUT,Look UP Table)的CLB阵列

如图就是一个FPGA结构

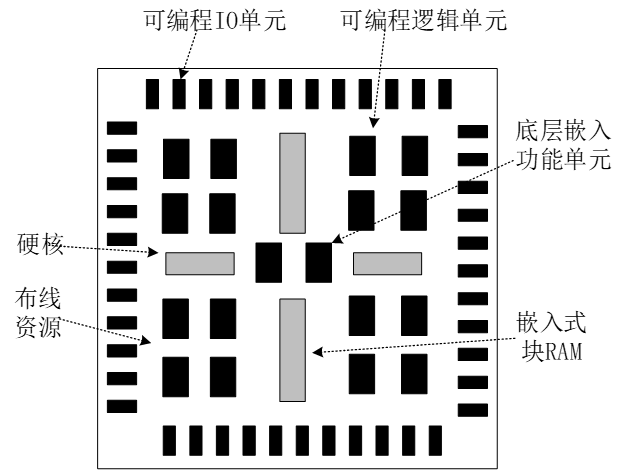

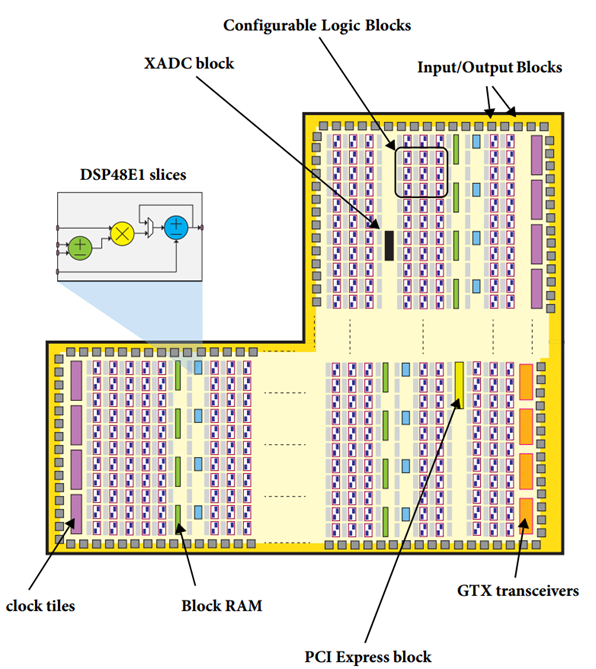

PL结构

对照ZYNQ的结构,我们可以看到PL部分的结构主要还是可编程逻辑单元、可编程IO单元等资源

ZYNQ不同的产品线采用不同的架构

Artix™-based devices: Z-7010, Z-7015, and Z-7020

Kintex™-based devices: Z-7030, Z-7045, and Z-7100

PS简介

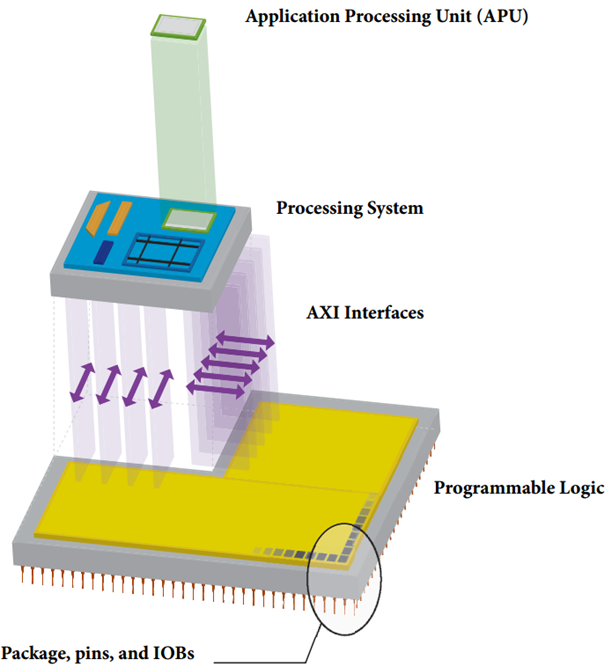

上面的PL其实就是FPGA芯片部分,也就是下面3D图片中最下面的黄色部分

3D结构图上面的就是ARM部分,也就是PS

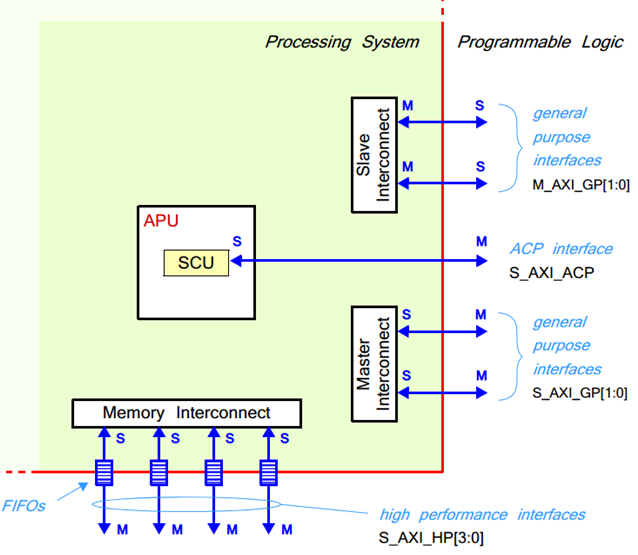

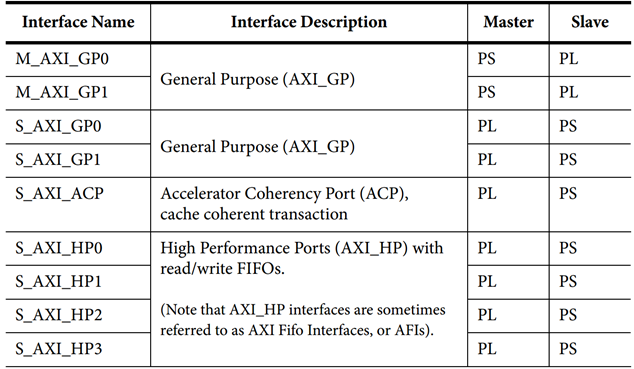

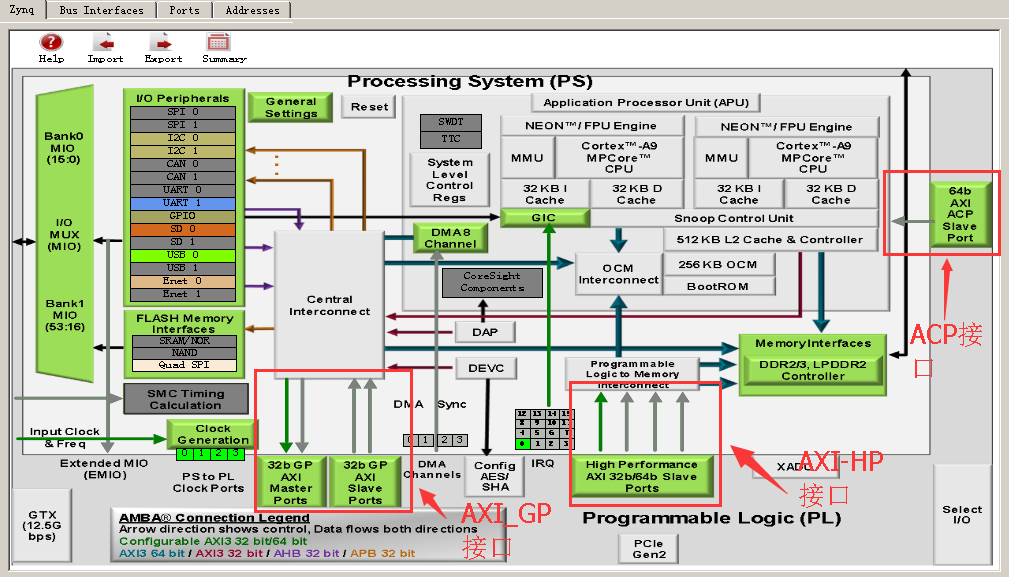

在ZYNQ 芯片内部用硬件实现了 AXI 总线协议,包括 9 个物理接口,分别为 AXI GP0~ AXIGP3 AXI HP0~AXI HP3 AXI ACP 接口。

AXI_ACP 接口,是 ARM 多核架构下定义的一种接口,中文翻译为加速器一致性端口,用来管理 DMA 之类的不带缓存的 AXI 外设, PS 端是 Slave 接口。

AXI_HP接口,是高性能 带宽的 AXI3.0 标准的接口,总共有四个, PL 模块作为主设备连接。主要用于 PL 访问 PS 上的存储器( DDR 和 On Chip RAM)每一个接口都有一个FIFO

AXI_GP接口,是通用的 AXI 接口,总共有四个,包括两个 32 位主设备接口和两个 32 位从设备接口。

可以看到,只有两个AXI GP 是 Master Port ,即主机接口,其余 7 个口都是 Slave Port (从机接口)。

主机接口具有发起读写的权限, ARM 可以利用两个 AXI GP 主机接口主动访问 PL 逻辑,其实就是把 PL 映射到某个地址,读写 PL 寄存器如同在读写自己的存储器。

其余从机接口就属于被动接口,接受来自 PL 的读写,逆来顺受。

有人会问,为什么高性能接口不做成主机接口呢?这样可以由 ARM 发起高速数据传输。

答案是高性能接口根本不需要 ARM CPU 来负责数据搬移,真正的搬运工是位于 PL 中的 DMA 控制器。

AXIDMA :实现从 PS 内存到 PL 高速传输高速通道 AXI HP<HP<——–>AXI Stream 的转换AXI

FIFO MM2S :实现从 PS 内存到 PL 通用传输通道 AXI GP<GP<———->AXI Stream 的转换

AXI Datamover :实现从 PS 内存到 PL 高速传输高速通道 AXI HP<HP<——–>AXI Stream 的转换,只不过这次是完全由 PL 控制的, PS 是完全被动的。

AXI VDMA :实现从 PS 内存到 PL 高速传输高速通道 AXI HP<HP<——–>AXI Stream 的转换,只不过是专门针对视频、图像等二维数据的。

AXI CDMA :这个是由 PL 完成的将数据从内存的一个位置搬移到另一个位置,无需 CPU 来插手。

关于如何使用这些IP ,我们会在后面的章节中举例讲 到。

有时,用户需要开发自己定义的IP 同 PS 进行通信,这时可以利用向导生成对应的 IP 。用户自定义 IP 核可以拥有 AXI 4 LiteAXI4 AXI Stream PLB 和 FSL 这些接口。后两种由于 ARM 这一端不支持,所以不用。

有了上面的这些官方IP 和向导生成的自定义 IP ,用户其实不需要对 AXI 时序了解太多(除非确实遇到问题),因为 Xilinx 已经将和 AXI 时序有关的细节都封装起来,用户只需要关注自己的逻辑实现即可。

AXI协议严格的讲是一个点对点的主从接口协议,当多个外设需要互相交互数据时,我们需要加入一个 AXI Interconnect 模块,也就是 AXI 互联矩阵,作用是提供将一个或多个 AXI 主设备连接到一个或多个 AXI 从设备的一种交换机制(有点类似于交换机里面的交换矩阵)。

这个AXI Interconnect IP 核最多可以支持 16 个主设备、 16 个从设备,如果需要更多的接口,可以多加入几个 IP 核。

AXI

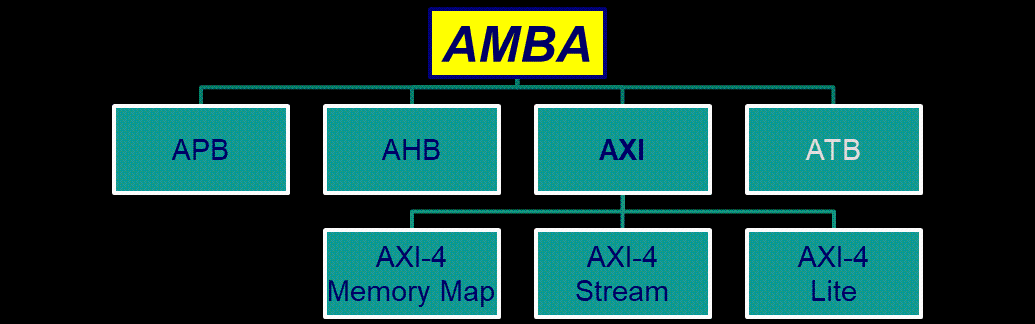

AXI全称 Advanced eXtensible Interface ,是 Xilinx 从 6 系列的 FPGA 开始引入的一个接口协议,主要描述了主设备和从设备之间的数据传输方式。

在 ZYNQ 中继续使用,版本是 A XI4 ,所以我们经常会看到 AXI4.0 ZYNQ 内部设备都有 AXI 接口。其实 AXI 就是 ARM 公司提出的AMBA Advanced Microcontroller Bus Architecture )的一个部分,是一种高性能、高带宽、低延迟的片内总线,也用来替代以前的 AHB 和 APB 总线。第一个版本的 AXI AXI3 )包含在 2003年发布的 AMBA3.0 中, AXI 的第二个版本 AXI AXI4 )包含在 2010 年发布的 AMBA 4.0 之中。

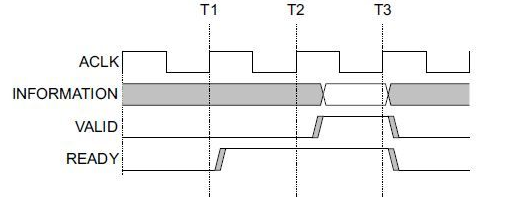

AXI协议主要描述了主设备和从设备之间的数据传输方式,主设备和从设备之间通过 握手信号建立连接。当从设备准备好接收数据时,会发出 READY 信号。

当主设备的数据准备好时,会发出和维持 VALID 信号,表示数据有效。数据只有在 VALID 和 READY 信号都有效的时候才开始传输。当这两个信号持续保持有效,主设备会继续传输下一个数据。主设备可以撤销VALID 信号,或者从设备撤销 READY 信号终止传输。 AXI 的协议如图, T2 时,从设备的 READY信号有效, T3 时主设备的 VILID 信号有效,数据传输开始。

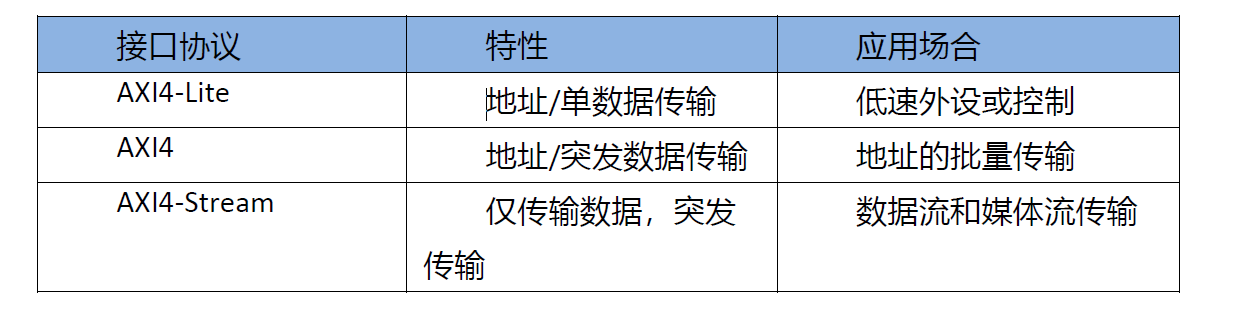

在ZYNQ 中,支持 AXI Lite AXI4 和 AXI Stream 三 种总线,通过表 5 1, 我们可以看到这三中AXI 接口的特性。

其中,最重要的就是 AXI-4 Memory Map 和 AXI-4 Stream

AXI-4 Memory Map:存储映射

AXI-4 Stream:传输大量数据

AXI4 Stream

这是一种连续流接口,不需要地址线(很像FIFO ,一直读或一直写就行)。对于这类 IPARM 不能通过上面的内存映射方式控制( FIFO 根本没有 地址的概念),必须有一个转换装置,例如 AXI DMA 模块来实现内存映射到流式接口的转换。 AXI Stream 适用的场合有很多:视频流处理;通信协议转换;数字信号处理;无线通信等。其本质都是针对数值流构建的数据通路,从信源(例如 ARM 内存、 DMA 、无线接收前端等)到信宿(例如 HDMI 显示器、高速 AD 音频输出,等)构建起连续的数据流。这种接口适合做实时信号处理。

AXI4

接口和AXI Lite 差不多,只是增加了一项功能就是批量传输,可以连续对一片地址进行一次性读写。也就是说具有数据读写的 burst 功能。

上面两种均采用内存映射控制方式,即ARM 将用户自定义 IP 编入某一地址进行访问,读写时就像在读写自己的片内 RAM ,编程也很方便,开发难度较低。代价就是资源占用过多需要额外的读地址线、写地址线、读数据线、写数据线、写应答线这些信号线。

ZYNQ芯片开发流程的简介

ZYNQ的开发也是先硬件后软件的方法。具体流程如下:

-

在 Vivado 上新建 工程,增加一个嵌入式的源文件。

-

在 Vivado 里添加和配置 PS 和 PL 部分基本的外设,或需要添加自定义的外设。

-

在 Vivado 里生成顶层 HDL 文件,并添加约束文件。再编译生成比特流文件( (*.bit )。

-

导出 硬件信息 到 SDK 软件开发环境,在 SDK 环境里可以编写一些调试软件验证硬件和软件,结合比特流文件单独调试 ZYNQ 系统。

-

在 SDK 里生成 FSBL 文件。

-

在 VMware 虚拟机里生成 u boot.elf 、 bootloader 镜像。

-

在 SDK 里通过 FSBL 文件 , 比特流文件 system.bit 和 u boot.elf 文件生成一个 BOOT .bin文件。

-

在 VMware 里生成 Ubuntu 的内核镜像文件 Zimage 和 Ubuntu 的 根 文件系统。另外还需要要对 FPGA 自定义的 IP 编写驱动。

-

把 BOOT 、内核、设备树、根文件系统 文件放入到 SD 卡 中,启动开发板电源, Linux操作系统会从 SD 卡里启动。

学习ZYNQ要具备哪些技能

学习ZYNQ 比学习 FPGA 、 MCU 、 ARM 等传统工具开发要求更高,想学好 ZYNQ 也不是一蹴而就的事情。

软件开发人员

计算机组成原理

C 、 C++ 语言

计算机操作系统

tcl 脚本

良好的英语 阅读 基础

逻辑开发人员

计算机组成原理

C 语言

数字电路基础

Verilog 、 VHDL 语言

良好的英语阅读基础

今天的文章【ZYNQ】从入门到秃头01 初识ZYNQ(PS和PL之间连接)分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/64552.html