前言

本次设计基于设计工具cadence allegro17.2,开发板板载CPLD、DSP、SDRAM、Flash等器件。

电源电路

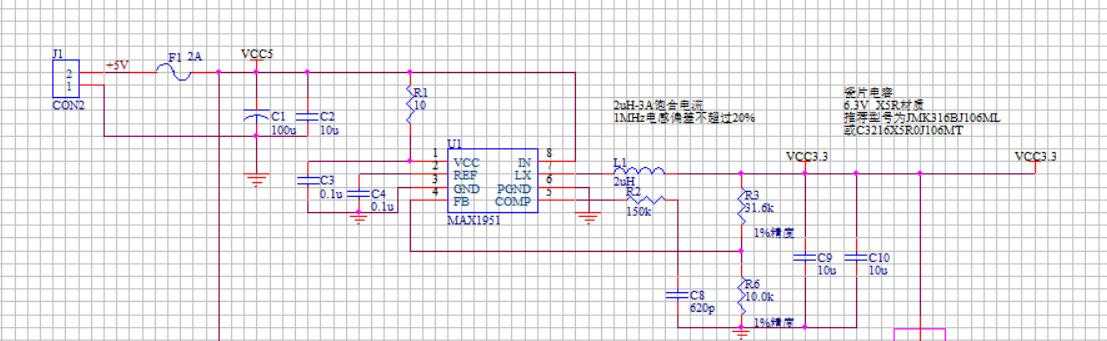

开发板的输入电源是通过接口端子输入的5V电源。开发板上多为数字器件,总电流值不高,因此接口端子后面的保险器(F1)采用2A规格。

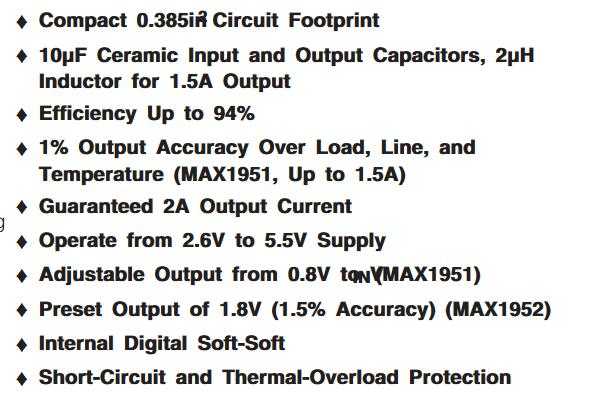

经过滤波后使用DC-DC电源芯片MAX1951对电源进行降压稳压处理。从datasheet的简介可以看出该款芯片拥有94%的工作效率,最高输出电流为2A,完全满足电路设计需求。此外,该芯片的输入电压是2.6V到5.5V,输出电压是0.8V到输入电压,非常适合用于数字电路开发板的设计。

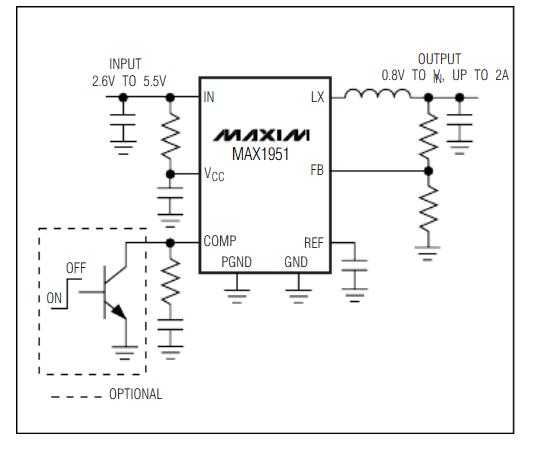

max1951的标准电路如下图所示。输出电压的计算公式为:Vout = (R3/R2 + 1)Vfb。Vfb的标准电压是1.25V。

实际的电路设计如下图所示。需要注意电源芯片的comp引脚(补偿引脚)需要远离电路中的信号部分,以免产生干扰影响稳定性。

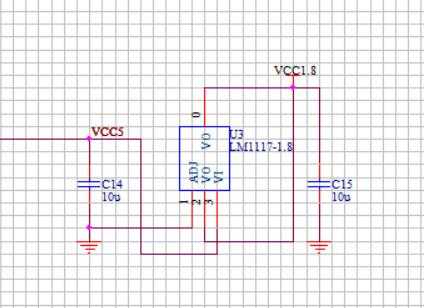

1.8V直接使用LM1117线性电源降压稳压。因为1.8V电路中的功率较小,为了减少电路器件选择了常见的线性电源。

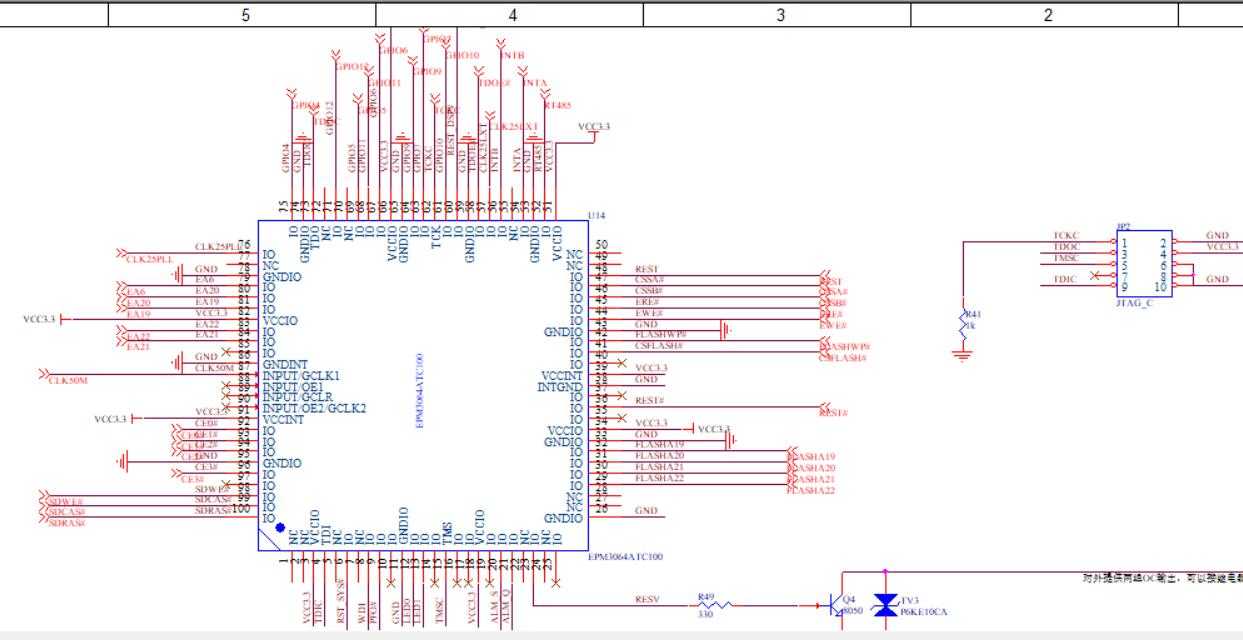

CPLD电路

CPLD电路主要用于与flash芯片与dsp芯片进行通信、控制、数据传输。使用JTAG标准口调试烧录程序。

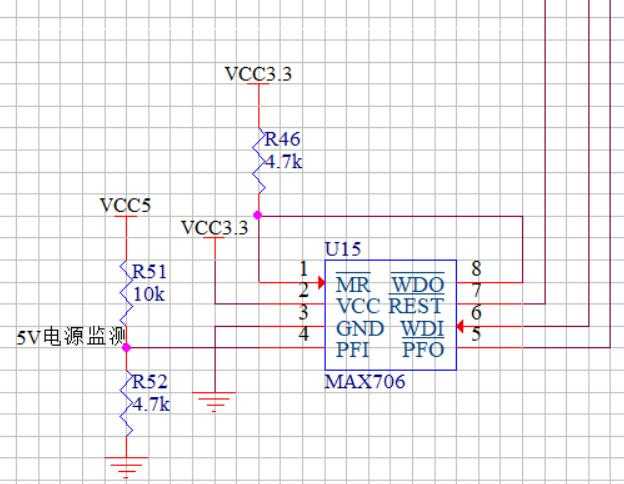

这里使用了一个电源监测芯片MAX706。MAX706可以用来做电源电压报警与看门狗检测。在电路中可以看到,PFI接口通过分压电阻来检测5V电源的波动情况,当5V电源电压明显降低时,PFO接口会向CPLD芯片发送低电平信号报警。此外,WDI端口接收CPLD的看门狗信号,如果看门狗信号出现问题,REST引脚会发送复位信号令其复位。

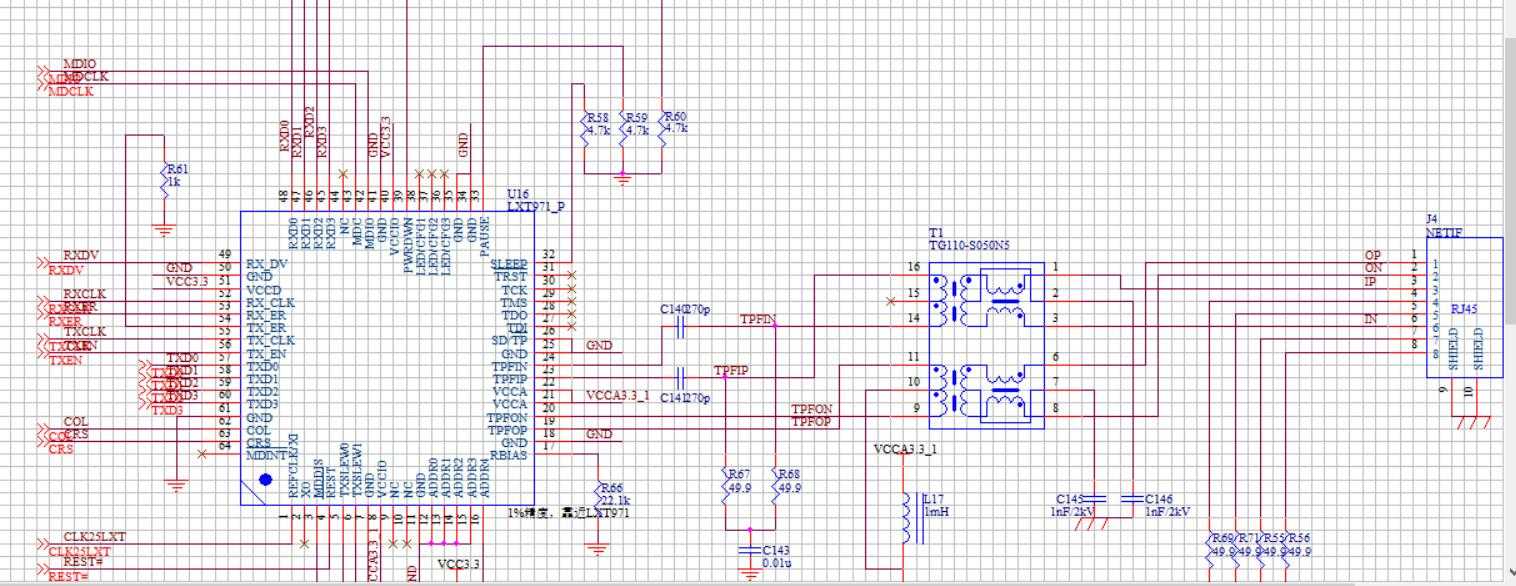

以太网接口电路

该以太网电路的一个特点就是没有采用集成变压器的网口接头,这给电路设计增加了复杂性。增加变压器的显著影响是:为了实现变压器初级次级的隔离,需要做地平面分割,在变压器下方将两块地平面分隔开。

变压器的供电电源需要做LC滤波处理,电容的取值一般为0.01uf~0.1uf,电感选择1mh。

为了实现电路防雷设计,在变压器次级,接地的滤波电容都是耐瞬时电压强的型号。

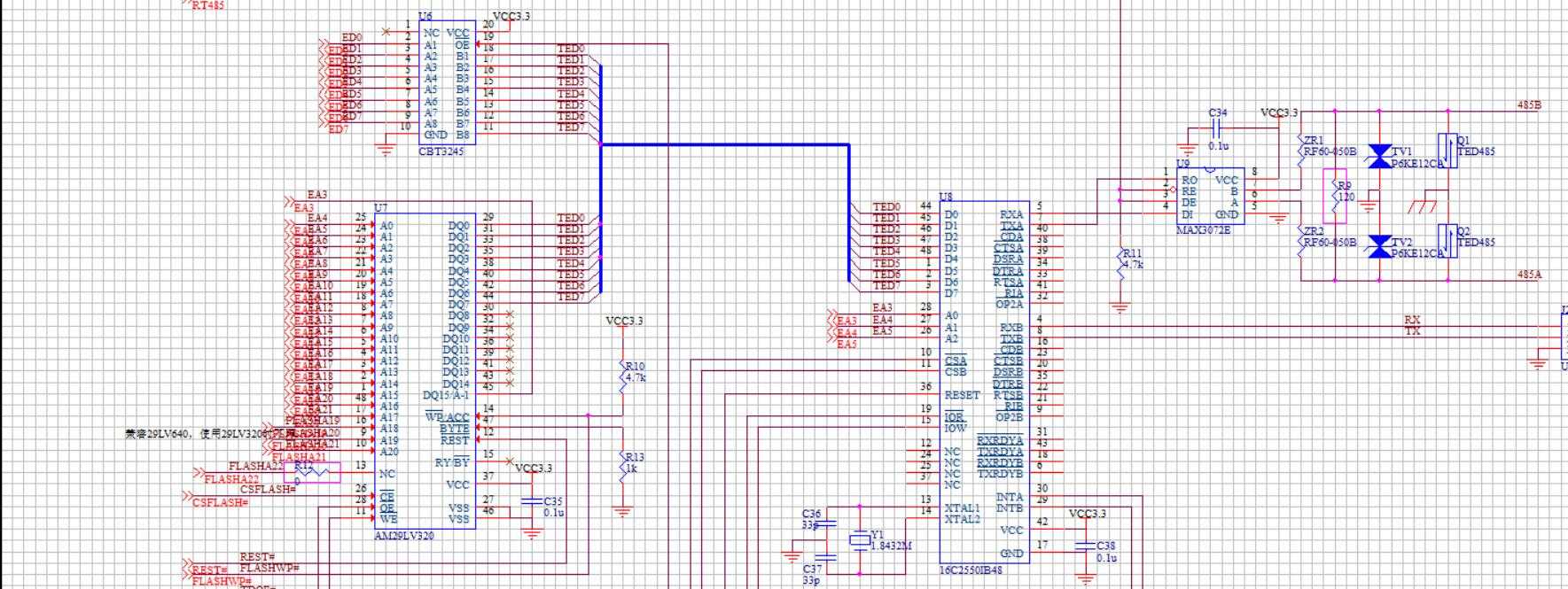

flash电路

flash这边的电路左边是一块flash芯片,右边是一块双通用异步接收器和发送器。两块芯片共同占用总线TED0~TED7。因此需要一个8位总线开关对其进行选择。

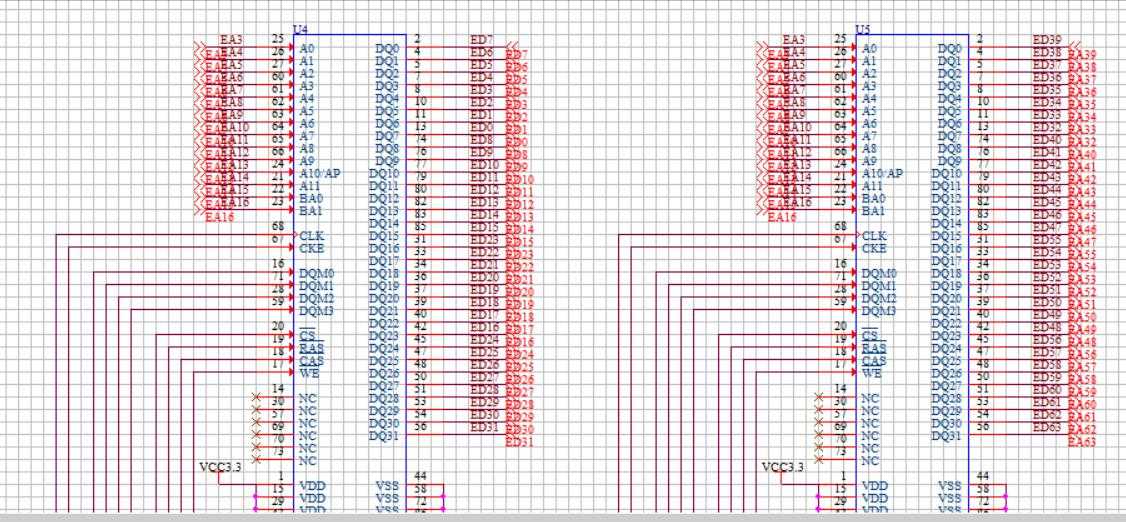

SDRAM

SDRAM电路采用两块芯片并联的方式。第一块SDRAM的数据线为ED0~ED31。第二块SDRAM的数据线为ED32到ED63。

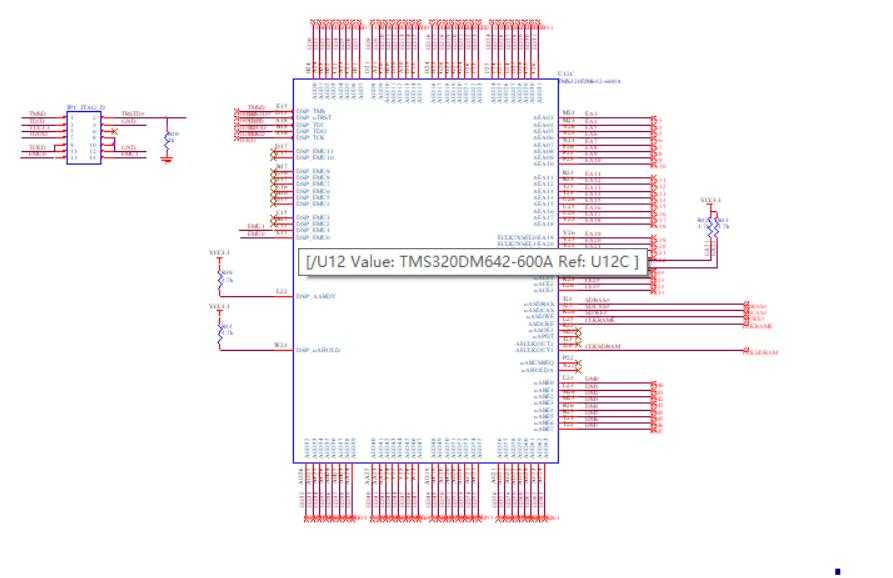

DSP

DSP电路的设计和单片机电路类似,没有其他特别的地方。

今天的文章dsp开发板介绍_DSP系统设计分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/68483.html