目录

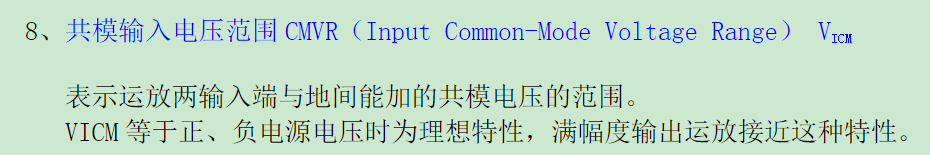

2,结合前面的那篇文章,输入端计入R1、C1低通滤波,输出端没有接电容滤波

运放的轨至轨输入是指运放的输入端信号电压能够达到电源的两个轨,并保持不失真,如上例输入信号电压可达到+/-15V。

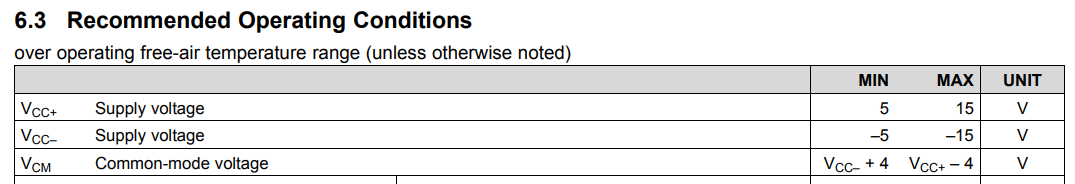

1,查看供电电源的正负极最大与最小电压,共模电压输入范围

2,结合前面的那篇文章,输入端计入R1、C1低通滤波,输出端没有接电容滤波

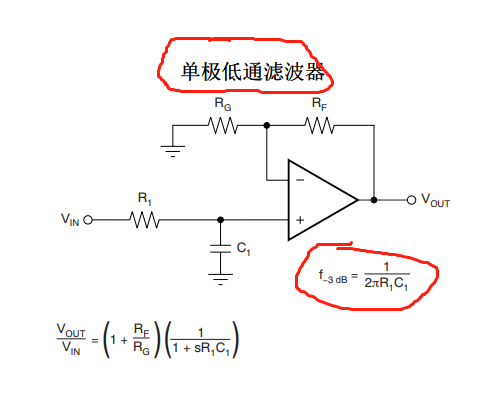

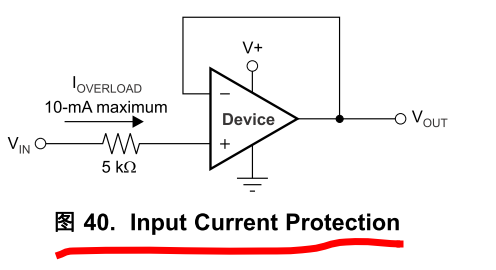

3,输入电流保护(PS: 有的没有最大输入电流限制 )

3-1 轨到轨运放最大输入电流限制?

3-2 有的没有最大输入电流限制

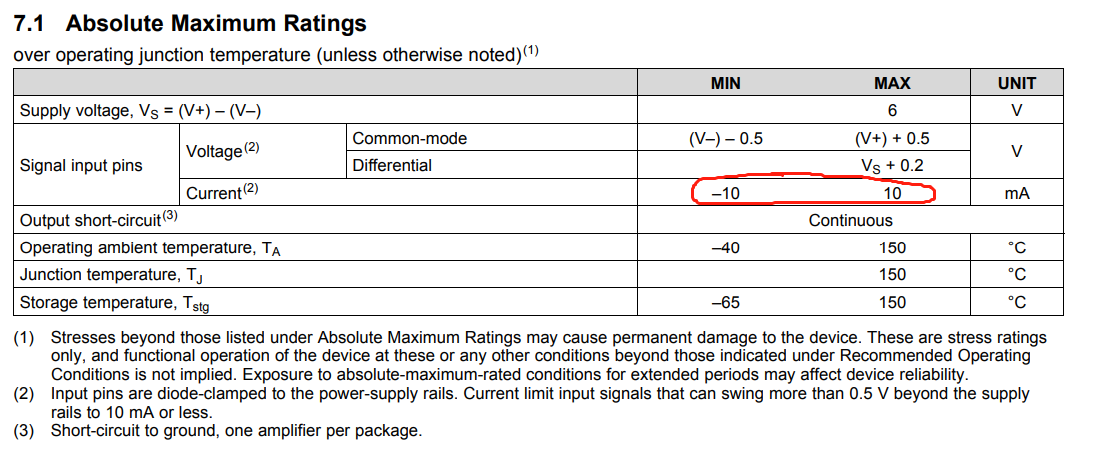

4-运算放大器的轨到轨什么意思

什么是轨到轨?这种运放和普通运放比有什么特点和优点? – 放大器论坛 – 放大器 – E2E™ 设计支持

楼主也可以参考一下Wayne的分享

– http://www.deyisupport.com/question_answer/analog/amplifiers/f/52/t/20405.aspx

– http://www.deyisupport.com/question_answer/analog/amplifiers/f/52/t/20407.aspx

– http://www.deyisupport.com/question_answer/analog/amplifiers/f/52/t/23138.aspx

随着单电源运放的广泛的运用,运放的轨至轨输入(rail to rail input)成为一个时髦的词。现在大部分低电压单电源供电的运放都是轨至轨输入的。TI在轨至轨输入的运放产品方面具有十分领先的优势。本文介绍运放的rail to rail输入的实现以及TI在实现运放的rail to rail 输入方面的领先技术。

先说两句废话,解释一下轨至轨,这里的轨指的是电源轨,运放的两个电源供电电压如+/-15V。这两个电源电压就像两条平行的距离为30V的“轨道”一样限制了运放的输入输出信号。

运放的轨至轨输入是指运放的输入端信号电压能够达到电源的两个轨,并保持不失真,如上例输入信号电压可达到+/-15V。

运放的输入电压范围可在运放的datasheet中找到。就是共模电压范围Vcm(Common-Mode Voltage Range)。如下表即为OPA365的输入电压范围,可见它是典型的轨至轨输入运放。

一般的BJT和JFET是非轨至轨输入的运放。如下表所示为OPA827共模输入电压范围为(V-)+3V至(V+)-3V,典型的非轨至轨运放。

单电源(我们暂且称之为“单电源”)运放的输入级通常有三种结构,第一种是采用PMOS做差分输入级。这样的运入输入级电压可以低于负电源轨0.2甚至0.3V,但达不到正电源轨,如OPA336。下表是datasheet中标出的OPA336输入电压范围。

它的输入级原理框图如下图,典型的PMOS差分输入级。

既然PMOS差分输入级输入电压不能达到正电源轨,那NMOS呢,对头,2-NMOS差分输入级的输入电压可以达到正电源轨,但是达不到负电源轨,一般会在负电源轨的1.2V之上。

此时有人想到了,3-把PMOS和NMOS差分输入级并联起来。在接近电源负电压轨时使PMOS差分输入级工作,在接近电源正电源轨时使NMOS差分输入级工作。这样不就可以实现运放的轨至轨输入了嘛。太巧妙了。的确早先的轨至轨输入运放就是这样设计的。并且现在也在大量使用这种技术。如下图是OPA703的输入级,就是典型的PMOS与NMOS相并联的运放输入级。当输入共模电压在(Vss-)-0.3V<Vcm<(Vss+)-2V时PMOS处于工作状态,NMOS处于关闭状态。当输入共模电压在(Vss-)-2V<Vcm<(Vss+)+0.3V时NMOS处于工作状态,PMOS处于关闭状态。

下表是OPA703的datasheet中给出的共模电压输入范围(V-)-0.3V至(V+)+0.3V.

Bipolar输入级运入同样也有这样的结构,如下图是典型PNP与NPN型三级管并联形成的差分输入级。

今天的文章什么是运算放大器的相位补偿技术_什么是运算放大器的相位补偿技术分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/69441.html