随着技术的发展,数字信号的时钟频率越来越高,电路系统对于信号的建立、保持时间、时钟抖动等要素提出越来越高的要求。EMI,即电磁干扰,是指电路系统通过传导或者辐射的方式,对于周边电路系统产生的影响。EMI会引起电路性能的降低,严重的话,可能导致整个系统失效。在实际操作中,相关机构颁布电磁兼容的规范,确保上市的电子产品满足规范要求。

时钟信号常常是电路系统中频率最高和边沿最陡的信号,多数EMI问题的产生和时钟信号有关。

降低EMI的方法有许多种,包括屏蔽、滤波、隔离、铁氧体磁环、信号边沿控制以及在PCB中增加电源和GND层等等。在应用中可以灵活使用以上方法,其中屏蔽是相对简单的机械学方法,成本较高,不适用于手持和便携式设备;滤波和信号边沿控制对于低频信号有效,不适合当前广泛应用的高速信号。另外,使用EMI/RFI滤波器这些被动元器件,会增加成本;通过LAYOUT技巧降低EMI显然比较费时,而且因设计的不同,手段也不尽相同。

展频时钟(Spread Spectrum Clocking)是另一种有效降低EMI的方法,本文将简要描述展频时钟发生器(Spread Spectrum Clock Generator, SSCG)是如何降低EMI的。

概述

时钟展频通过频率调制的手段将集中在窄频带范围内的能量分散到设定的宽频带范围,通过降低时钟在基频和奇次谐波频率的幅度(能量),达到降低系统电磁辐射峰值的目的。

一般数字时钟有很高的Q值,即所有能量都集中在很窄的频率范围内,表现为相对较高的能量峰值。在频谱图上容易看到在中间频率上有很高的峰值,在奇次谐波位置有较低的峰值;SSCG通过增加时钟带宽的方法降低峰值能量,减小时钟的Q值。图1示意SSCG的工作原理。

图1. SSCG降低EMI示意图

时钟展频通过特定方式调制原始时钟信号。Linear和Hershey Kiss(不是好时之吻巧克力哦)是常用的调制方式。

应用特点

SSCG是一种Active且低成本的解决EMI问题的方案,可以在保证时钟信号完整性的基础上应对更广频率范围内EMI问题。相比传统上使用Ferrite Beads和RF Chokes抑制EMI,SSCG通过时钟内部集成电路调制频率的手段来达到抑制EMI峰值的目的。SSCG不仅调制时钟源,其它的同步于时钟源的数据、地址和控制信号,在时钟展频的同时也一并得以调制,整体的EMI峰值都会因此减小,所以说,时钟展频是系统级的解决方案。这是SSCG相比其它抑制EMI措施的最大优势。

SSCG功能可以由用户选择不同配置,ON或者OFF,以及不同的调制范围等。

被动的EMI抑制器件通常也会集成ESD保护功能,是不耗电的。SSCG由于使用到展频等集成电路功能,会消耗能量。

调制参数

时钟展频有三个主要的控制参数:调制速度(Modulation Rate)、调制深度(Modulation Depth)和调制方式(Modulation Profile)

1. 调制速度

调制速度(MR)是指输出时钟频率 fo 在设定的调制频率范围内的变化速度。调制速度应远小于源时钟的频率 fc 以免引起时序问题(建立/保持时间等),同时应当高于人耳可识别的声音的频率范围(20Hz~20KHz)以免产生噪音。在实际应用中,调制速度一般选择30KHz~120KHz。

2. 调制深度

调制深度是指展频后输出时钟频率 fo 以调制速度MR偏移源时钟频率 fc 的大小。调制深度以偏移(Δf)源时钟频率的百分比(%)来表示。调制深度决定降低EMI峰值的大小。通常调制深度越大,EMI峰值越低。在应用时,需要合理预计系统可接受的频率调制范围。图2表示在不同调制深度下,EMI峰值的对比。

图2. 调制深度对降低EMI程度的影响

在许多系统中,基频的奇次谐波才是产生EMI问题的根源,SSCG不仅衰减基频的EMI辐射,同时也抑制奇次谐波上的能量辐射,而且相比于基频,SSCG对于奇次谐波的衰减作用更为显著。这是因为奇次谐波的(展频后)频带范围相比基频的频带更宽(整数倍)。如图3表征这种影响。

图3. EMI衰减 VS 奇次谐波

3. 调制方式

调制方式(Modulation Profile)决定EMI峰值的表现形式。Linear和Hershey Kiss是SSCG常用的两种调制方式。

线性调制相对简单,顾名思义,线性调制后输出的时钟频率是线性变化的。这种调制方法的缺点,如图4示,输出频谱旁瓣比中间频率幅度高1-2dB,如前文讨论,在任何频率EMI的失效也就意味着整个EMI测试的失败。旁瓣的辐射峰值可能超出SPEC范围,设计者需要考虑到这点的影响。

图4. 线性调制方式 & 输出频谱

通过Hershey Kiss调制可以得到接近平整的频谱图,如图5所示,Hershey Kiss调制的特点是在调制范围的两端,频率变化速度更快,在调制范围的中间值,频率变化较慢。频率在两端变化的速度快,这样信号在频率两端的能量得到更大的衰减,分散到中间位置。整体的表现就是整个频谱的能量近似平坦。图5中采用Hershey Kiss调制方式,EMI峰值更近一步衰减了1.13dB。

图5. Hershey Kiss调制方式 & 输出频谱

图6和图7是两种调制方式的频谱图。

图6. 线性调制

图7. Hershey Kiss调制

展频模式

按展频时钟相对源时钟偏移的不同,展频分为三类:

1. 中间展频

中间展频(Centre Spread)是指展频时钟的平均频率和源时钟频率相同的展频方式。在未调制输出时钟频率等于输入时钟频率的系统中,展频后输出时钟频率 fo 按调频方式(Linear或Hershey Kiss)决定的波形以MR速度,在(fc-Δf)到(fc+Δf)范围内变化,即:

fo = fc ± Δf

例如,100MHz时钟以±1%调制深度中间展频后,输出时钟的变化范围为99MHz~101MHz。

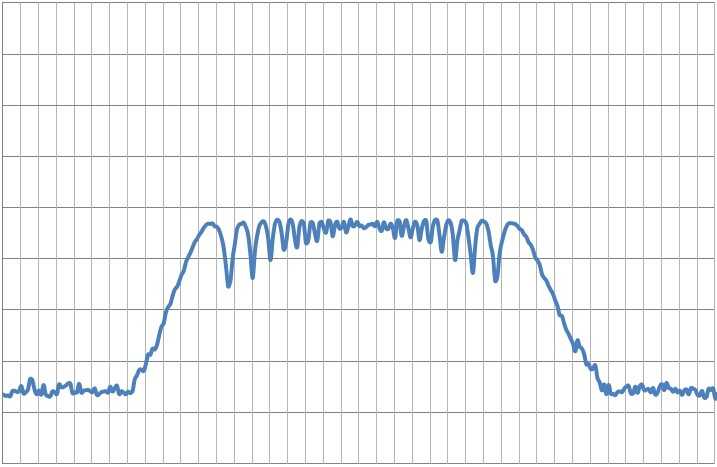

图8和图9表示这种展频模式的特点,其中图8表示输出时钟频率 fo 随时间变化的情况,图9表示幅度(能量)在频率范围内分布的情况。

图8. 中间展频(MDA)

图9. 中间展频(Spectrum Analyzer Plot)

2. 向下展频

向下展频(Down Spread)是指展频时钟的最高频率等于源时钟频率的展频方式。在未调制时钟输出频率等于输入时钟频率的系统中,展频后输出时钟频率 fo 按调频方式(Linear或Hershey Kiss)决定的波形以MR速度,在(fc-Δf)到 fc 范围内变化,即:

fo = fc – Δf

例如,100MHz时钟以-1%调制深度向下展频后,输出时钟的变化范围为99MHz~100MHz。

图10和图11表示这种展频模式的特点,其中图10表示输出时钟频率 fo 随时间变化的情况,图11表示幅度(能量)在频率范围内分布的情况。

图10. 向下展频(MDA)

图11. 向下展频(Spectrum Analyzer Plot)

3. 向上展频

向上展频(Up Spread)是指展频时钟的最低频率等于源时钟频率的展频方式。在未调制时钟输出频率等于输入时钟频率的系统中,展频后输出时钟频率 fo 按调频方式(Linear或Hershey Kiss)决定的波形以MR速度,在 fc 到(fc+Δf)范围内变化,即:

fo = fc + Δf

例如,100MHz时钟以+1%调制深度向上展频后,输出时钟的变化范围为100MHz~101MHz。

图12和图13表示这种展频模式的特点,其中图12表示输出时钟频率(fo)随时间变化的情况,图13表示幅度(能量)在频率范围内分布的情况。

图12. 向上展频(MDA)

图13. 向上展频(Spectrum Analyzer Plot)

注意事项

1. 时钟抖动

时钟展频的一大弊端是不能用于对时钟精度敏感的应用,如以太网和CAN总线。在选择时钟展频和调制深度时,设计人员需要特别注意展频引入额外的Jitter,并可能由此引起的建立/保持时间问题、高误码率和PLL失锁问题。Jitter分为不同类别,对系统性能有不同程度的影响。

- 周期抖动 Period Jitter / PJ

周期抖动是指输出时钟相对于理想时钟的最大偏移值。周期抖动一般是测量一段时间内(通常10,000个周期)所有的时钟,取其中时钟边沿偏离的最大值(earliest and latest edge)。

周期抖动影响同步时钟系统的时序裕量,输出时钟相对理想位置的偏移会对建立/保持时间造成影响。例如,100MHz时钟在以1%调制深度向上展频后,频率的变化范围是100MHz~101MHz,即时钟周期的变化范围是9.9ns~10ns。这样的话,理想的展频时钟就有0.1ns(100ps)的周期抖动。增加调制深度(1%)或时钟频率(100MHz)其中任何一项,周期抖动都会线性增加,从而导致时序问题。另外,以上讨论的周期抖动仅仅是由时钟展频引入的,还不包括设备(时钟发生器)本身固有的Jitter,实际上展频时钟的Jitter应该包括这两部分。时钟固有Jitter可以在关闭展频后测量出来。

- 长时抖动 Long-Term Jitter / LTJ

长时抖动类似于周期抖动,是指在长时间内(many cycles)输出时钟相对理想时钟的最大偏移值。时钟展频在这方面表现更为明显。经过长时间的变化,其时钟信号边缘与理想位置偏移更大。关于长时抖动比较显著的例子是显卡驱动显示器,经过一段时间后,过多的长时抖动会引起像素值偏离设定值。

- 周期间抖动Cycle-to-Cycle Jitter / CTCJ

周期间抖动是指一个时钟周期相对它之前时钟周期的偏移量。在对输入信号进行等间隔取样的通信系统或ADC电路中,周期间抖动会造成非常不利的影响。采样时钟的周期间抖动会导致取样点不准确,因而引起输出数据错误。

时钟展频只引入非常小的周期间抖动。例如30KHz~120KHz调制速度的时钟展频,源时钟的频率至少是MR的1000倍,也就是说至少经过1000个时钟周期,才完成一个调制周期,输出时钟fc相邻周期间的差别非常小。当然,设备(时钟发生器)本身也存在固有的周期间抖动。展频大约只引入低于0.05%的周期间抖动进入到系统。因此展频非常适用于需要低周期间抖动、低误码率和低EMI的系统。

2. 带PLL的展频

当展频的时钟输出到下游的PLL时,注意PLL表现为低通滤波器,即允许输入的低频部分通过,同时衰减其中的高频部分。展频时钟输入PLL时,PLL可能出现无法锁住频率的问题。务必确保PLL必须能检测展频时钟的频率变化并允许展频时钟通过。以上取决于PLL的带宽,如果带宽太低,PLL可能无法可靠地侦测输入时钟,造成侦测偏差,给系统引入更大的Jitter。

参考资料

ON Semiconductor: AND9015 -A Solution for Peak EMI Reduction with Spread Spectrum Clock Generators

Cypress Semiconductor: Reducing EMI in digital systems through spread spectrum clock generators

今天的文章用于降低emi的时钟展频技术是_高频低频中频的划分依据分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/78239.html