基于FPGA的AD5753 (DAC数模转换器)的控制 I(SPI驱动)

软件: Vivado 2018.03

FPGA芯片: XILINX V7 325T ffg900

DAC芯片:AD5753

语言: Verilog

-

- 基于FPGA的AD5753 (DAC数模转换器)的控制 I(SPI驱动)

- 引言

- 1.1 AD5753数据手册阅读

-

- 1.1.1 简介

- 1.1.2 AD5753基本参数

- 1.1.3 AD5753产品详情

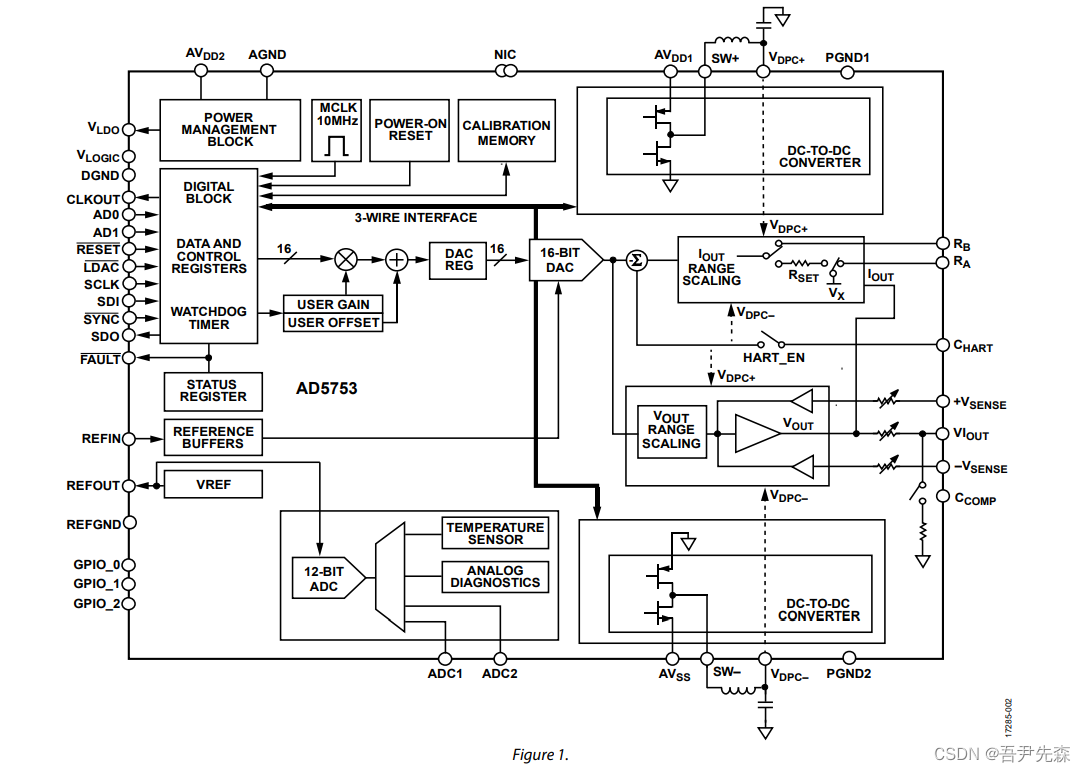

- 1.1.4 AD5753原理图

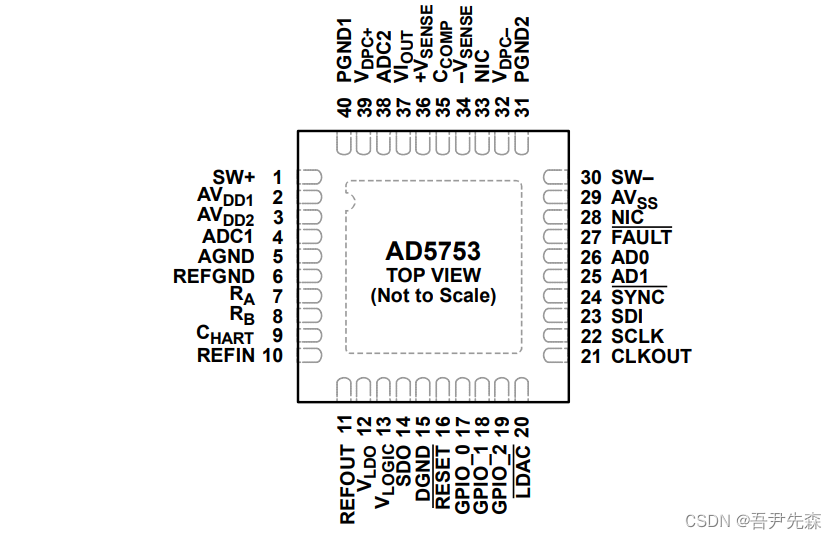

- 1.1.4 AD5753管脚配置与重要管脚说明

- 1.1.5 AD5753时序图

引言

趁周末,分享下最近的学习经验和心得。苟日新,日日新,再日新。

本次分享DAC(AD5753) SPI驱动控制器的FPGA实现,可以借鉴到大部分DAC或者ADC的SPI驱动控制,包括从读数据手册到工程实现,仿真,上板调试的整个过程,实现了对DAC芯片的寄存器读写控制。内容包括上板调试时遇到的问题和解决方案,很有实用价值。

1.1 AD5753数据手册阅读

1.1.1 简介

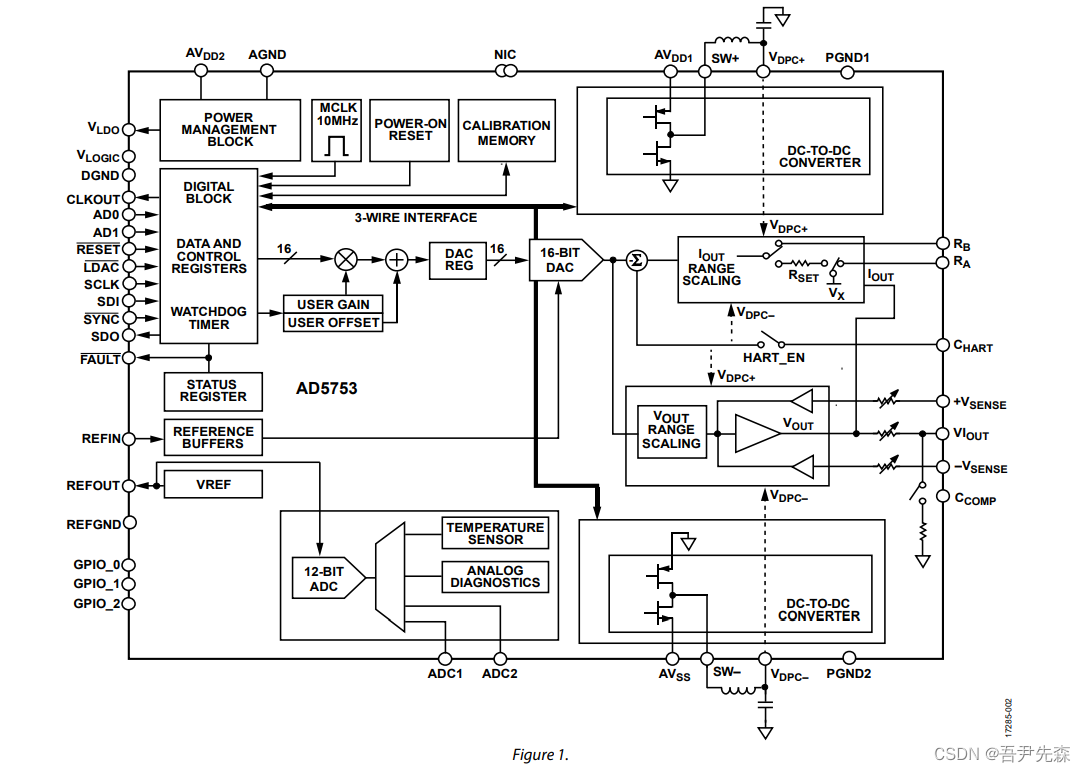

单通道、16位电流和电压输出DAC,提供动态功率控制和HART连接

1.1.2 AD5753基本参数

16 位分辨率和单调性

电流输出范围:0 mA 至 20 mA、4 mA 至

20 mA、0 mA 至 24 mA、±20 mA、±24 mA 和 −1 mA 至 +22 mA

电压输出范围(具有 20% 超量程):0V 至 5 V、0 V 至 10 V、±5 V 和 ±10 V

可编程功率控制 (PPC) 模式可实现比 DPC 更快的建立时间(典型值 15 μs)

高级片内诊断,包括 12 位 ADC

2 个外部ADC 输入引脚 片内基准电压源

1.1.3 AD5753产品详情

AD5753 是一款单通道电压和电流输出数模转换器 (DAC),可在 AVSS 上的最小

−33 V 至 AVDD1 上的最大 +33 V 电压范围内工作,两个轨之间的最大工作电压

为 60 V。片内动态功率控制 (DPC) 可以较大限度地降低封装功耗

AD5753 使用一个多功能 4 线串行外设接口 (SPI),以高达 50 MHz 的时钟频率工

作,并与标准 SPI、QSPI™、MICROWIRE™、数字信号处理器 (DSP) 和微控制器接口

标准兼容。该接口使用可选的 SPI 循环冗余校验码 (CRC) 和监控计时器 (WDT)。

1.1.4 AD5753原理图

1.1.4 AD5753管脚配置与重要管脚说明

| SDO | 串行数据输出。该引脚在 读回模式下对来自串行寄存器的数据进行计时。 最大SCLK速度读回模式为15MHz,该速度取决于VLOGIC电压 |

|---|---|

| RESET | 硬件复位,低有效。发出复位后100μs内,不要写入SPI命令 |

| LDAC | 导入DAC数据,低有效,该引脚更新DAC_OUTPUT寄存器,从而更新DAC输出。不要在SYNC上升沿之前的500 ns窗口内或SYNC上升边缘之后的1.5µs内使能LDAC |

| SCLK | 串行时钟输入。在SCLK的下降沿,数据被计时到输入移位寄存器。在写入模式下,该引脚以高达50 MHz的时钟速度工作,该速度取决于VLOGIC电压。在读取模式下,最大SCLK速度为15 MHz,该速度也取决于VLOGIC电压。 |

| SDI | 串行数据输入。数据必须在SCLK的下降沿有效。 |

| SYNC | 串行接口的帧同步信号。低有效。当SYNC低时,数据在SCLK下降沿传输 |

| FAULT | 故障引脚。低有效,漏极开路输出。当未检测到故障时,此引脚为高阻抗,当检测到某些故障时,该引脚为低阻抗。该引脚必须在V_logic处连一个10 kΩ的上拉电阻 |

1.1.5 AD5753时序图

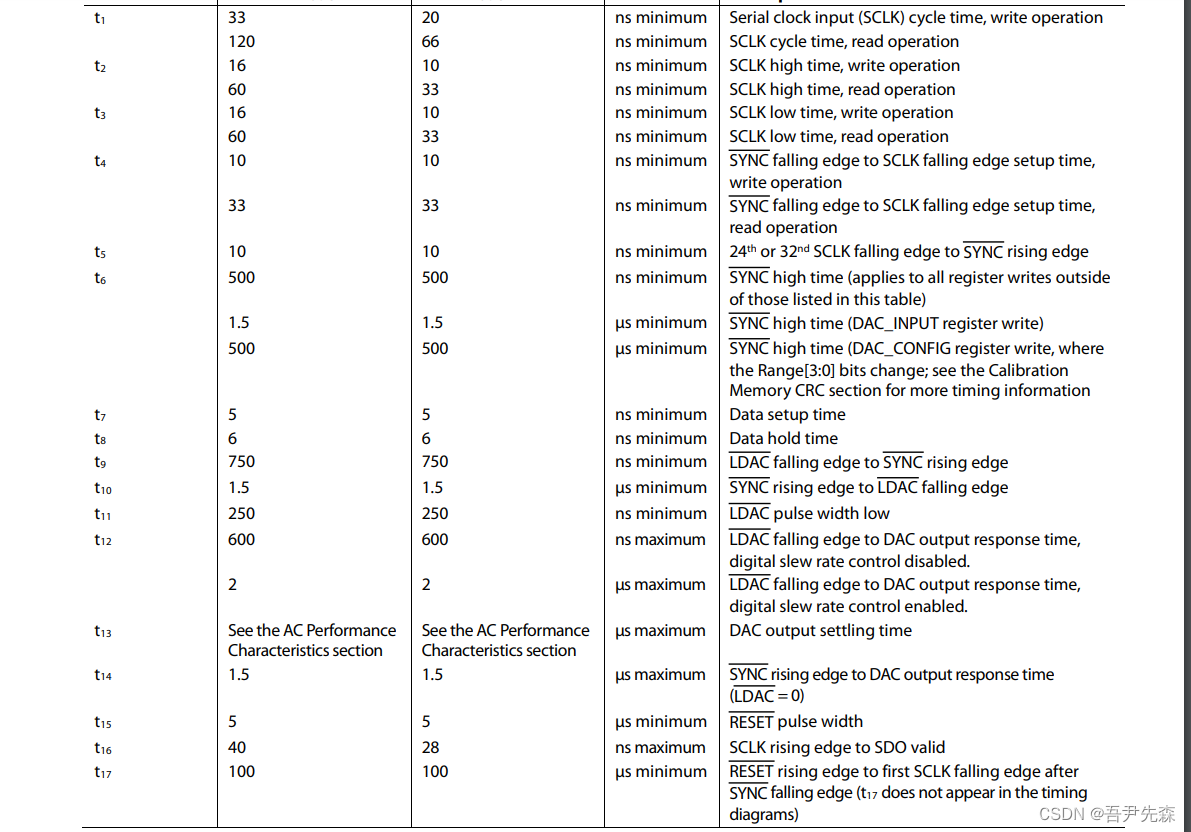

1.1.5.1 AD5753时序特性图

时序特性表格对于准确无误的读懂芯片的时序图至关重要,要和时序图对比着看。

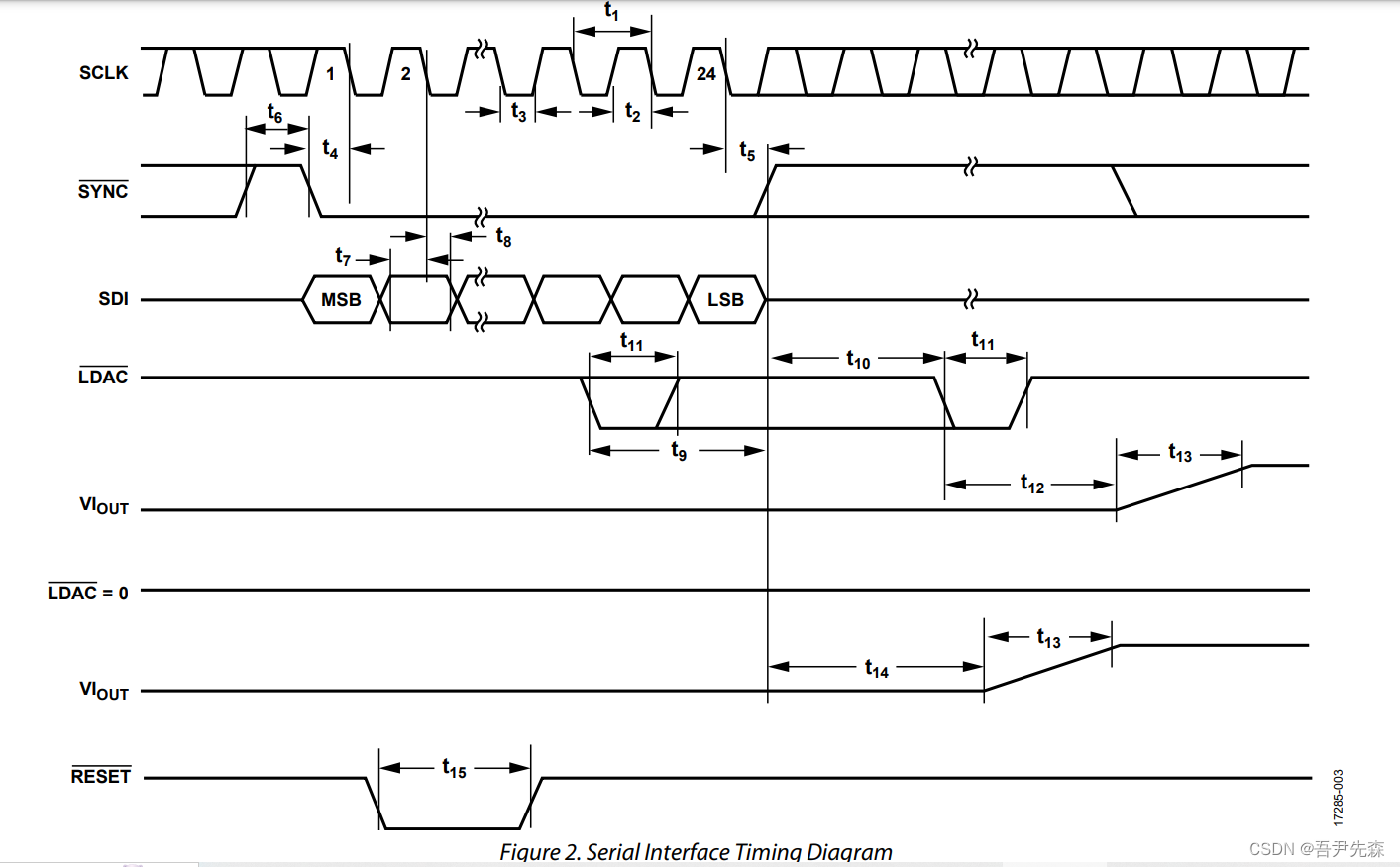

1.1.5.2 AD5753串行接口写操作时序图

此图为AD5753串行接口写操作的时序图,如上所示可以直接写24bit的数据到芯片的寄存器中,要想稳定的驱动芯片,就需要深度理解芯片的控制时序图,因此读时序图切不大意。下面对AD5753串行接口时序图 进行深入解析

如上 t1,表示sclk一个时钟周期,查找1.1.5.1的表,

- 写操作t1 在管脚电压为3到5v时 最小为20ns,即sclk时钟最大为50M,与1.1.4 管脚说明一致。

- t5 表示最后一个sclk的下降沿 到 SYNC的上升沿最小为10ns 。

- t6 表示SYNC同步信号的上升沿到同步信号的下降沿 ,最小值为500ns;

- t7 数据建立时间 最小5ns

- t8 数据保持时间 最小6ns

- t9 LDAC下降沿到SYNC上升沿最小为 750ns

- t10 LDAC上升沿到SYNC下降沿最小为 1.5us,即

- t11 LDAC 低有效的最短时间为250ns

LDAC的最用是更新DAC_OUTPUT寄存器,从而更新DAC输出,是控制时序中比较重要的点,要着重观察。

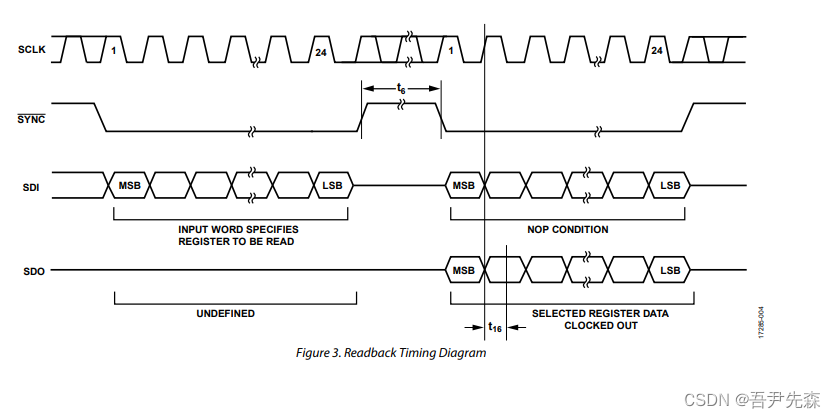

1.1.5.3 AD5753串行接口读操作时序图

第一个24bit 从外界输入所要读取寄存器的地址;

第二个24bit DAC芯片会输出该寄存器里面对应的数据;

两个数据之间的间隔 t6 要达到500ns

未完待续。。。

仅以此篇博客,祝愿各女性朋友节日快乐!祝晓凡女士开心快乐,无忧无虑。

今天的文章ad677模数转换芯片_数模转换器的工作原理分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/84879.html