大家Verilog和VHDL用得好好的,为什么要整个Chisel语言出来???

说到数字芯片或微处理器的设计实现,你首先想到的语言是什么?可能会是Verilog和VHDL这种早在上世纪八十年代就开发出来的成熟硬件描述语言,也可能会是在Verilog基础上建立、结合了硬件验证语言(HVL,Hardware Verification Language)的System Verilog,甚至还有近年来火热的基于C/C++/System C的高层次综合(HLS,High-Level Synthesis)。但是跟你说起Chisel,你可能会一脸茫然。那么,Chisel是什么?为什么又突然冒出个Chisel出来?用Chisel有啥好处?这篇博客就来详细回答这些问题。

Chisel是什么?

2012年,加州大学伯克利分校(UC Berkeley)在计算机体系结构领域顶级会议DAC(Design Automation Conference)上发表了文章Chisel: Constructing Hardware in a Scala Embedded Language(链接直接访问论文原文)。

这个UC Berkeley相信研究计算机体系结构的人应该都有所耳闻,该校在计算机科学领域处于全球顶尖水平。该校的David A. Patterson教授(2017年图灵奖得主)编写的《计算机体系结构:量化研究方法》是体系结构方向研究者的必读书目,其主导建设的开源指令集RISC-V更是体系结构领域的重点研究方向之一。

它们在DAC 2012上的论文首次提出了Chisel语言。Chisel全称Constructing Hardware In a Scala Embedded Language,即嵌入在Scala语言中的硬件构造语言。这是一种新的硬件构造语言,使用高度参数化的生成器和分层的特定领域硬件来支持高级硬件的设计。

再看看Chisel官网给出的介绍:

Chisel is a hardware design language that facilitates advanced circuit generation and design reuse for both ASIC and FPGA digital logic designs. Chisel adds hardware construction primitives to the Scala programming language, providing designers with the power of a modern programming language to write complex, parameterizable circuit generators that produce synthesizable Verilog. This generator methodology enables the creation of re-usable components and libraries, such as the FIFO queue and arbiters in the Chisel Standard Library, raising the level of abstraction in design while retaining fine-grained control.

翻译一下:

Chisel是一种硬件设计语言,可以促进ASIC和FPGA数字逻辑设计的高级电路生成和设计重用。Chisel在Scala编程语言中添加了硬件构造原语,为设计人员提供了现代编程语言的强大功能,可以编写复杂的、可参数化的的硬件设计语言,从而可以编写复杂的、可参数化的电路生成器,从而生成可综合的Verilog代码。这种生成器方法可以创建可重用的组件和库,例如Chisel标准库中的FIFO队列和仲裁器,提高设计的抽象级别,同时保持细粒度的控制。

可以剥离出以下理解:

- Chisel是基于Scala语言的嵌入式的语言,本质上还是Scala语言;

- 区别于Scala,Chisel使用的是自定义的硬件构造原语,在构造硬件时有自己的一套语法规则,可以认为是新语言;

- Chisel并非直接编写电路实现,而是编写电路生成器,然后再生成可综合的代码;

- Chisel可以发挥出Scala语言的面向对象特性,从而更好地编写参数化的电路生成器,还可以更好地复用组件;

- Chisel提供了较为丰富的组件库,可以直接在自己设计的硬件中使用;

- Chisel不仅能够提供较高等级的抽象,还能够对实现有细粒度的控制,区别于HLS,本质上还是个硬件构造语言;

为什么要提出Chisel?

Chisel的设计者们是这么说的(以下翻译自官网Motivation – “Why Chisel?”):

在我们的科研项目和硬件设计课程中,与现有硬件描述语言进行了多年的斗争,这促使我们开发一种新的硬件语言。Verilog和VHDL是作为硬件仿真语言开发的,直到后来它们才成为硬件综合的基础。这些语言的大部分语义不适用于硬件综合,事实上,许多结构都无法综合。其他结构在他们如何映射到硬件实现是很不直观的,或者说他们的使用可能会意外地导致非常低效的硬件结构。虽然可以使用这些语言的子集并且还能得到可以接受的效果,但它们仍然呈现出混乱和令人困惑的规范模型,特别是在教学环境中。

然而,我们开发新硬件语言的最强烈动机是我们希望改变电子系统设计的方式。我们认为,重要的是不仅要教学生如何设计电路,还要教他们如何设计电路生成器——从高级设计参数和约束自动生成设计的程序。通过电路生成器,我们希望利用设计专家的辛勤工作,为大家提高设计抽象水平。为了表达灵活和可拓展的电路结构,电路生成器必须采用复杂的编程技术来确定如何根据高级参数值和约束更好地定制其输出电路。虽然Verilog和VHDL包含一些用于编程电路生成的原始结构,但它们缺乏现代编程语言中的强大功能,例如面向对象编程、类型推断、对函数式编程的支持以及反射等。

我们没有从头开始构建新的硬件设计语言,而是选择在现有语言中嵌入硬件构造原语,我们选择Scala不仅是因为它包含我们认为对于构建电路生成器很重要的编程特性,还因为它是专门作为特定领域语言(DSL)的基础而开发的。

依然可以总结出来以下内容:

- Verilog和VHDL不适合硬件综合,而且用起来不直观,生成的硬件结构可能很低效,教学的时候很费劲;

- 希望可以改变电子系统设计方式——设计实现电路生成器而不是电路;

- 希望可以利用现代编程语言的各种优良特性,实现参数化、约束控制电路生成;

- Scala为DSL语言而生,团队也刚好需要Scala的特性,一拍即合,再次强调不是新语言,只是嵌入在Scala中而已;

- Chisel更倾向于学院派的东西,很大程度上是为了科研项目和教学,但还是希望能对业界有很大影响。

使用Chisel理论上有啥好处?

看了上面的内容,你可能对Chisel的好处有了一个简单的认识,那么具体有什么好处呢?这里我同样放上StackOverflow上的一个帖子:

What benefits does Chisel offer over classic Hardware Description Languages? – Stack Overflow

标题为:Chisel相比传统的硬件描述语言能提供哪些好处?

题主自述是个本科的IC(集成电路)设计学生,他认为Verilog已经是在工业界和学术界都有统治地位的成熟语言,有各种成熟的仿真工具支持,而Chisel并不支持Verilog支持的所有构造,比如模拟电路相关的元素,而Chisel提供的参数化生成器,在Verilog上也可以有等价实现。

确实他说的是有道理的,也提到了Chisel的部分痛点,现在我们来看看热心网友是怎么回复的呢?

总结下来有两大好处:

- 通过新的语言特性和可用的库提高生产力;

- 通过硬件编译器结构提高了专业化;

那么下面分别讲一讲这两个好处。

语言特性——最强有力的答案

我们可能看到过其它类似的问题,比如新手接触编程,可能会问“Python和C语言相比有哪些好处”,那有些人可能就会回答说Python并没有提供更多的功能,他们的观点是这样的:

- 任何能用Python写的东西C也能写,for循环、while循环什么的也都差不多,代码也差不多,比如

printf("Hello\n")和print("Hello\n"),真就区别不大; - C语言还有内联汇编的特性,Python就不行(注:虽然可以用PyASM包来实现,但是用法也比C复杂很多很多);

- 两个都是图灵完备的,所以没差(图灵完备是指机器执行任何其他可编程计算机能够执行计算的能力)。

但是上面的言论忽略了一个重要的事实,那就是Python提供了几种新的编程范式来提高生产力:

- 面向对象编程

- 函数式编程

- 丰富的库

这几种特性带来的就是更高的设计生产力和更好的代码复用性,因此可以将Python看成一种更强大的语言。

然而众所周知,如果在一群程序员中说xxx是世界上最好的语言,那么你们可能会打起来。Paul Graham(《黑客与画家》作者)在文章“Beating the Averages(打破平庸)”中提出了一个“Blub Paradox(灯泡困境)”,观点是“精通功能较弱的语言的工程师无法评估功能更强大的语言的效用”。

换句话来讲,上面说到的几点编程范式的存在并不是要强迫你去用,你完全可以编写出C味十足的Python(甚至直接以此为理由完全放弃使用Python!)。

那再说回Chisel,Chisel是一种领域特定语言(DSL),用于描述嵌入在Scala中的硬件电路。就其本质而言,它确实提供了和Verilog等效的结构,比如模块(Module)、输入/输出(IO)、寄存器(Reg)等。那如果按照提问者的观点,基本的Chisel确实和Verilog完全一样,你也完全可以把Chisel用成Verilog。这也经常称为反对Chisel支持Verilog的理由,但是这和根据“Hello World”示例的结构来选择编程语言有什么不同呢?

所以完全可以问出更好的问题:“我用Python写什么是用C很难写的呢?”那这个问题显然超过了“Hello World”比较的范围。举个例子,要是想在C或者Python中构建一个机器学习库,比如TensorFlow,那对于C来说就会很困难,因为TensorFlow需要很多抽象。

所以这个问题通过看成熟的Chisel项目就能看出来了,举两个典型的例子:Rocket-Chip和Diplomacy。Rocket-Chip是任意片上系统(System on Chip,SoC)设计的生成器,用Diplomacy来处理参数协商问题——在任意SoC中,我希望知道连接在一起的N个组件的参数来构造我想要实现的功能(比如地址宽度、内部逻辑、一致性协议等)。最重要的是,Rocket-Chip和Diplomacy都可以用作一个库(虽然目前还有些困难)。简单点说,就是Chisel程序员几乎可以像“import一个图形库一样”直接“import一个RISC-V处理器”!

那么现在问题就变成了评价语言特性和可用的强大的库,所以真正的实用指标应该是这样的:

- 我需要多少代码量来描述某个组件?

- 这个语言允许我构建的抽象层次够不够高?

- 这个语言对代码复用的支持程度如何?

最后再说不受支持的构造,比如说时钟下降沿触发和异步重置(Chisel和FIRRTL现在都支持异步重置了),Chisel都可以通过Verilog黑盒提供一个紧急手段(不知道翻译得合适不合适,原文是provides an escape hatch kludge)。但是说实在的,这些特性也就是开发人员举手之劳的事。

硬件编译器——另一个视角的答案

Chisel形成了硬件编译器框架的一部分,看起来很像是应用于硬件生成的LLVM。从Chisel到Verilog的过程构成了多阶段编译器:

- 首先是“Chisel阶段/前端(Front-end)”,将Chisel编译成叫作FIRRTL(Flexible Intermediate Representation for RTL,RTL的灵活中间表示)的电路中间表示;

- 然后是“FIRRTL阶段/中端(Mid-end)”,优化FIRRTL并应用用户自定义的转换;

- 最后是“Verilog阶段/后端(Back-end)”,基于优化后的FIRRTL发射(emit)Verilog。

虽然很微妙,但是这种编译器结构可以实现以下功能:

- 前端和后端是解耦合的,意味着可以编写其他前端和后端,比如利用Yosys可以有Verilog的前端,其他的语言可以直接以FIRRTL为目标,比如Magma是Python中类似Chisel的语言,可以以FIRRTL为目标。新的前端可以获得中端优化和可用后端的所有好处;

- 也可以编写新的后端,例如VHDL后端只需要一个有动力的开发人员去编写;

- 电路IR(Intermediate Representation,中间表示)的引入实现了电路的电路的自动专门化或变换。这个特性已经被用来将电路转换为运行速度比未优化版本更快的FPGA优化版本(Midas和FireSim)、启用硬件断点/断言(Dessert)、添加运行时可配置故障注入功能(Chiffre),而直接在Verilog上实现这些很复杂,而且实现了也是很脆弱的;

所以从这个角度来看,这个问题更接近于“C++和LLVM相比汇编语言提供了哪些好处?”

在讨论编译器的时候,通常会出现Chisel和HLS的比较问题。而他们的不同之处在于,Chisel从本质上来说仍然是一种用于描述电路的强大语言,而HLS是一种将程序转换为电路的过程。

总结一下

对于Chisel和Verilog的比较,Chisel到底比Verilog强在哪些地方很难比较,需要比较两种语言的编程范式集合。而回答哪个更好的最好方法是深入研究成熟的Chisel代码库并且尝试自己去用Chisel(几个月之内不要做判断),这是需要时间的。而且硬件工程师通常很精通C语言,但可能从未(或从未深入了解)面向对象编程、函数式编程或者利用现代软件工程原理编写过复杂项目,这会导致他们有偏见。正是这种偏见存在,所以大多数人都在努力寻找反驳Chisel(或其他类似语言)的理由,而不是使用它的理由。

使用Chisel实际上真的有那么好吗?

实践出真知,上面理论分析了那么多,那实际应用怎么样呢?

这里就不举例说哪些用Chisel写的开源SoC实现源码了,我们把目光转向国内的中科院计算所,他们是最早吃螃蟹的人。他们组织的“一生一芯”计划已经办到第四期了,相信第一批在几个月做出成功流片的果壳处理器(Nutshell)的那群本科生已经刷屏很多次了。而他们在CCF A类推荐期刊《计算机研究与发展》上发表的文章芯片敏捷开发实践:标签化RISC-V (ict.ac.cn)通过实践验证了Chisel带来的生产力提高。

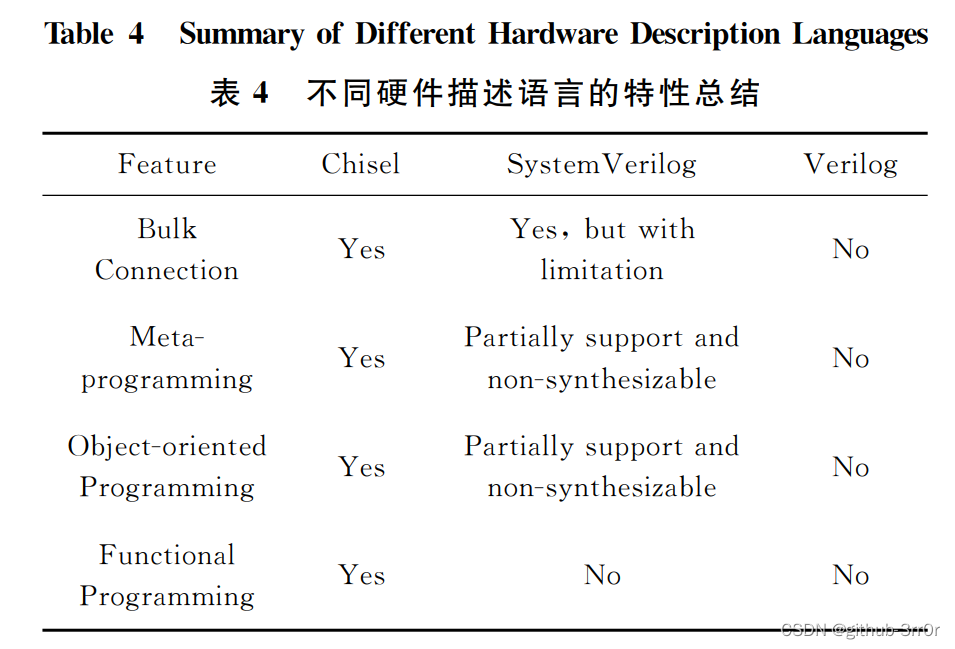

首先放上他们对Chisel、SystemVerilog和Verilog着三种语言的特性总结:

其中,“Bulk Connection”表示信号的整体连接,“Meta-programming”表示元编程,“Object-oriented Programming”表示面向对象编程,而“Functional Programming”表示函数式编程。可以看到,Chisel对于这些特性的支持都是最好的。

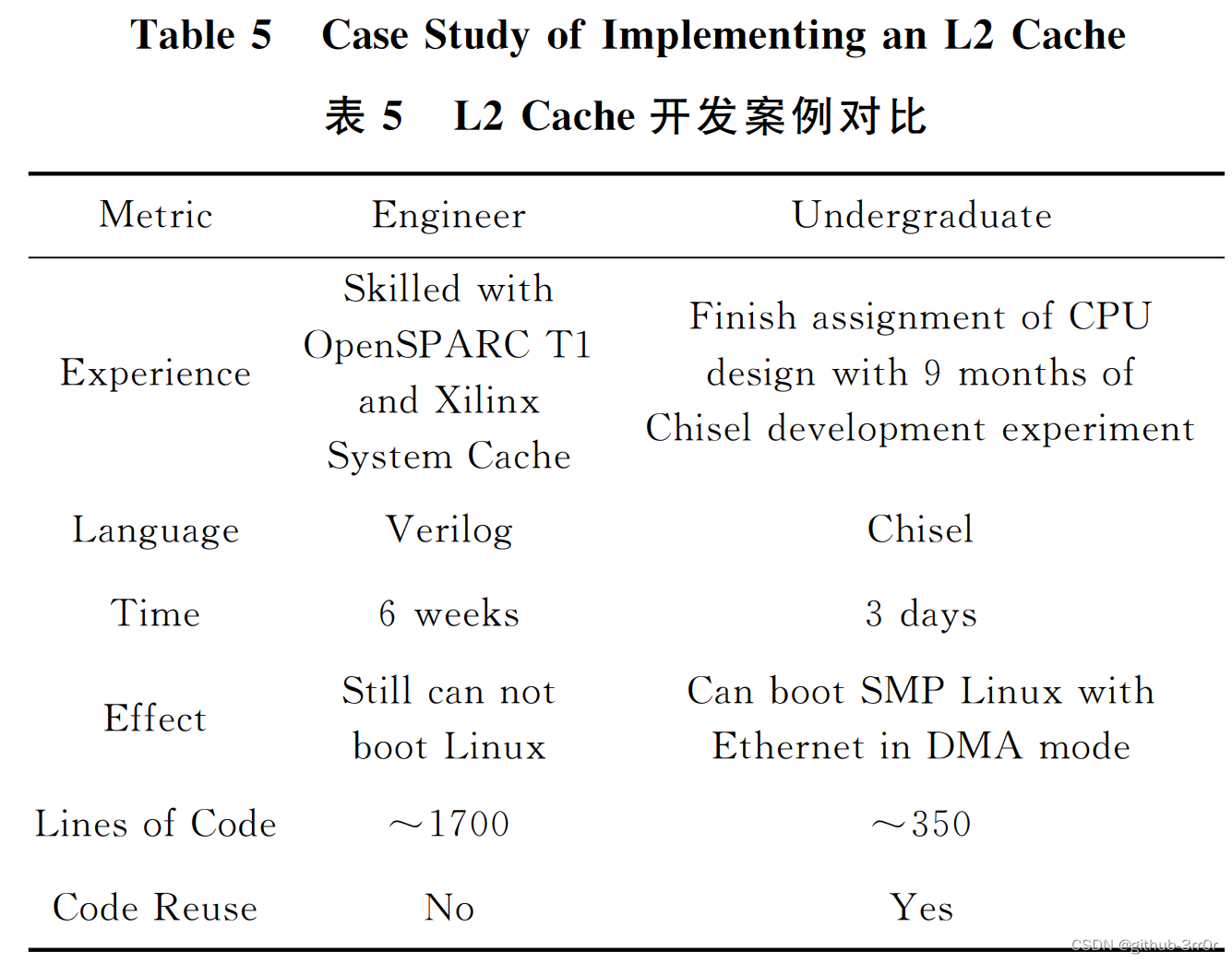

那么实践效果如何呢?他们以一个二级缓存为例分别用Chisel和Verilog来实现,先放上编码效率的实验结果:

下面文字描述一下,首先出场的是对OpenSPARC T1和Xilinx System Cache有深入了解的工程师,他使用传统开发模式,选择了Verilog语言开发这个二级缓存,从零开始搭建环境,不复用任何代码。最后他耗费了七周时间,代码行数约1700行左右,然而遗憾的是,他开发的缓存不能支持成功运行Linux。

第二个出场的是一位完成了CPU设计课程、有九个月Chisel开发经验但从未设计过二级缓存的大四本科实习生,他选择使用Chisel语言来开发这个二级缓存,并使用Chisel的标准库来帮助设计。最终他只花了三天的时间,代码行数约为350行,支持了通过DMA模式的以太网启动SMP Linux。而且,他写的代码还能够复用!我只能说高下立判。

其中还有个插曲,工程师在开发过程中为了编写一个端口数量可配置的总线连接配置代码,在generate特性的基础上用了一些特殊技巧实现了这个功能,大概250行Verilog代码。但是因为连线和数字下标太多了,还需要顾及总线握手协议,一时疏忽就导致了两个连线错误的bug,结果这个bug花了三天时间才发现并修好。另外,那一部分的特殊技巧的代码可读性很差,即使有注释,一周之后的工程师也不能立马理解他自己的代码了。而如果使用Chisel只需要编写两行代码就能实现该功能,而且可读性好,几乎不会出现错误。而那个本科生其实写完只花了两天,一周之后重新阅读代码修一个bug也只花费了一天。

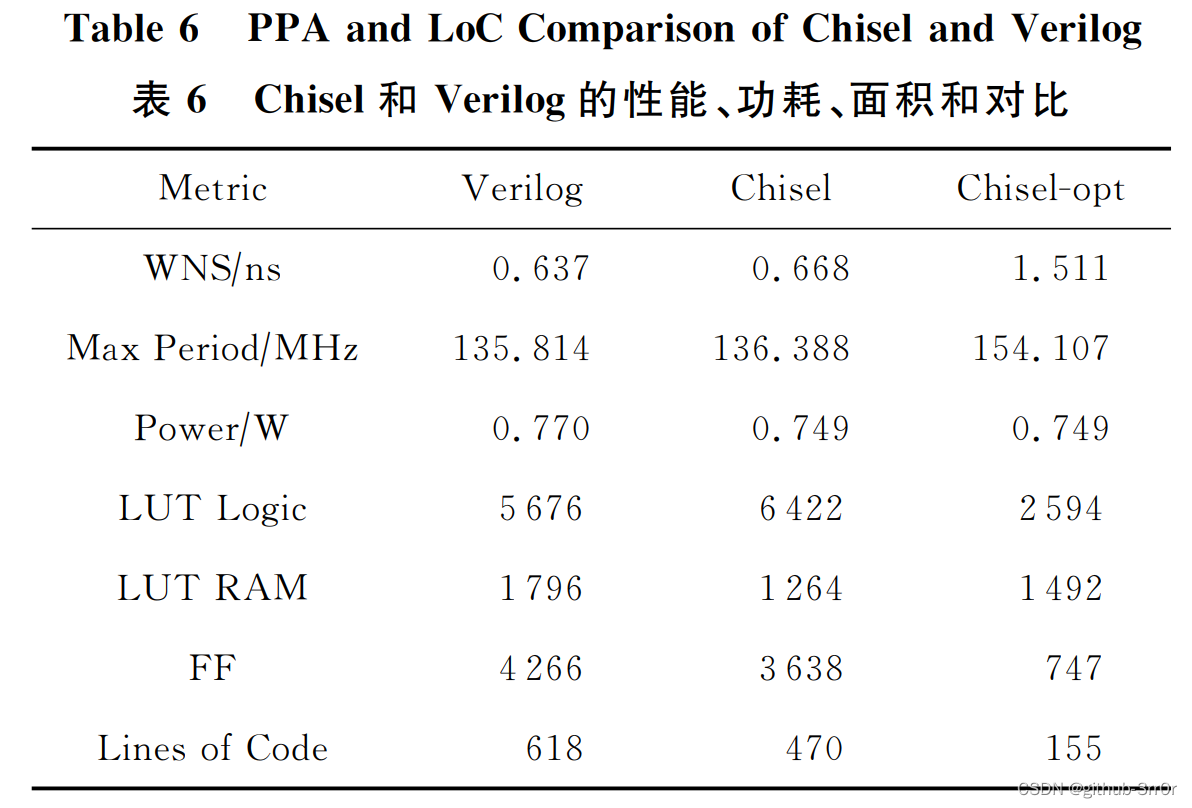

再看看编码质量的对比,毕竟不能光快但是生成的代码质量不行吧:

其中,Verilog是工程师写的那个,Chisel是找了一个没有任何Chisel开发经验的学生,逐字逐句用最简单的Chisel原语“翻译”了工程师的代码,而Chisel-opt是该学生上手之后,使用Chisel的高级语言特性重构了实现的代码。通过对最终生成的网表进行对比,可以看出是全面吊打:

- 最差负时序余量(WNS,单位ns)远好于Verilog,换算成最高可运行频率(Max Period,单位MHz)也有了很大提升;

- 在功耗方面节约了2.73%,还行;

- 使用的查找表(LUT,Lookup table)和触发器(FF,Flip-Flop)数量大大幅减少!

- 网表的代码行数也大幅减少!

可以看到结论是显而易见的,一个新手Chisel程序员,就可以利用Chisel的各种特性,在更短的时间内,以更少的代码量,编码质量与老练工程师相当甚至更好,展现出了很高的价值!

那还在等什么,赶快来学Chisel吧!

Chisel有哪些缺点?

Chisel这么好用,但是肯定也还是有缺点的,总结如下:

- 学习曲线比较陡峭,没有面向对象编程、函数式编程经验的人学起来会费劲;

- Chisel的相关资料比较少,我写的上一个系列的博客阅读量寥寥,愿意写的人也少;

- EDA工具对Chisel的支持并不完善,如果生成Verilog代码再去验证、调试,代码可读性很差,难以调试;

前两个问题都是可以解决的,毕竟有我正在做的这个系列呀,争取深入浅出把Chisel讲明白!

至于第三个问题,压根儿就不属于学习上的困难,我们学习的时候完全可以忽略。

总结

全文看下来,优点说了很多,缺点没写几行,说明Chisel还是很不错的。接下来就要正式开始学习了,Chisel说难真的不难,就算真的难吧,记得一句话——“道阻且长,行则将至”,毕竟我们后面还要用Chisel去实现一个较完备的处理器呢,这可是计算机体系结构的黄金时代啊。

今天的文章vhdl与verilog的哪个流行_verilog用什么软件编写分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/85962.html