产品可靠性设计-静电放电ESD的测试与整改-3

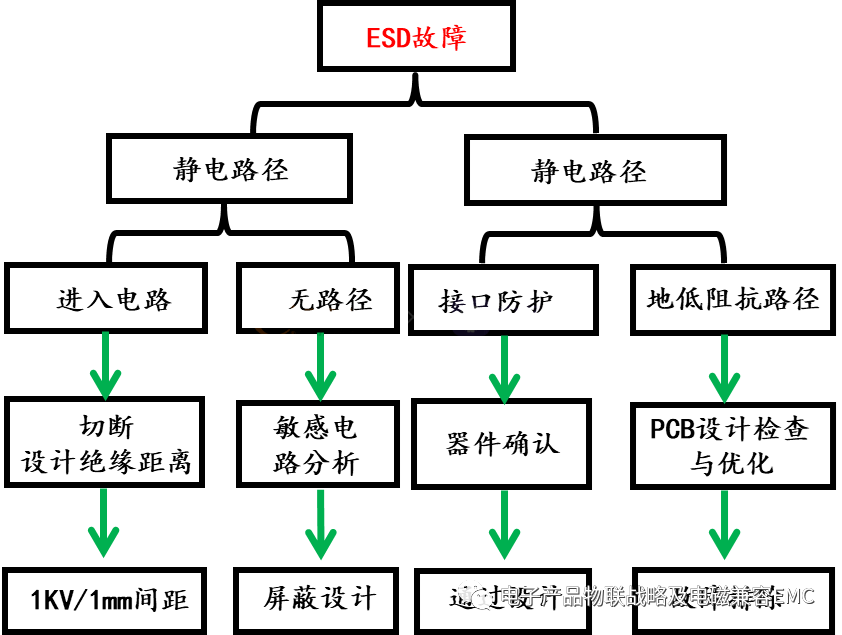

ESD静电放电的故障诊断与整改

1.典型的解决方法

很多方法都能阻止ESD电流脉冲或让电流脉冲通过产品安全地返回系统将其转移到大地。

串联设计,比如铁氧体磁珠、共模扼流圈和小阻值的串联电阻器。可用于阻止或减小电流脉冲。

并联设计,比如电容器件、反偏的二极管、火花隙或气体放电装置,当跨接在数据线上时,可将大部分的ESD电流转移至外壳平面或安全地。

对于外壳平面,并不需要其是一个完整的平面,也不需要其位于底层或中间层上。使用外壳平面最有效的方法之一是,在所考虑的连接器的某一侧的两个电路板安装点之间布置一条宽的PCB走线。这条PCB走线应搭接到这些安装点上。PCB走线应位于平面的顶层表面上且使其与连接器的插针保持安全距离。对于所考虑的每个插针和每条PCB走线,应安装合适的瞬态抑制器件,并且与外壳PCB走线之间的距离应非常短。这将会形成一条安全的和低阻抗的路径以泄放掉ESD电荷。

在进行设计时将大部分的ESD电流转移到大地,也不要影响数据线路的信号完整性。

(1)在可疑电缆上加装铁氧体是最快的,通常也是最先想到的方法。一定要确保这些铁氧体的位置放置尽可能地靠近产品的I/O连接器或电源连接器。

(2)对于I/O线缆、信号线或电源线需要使用低通滤波器。好的设计是在信号线上串联47Ω~100Ω的小电阻,同时在信号线与返回线或电源返回线之间使用1~10nF的电容。如果有可能,滤波器一定要使用最短的线缆。如果滤波器直接设计在PCB板上,高频时推荐使用贴装的器件。

(3)确保外壳或壳体没有产生泄漏。可能需要增加紧固件的数量。壳体也可能需要使用附加的射频衬垫。

(4)可能需要在呈现敏感的内部电路节点上跨接1~10nF的电容器件或RC滤波器。比如,连接任何CPU的复位输入的电路。

(5)对于内部PCB相连的所有I/O连接线和电源线,最终的解决办法是设计瞬态电压抑制器件TVS。PCB需要尽可能地在接近I/O连接器处与外壳进行好的射频搭接。

(6)对于非屏蔽壳体,增加一个金属平板,所有I/O和电源连接器的外壳应与它的一面进行连接。

对于高速数据线,可以使用的两种最佳技术为陶瓷ESD装置和硅ESD装置。陶瓷防护装置的电容值非常小,大约为0.05pF、耐压非常高且寿命长。

对于8KV的ESD脉冲,他们可将峰值电压限制到300V,钳位电压为40V。硅ESD装置的电容值稍大点,为0.25pF。其优点是具有非常快的开通时间,可将峰值电压限制在50V以内。钳位电压为8~10V。

2.特殊情况及问题分析

对于没有金属壳体的产品或EUT,ESD抗扰度的设计值得关注。其设计方法:可以在会导致任何元器件出现敏感ESD电流路径上增加串联阻抗,以及在想让ESD电流离开产品的位置处增加低阻抗的转移路径。

(1)最佳的方法是在所有I/O连接器上设计瞬态抑制器,它可以将电流脉冲转移到PCB的外壳平面。

(2)I/O线加装共模扼流圈。

(3)在电缆上非常靠近连接器处设计铁氧体扼流圈能减小一部分电流脉冲。

(4)在信号线到PCB外壳平面之间或信号线到安全地导线之间接并联电容1nF/10nF,能有助于转移ESD电流。

(5)确保PCB周围的ESD电流能被转移的一种非常好的方法是,通过在PCB的下面增加金属平板(或者是金属背板)。这种金属平板应与所有I/O连接器的导电后壳及外壳进行连接。ESD电流将能从金属平板泄放到大地。

通过软件设计也可能使产品对ESD产生固有的抗扰度:

(1)不要使用无限的“等待”状态。

(2)在适当的情况下,使用“看门狗”程序让EUT重启。

(3)使用校验位、校验或纠错码,以防止存储损坏数据。

(4)一定要确保所有的输入为锁存的和选通的;不能为浮点的。

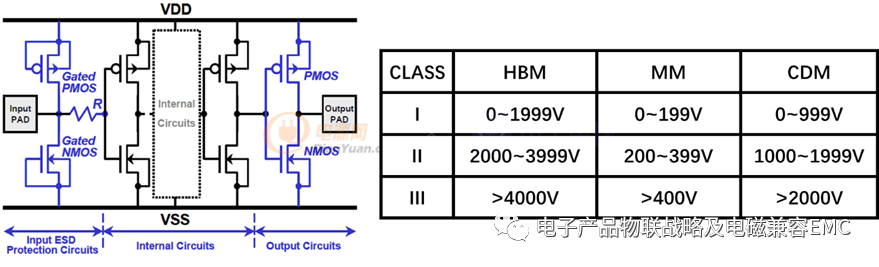

3.IC芯片产品ESD设计与优化

Ø增加用于保护内部线路的ESD保护电路,使其可承受较大的电流。

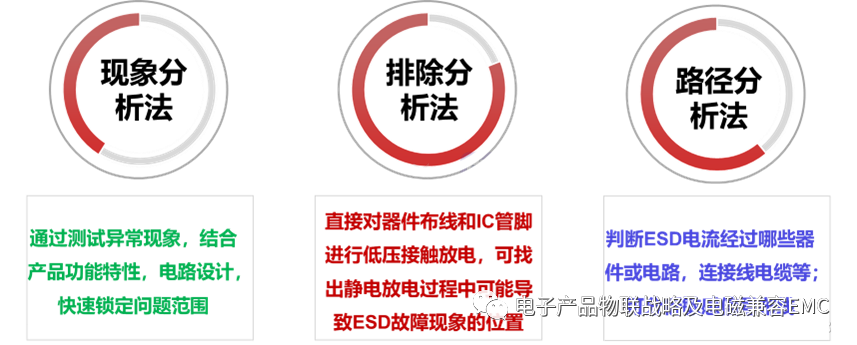

在实际产品及设备上进行ESD测试与整改时的基本方法:

堵;

从机构上做好静电的防护,用绝缘的材料把PCB板密封在外壳内,不论有多少静电都尽量不释放到PCB板及内部电路。

导;

有了ESD,迅速让静电能量导到PCB板地的低阻抗上,做好PCB设计可以消除一定能力的静电放电电流。

电路的设计采用堵和导的方法:

1.MCU控制芯片的电源和地的滤波设计

2.接口电路的电源滤波及信号电路的R,C滤波

3.驱动器I/O发送和接收端的电阻R,阻容RC的反射及串扰控制

4.PCB的信号回流和电源与地回流面积的控制;

在PCB板级的ESD防护设计技巧:

A.规划静电电流泄放路径,为静电电流泄放提供安全可靠的低阻抗泄放通道。

B.减小地电位差,为信号提供稳定的工作电压与稳定的电平传输。

C.控制好信号的环路面积减小寄生电感。

5.把干扰泄放到大地或者对地阻抗最小的点上;

6.减小干扰进入PCB内部电路的能量;

7.增加被干扰电路的高频阻抗;

8.对敏感的器件或电路进行防护;

9.加强绝缘击穿距离;

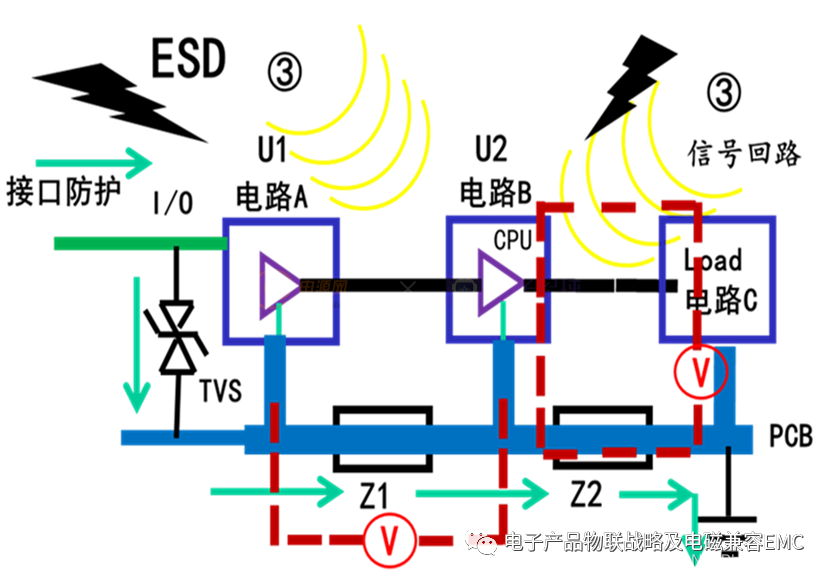

注意:当静电放电ESD干扰信号通过耦合方式到达电路板内部的时候,如下图所示:

注意:PCB的设计地走线,地回路,接地点的位置设计也是解决抗扰度ESD设计最关键的设计方法与思路。

目前行业内最典型的EMS敏感度的设计也都跟这个结构图相关联。

产品问题的发生也是跟我们产品设计可靠性相关联的。

声明:本内容为作者独立观点。未经允许不得转载。授权事宜与稿件投诉,请联系:editor@netbroad.com

今天的文章esd静电放电抗扰度试验测试方法_esd保护电路设计分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/86682.html