1、基本设置

1.1.快捷键设置

在env文件中添加快捷命令,

若不知道当前的用户环境变量路径,可以在Command窗口里输入: echo $localenv

路径:D:\Cadence\Cadence_SPB_16.6\share\pcb\text 全局变量

D:\SPB_Data\pcbenv 用户变量

命令示例:

funckey w add connect

funckey s slide

funckey d delete

funckey r rotate

funckey m move

funckey a delay tune

funckey z

oops

funckey e done

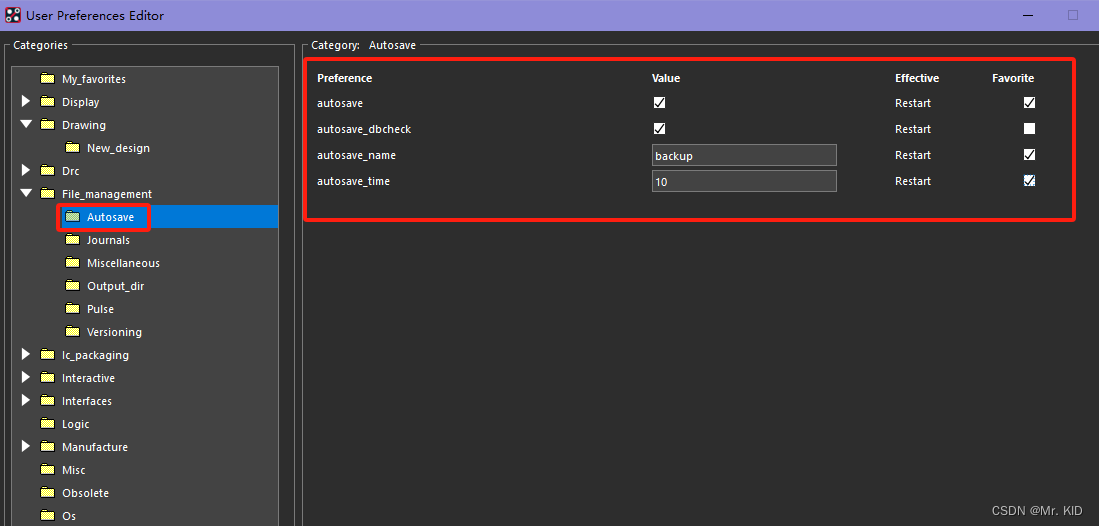

1.2、自动保存

点击Setup菜单→User Preferences…(用户参数设置)

Autosave:是否开启自动保存,若需要开启,选中。

autosave_dbcheck:自动保存前是否进行dbcheck,选中保存时间可能会长几秒。因为保存前要进行校验,可以不选。

autosave_name:设置自动保存的文件名,会在当前pcb目录下生成一个以该命名的文件。

autosave_time:设置自动保存的间隔时间,单位分钟。可设置10-300分钟。这里设置10分钟。

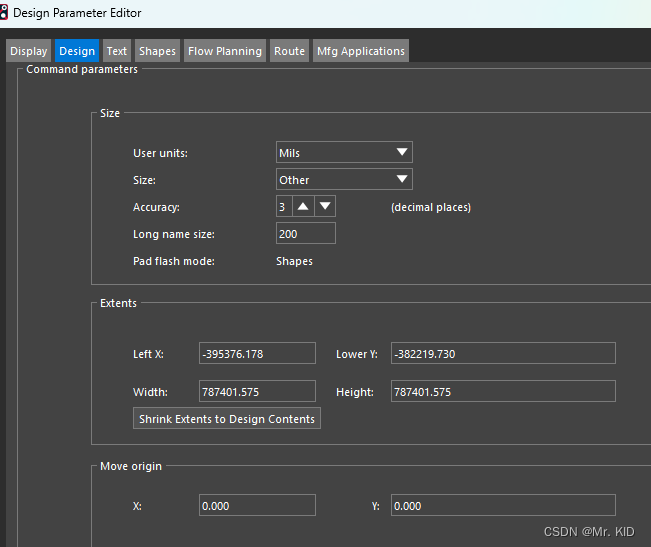

1.3、精度设置

单位精度设置:setup–》design parameter edit–》design

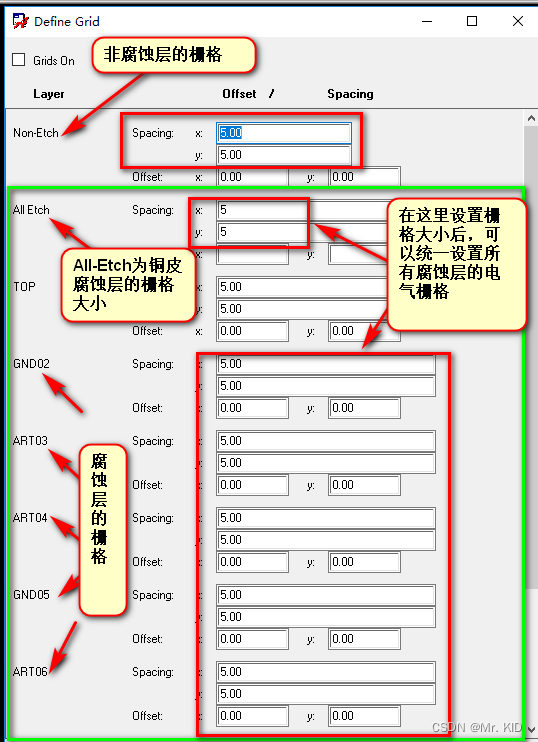

栅格设置:setup–》grids

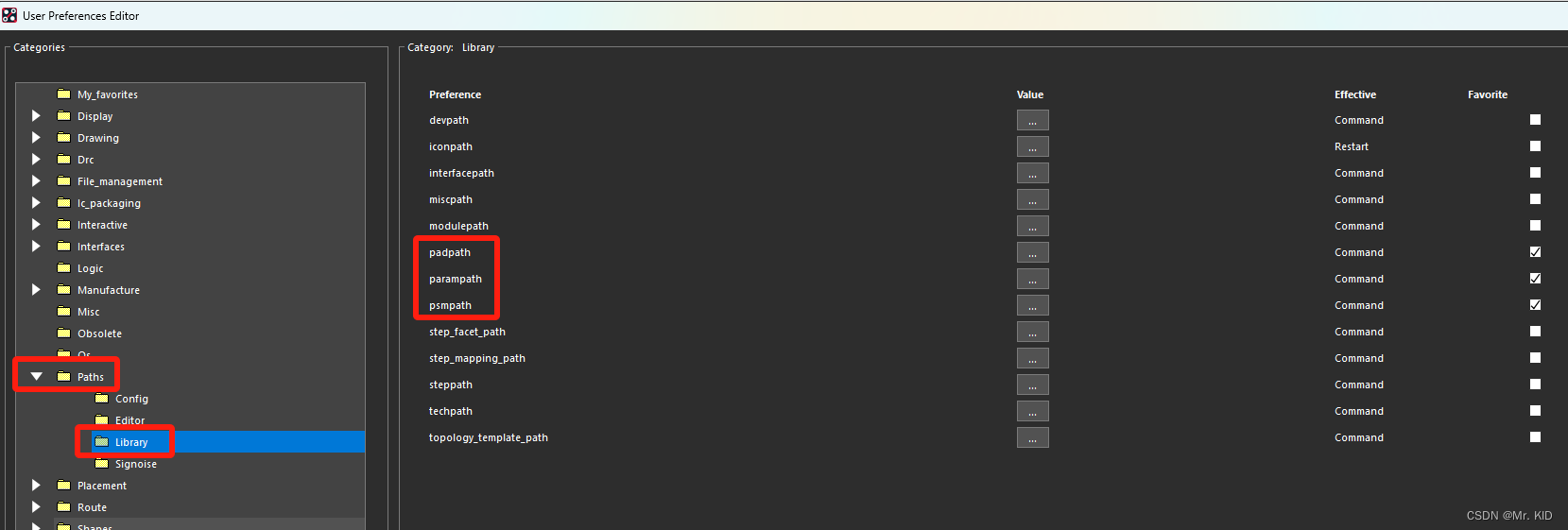

1.4、封装路径设置

封装库路径设置:setup–》user preferences–》paths–》library

封装库需要包含:.dra .psm .pad文件

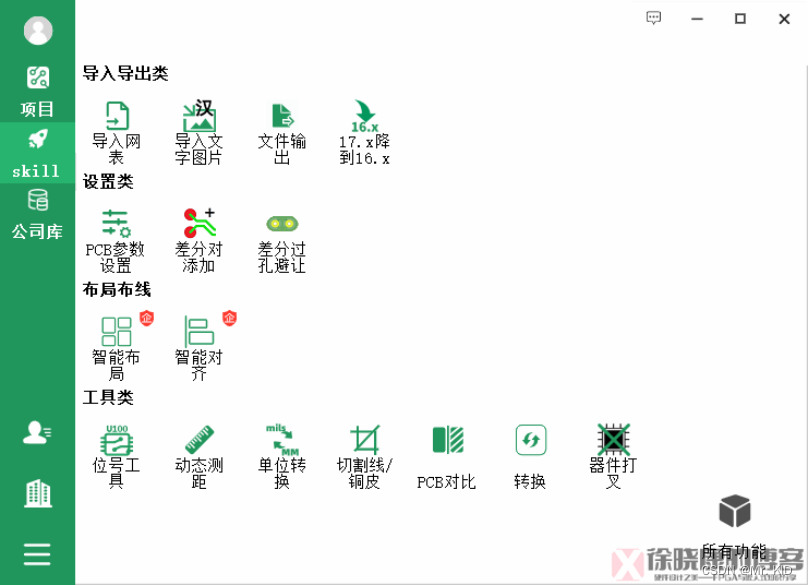

2、SKILL工具

电路精灵、EDA365等skill工具。可添加反焊盘,drc检查,一键生成gerber等。

EDA365电子工程师网-中国电子技术论坛,硬件设计论坛,PCB设计论坛,layout设计论坛,EDA论坛,电子工程师乐园,单片机,电子电路,嵌入式系统,DSP,嵌入式系统,PCB,数字信号处理,网络通信,工艺制造封装,测试测量

官网下载地址: 电路精灵 (

tech-gyro.com)

3、板框绘制

3.1零点设置

一般会将图纸的左下角设置为零点: setup–》change drawing origin–》在command输入零点坐标。

3.2板框绘制

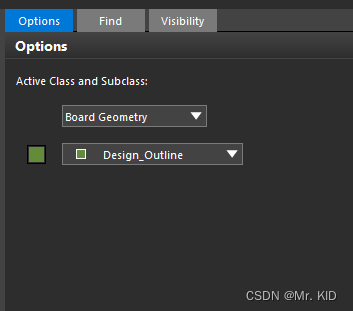

board geometry–》outline(design_outline)–》add line(线宽设置为6mil)

在命令框输入x 0 0(抓取零点位置)–》iy 9600 –》ix 12000–》iy -9600–》ix -12000 (画边框的顺序:必须先上移再右移 再下移再左移)

ATX 305X244mm 板框绘制完毕

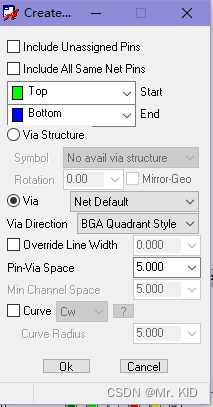

4、Fanout-自动扇出

BGA封装器件可选择自动扇出。

Route->create fanout

在右侧options选择top-bottom(注:这里不选择后面无法选择过孔),选择扇出的过孔类型,再选择过孔扇出的方位,扇出长度等。如图:

注意扇出时选择pin会单个扇出,选择symbol会整个symbol pin全部扇出。

5、shape命令

Polygon:使用此命令绘制多边形铜皮;

Rectangular:使用此命令绘制矩形铜皮;

Circular:使用此命令绘制圆形铜皮;

Select shape or void:选择shape,常用来给shape赋予网络属性,用select shape or void命令选择shape后点右键选择assign net,在右边options里输入网络名即可;

Manual void:这个在下拉菜单中可以选择几个不同的命令,如下所示:

lPolygon:在一个完整的铜皮中挖掉一个任意形状的洞;

lRectangular:在一个完整的铜皮中挖掉一个矩形的洞;

lCircular:在一个完整的铜皮中挖掉一个圆形的洞;

lDelete:将已经避让的铜皮恢复,或者将用manual void/ polygon挖掉的的铜皮恢复;

lElement:避让命令,如果铜皮的网络和孔的网络部一样,用该命令避让;

lMove:将避让后的shape的一个轮廓移动到shape的其他地方避让,原来避让的shape即还原;

lCopy:将避让后的shape的一个轮廓复制;

Edit boundary: 修改shape的大小,切割shape;

Delete islands:删除孤岛铜皮;

Change shape type:改变铜皮的属性,修改shape为静态或者动态的,静态的铜皮不能避让,动态的铜皮是可以避让的;

Merge shapes:将两相同网络的shape合并,或者将一无网络的shape和一有网络的shape合并;

Compose shape:将一些不是封闭的line属性的线改变成为shape,此命令多用于将板框进行合并处理;

Decompose shape:与Compose shape是相反的,将铜皮属性的变成闭合的line属性;

Global dynamic params:此命令常用来选择过孔和shape的连接时以全连接还是以花焊盘连接。进入global dynamic params菜单对话框,选择thermal relief connects ,将三个选项都选为full contact 为全连接,都选为orthogonal为花焊盘连接。

6、模块、走线复用

6.1.模块复用

切换到placement edit模式–》框选已布局完成模块器件net–》右键place replicate create–》右键done–》左键输入模块名

框选相同模块器件–》右键place replicate apply–》选择刚创建的模块

6.2.sub-drawing走线复用

导出sub-drawing:file–》export–》sub-drawing–》选择需要复用的clines–》设置参考点,在命令行输入器件1pin坐标‘x 0 0’-》按下enter,保存为.clp文件。

导如sub-drawing:file–》import–》sub-drawing–》 选择刚才保存的文件,点击OK。–》导入后会有个框,直接在命令行输入同一器件同一pin的坐标“x 1 1”,Enter便可。若两个图纸完全相同,输入零点坐标x 0 0,即可。

(需注意clp文件与brd文件需放置在同一文件夹。)

7、平移命令

框选器件,move–》命令行输入

ix 5000 右移

ix -5000 左移

iy 5000 上移

iy -5000 下移

8、调节差分对间距线宽

Allegro pcb快速调整差分对线宽与线距 (pcballegro.com)

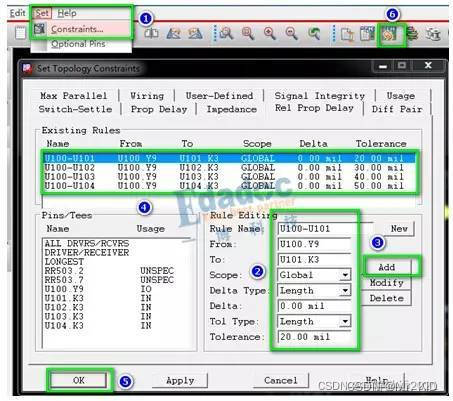

9、设置等长的3种方法

1.选择目标网络,右键–》create–》match group

将最长的走线设置为target,设置等长范围。

2.pin pair点到点

选择目标网络,右键–》create–》pin pair

选择目标网络pin pair–》create–》match group

设置等长范围。

3.sigxploer

选择目标网络,右键–》create–》net group

选择建立的net group–》右键–》选择SigXploer命令,打开SigXploe,按照图示进行设置。

如果SigXploe有各种问题,直接用方法2,简单明了。

Allegro走等长线设置_cadence allegro等长_宁静致远2021的博客-CSDN博客

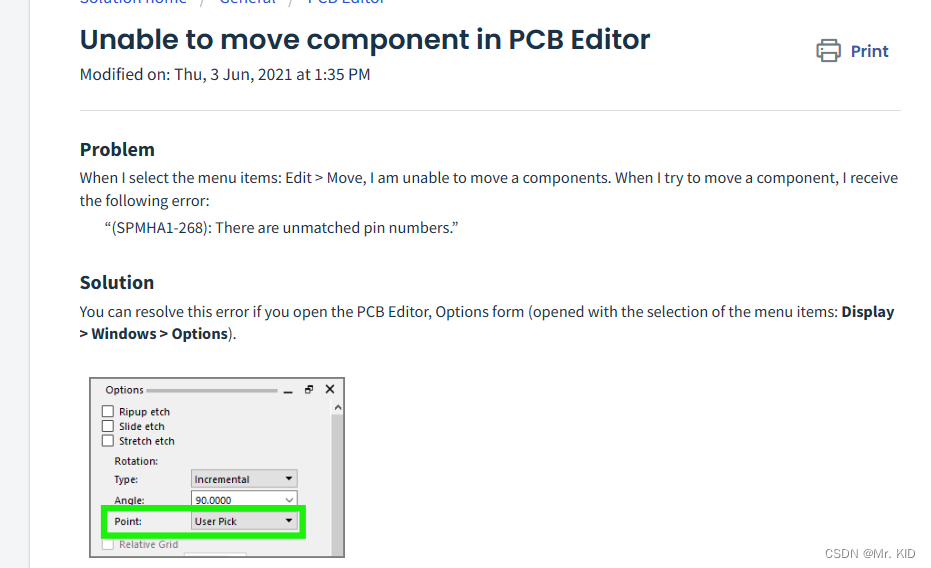

10、常见问题

1.there are unmatched pin number?无法移动器件

2.死铜删除与重新覆铜

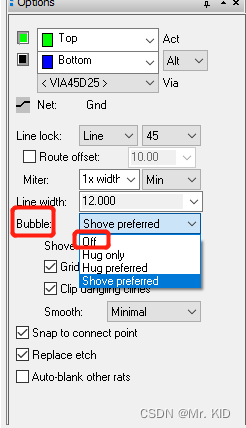

3.出线会自动避让,无法顺利出线

将bubble 设置为off,可顺利出线

BUBBLE -> shove perferred 推挤

-> hug only 抱紧

-> hug perferred 抱紧

-> off 关闭

shove vias 推挤过孔

-> off 关闭

-> minimal 最小值

-> full 推挤

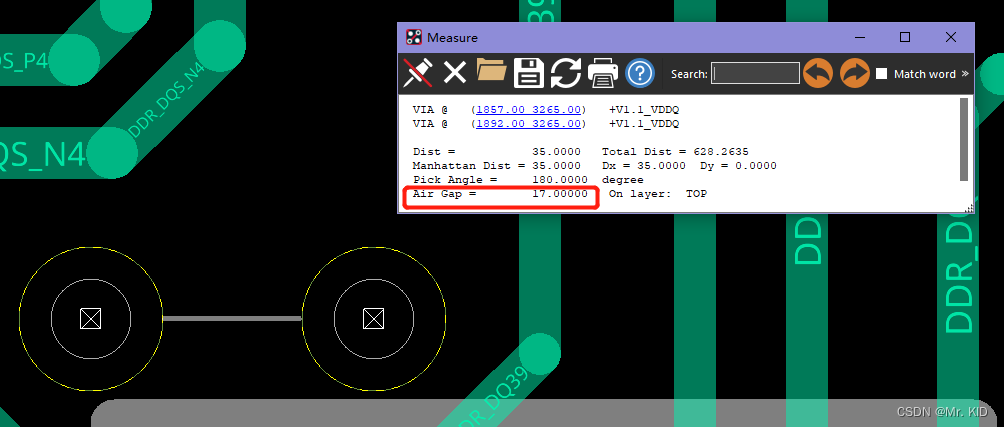

11、Air Gap,Dist说明

air gap为过孔边沿的距离为17mil

dist 为过孔中心距离,包含焊盘半径。

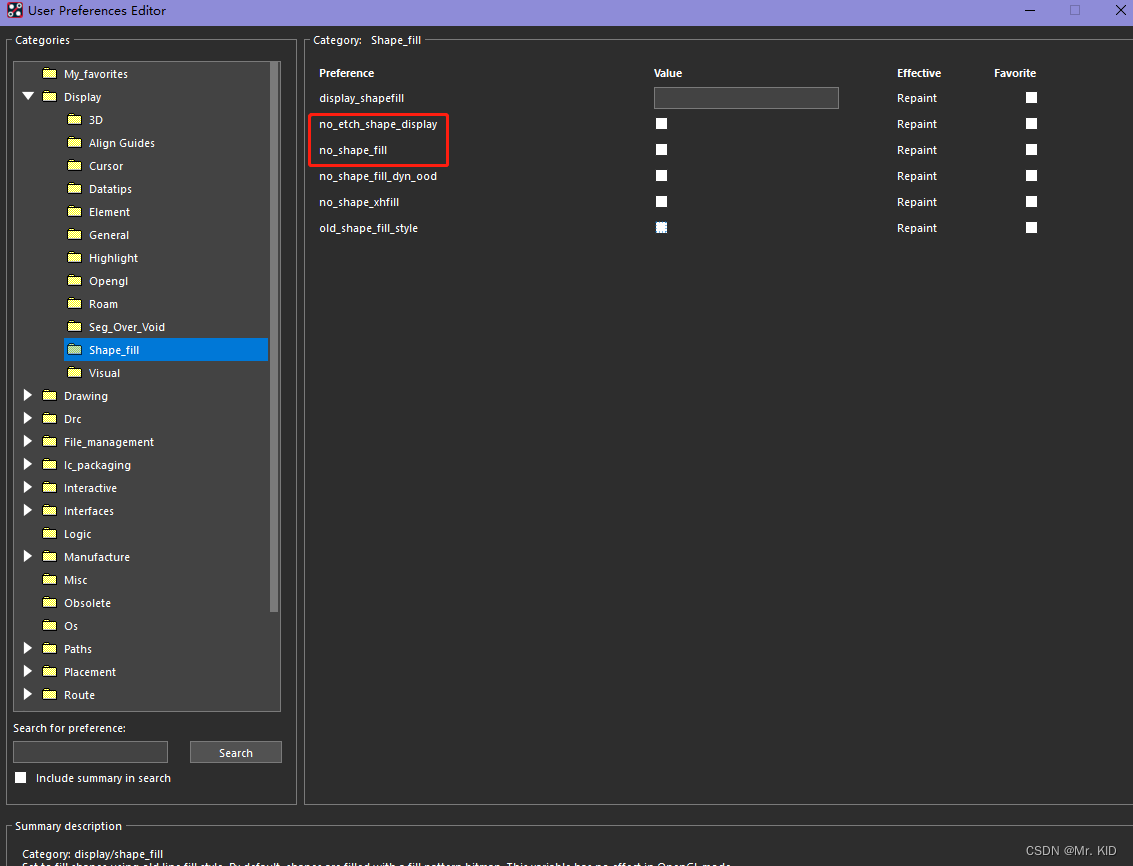

12、Shape铜皮显示设置

不显示shape铜皮或只显示shape边框:

Setup -> User Preferences-> Display选项下的 shape_fill,勾选对应的选项即可实现:禁止铺铜显示还是显示铺铜边框功能。

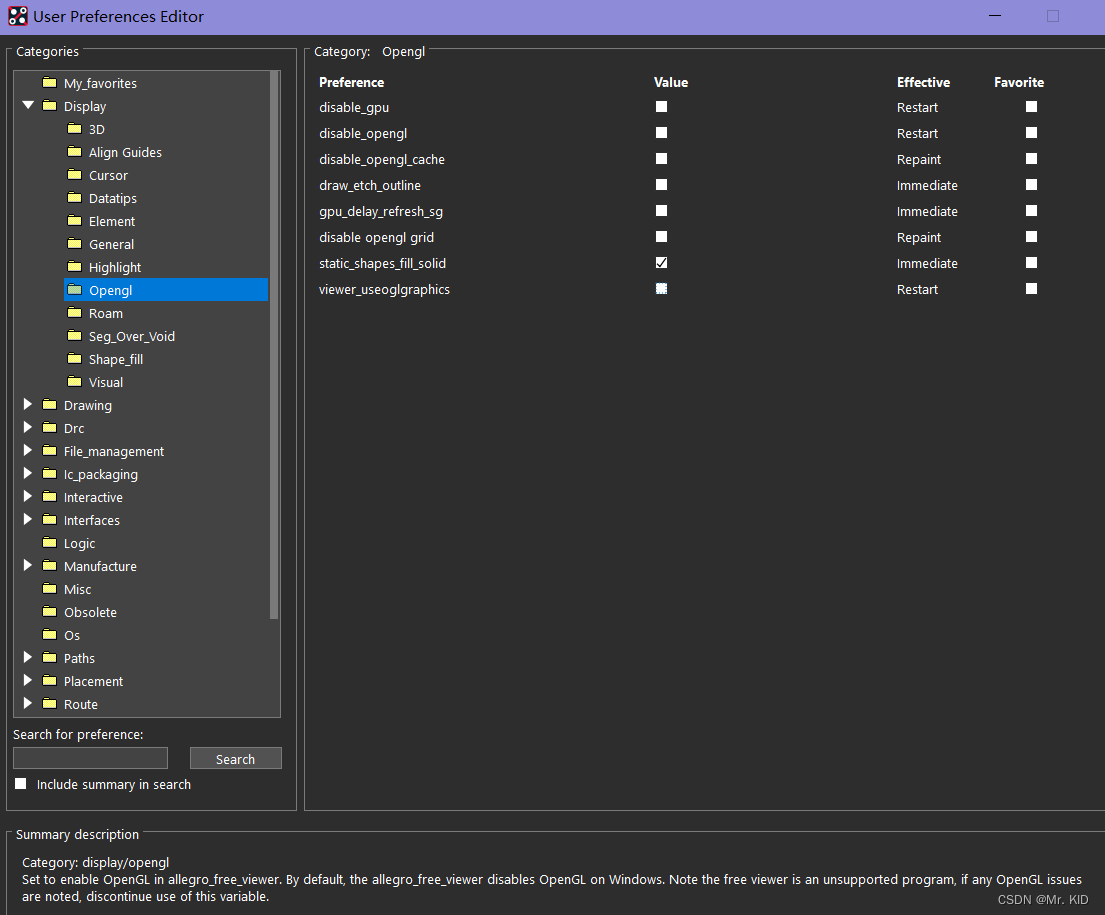

显示shape实体铜,而不是网格铜:

Setup -> User Preferences… -> Display选项下的openGL -> 勾选”static shape fill solid”

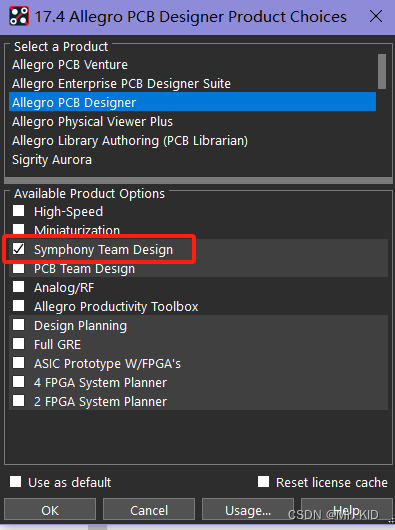

13、Allegro17.4 Symphony协同布线

打开allegro选择symphony team desgin模式

file–》start symphony server–》open需协同的.brd文件–》分享ip

从机连接–》file–》symphony connect–》输入ip 点击连接

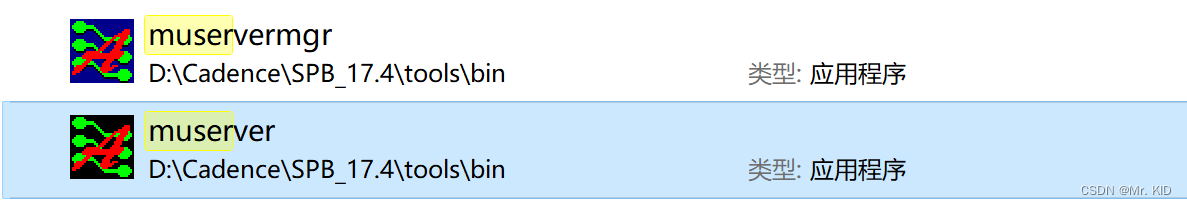

若按照上述操作,部分主机启动连接后会卡死,可先打开muserver程序,再进行分享。

今天的文章allegro基本操作_allegro快捷键大全分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/86881.html