声明:作者是做嵌入式软件开发的,并非专业的硬件设计人员,笔记内容根据自己的经验和对协议的理解输出,肯定存在有些理解和翻译不到位的地方,有疑问请参考原始规范看

Escape Mode是使用Low-Power状态的Data Lanes的一种特殊操作模式,用这种模式可以实现一些特殊的附加功能。Escape Mode要在Forward Direction上支持,Reverse Direction上则是可选项。支持Escape Mode并不意味着必须包含其所有可用的特性。

Data Lane通过Escape Mode Entry过程(LP-11,LP-10,LP-00,LP-01,LP-00)进入Escape Mode。一旦在线路上观察到了最后的Bridge状态(LP-00),Lane就进入了Escape Mode并处于Space状态(LP-00)。在最后的Bridge状态之前的任意时间,如果检测到了LP-11,则Escape Mode Entry过程会被打断并且接收侧会等待或者回到Stop状态。

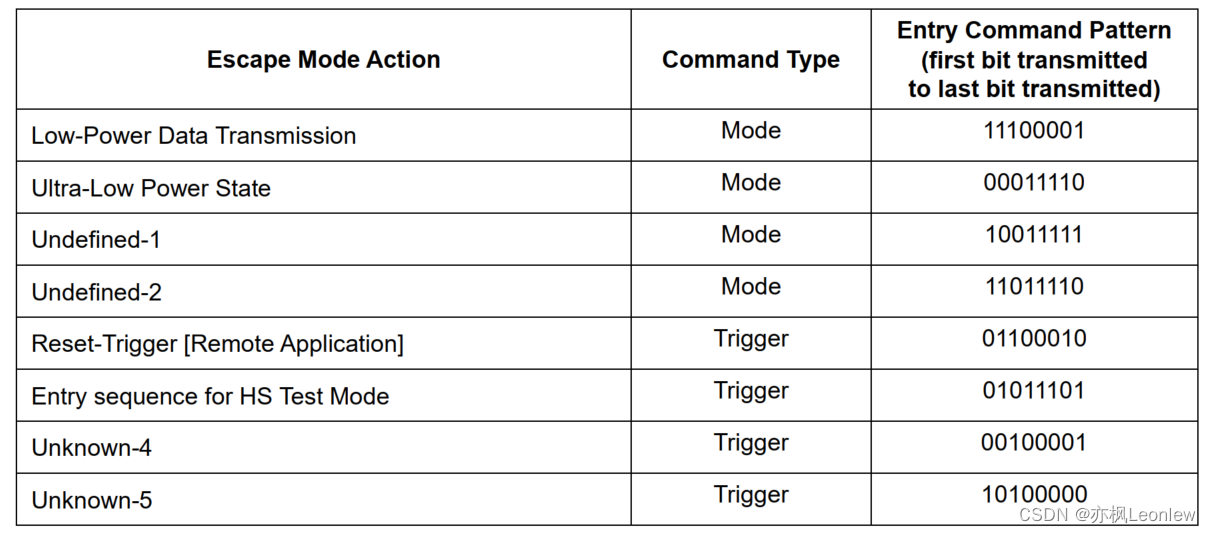

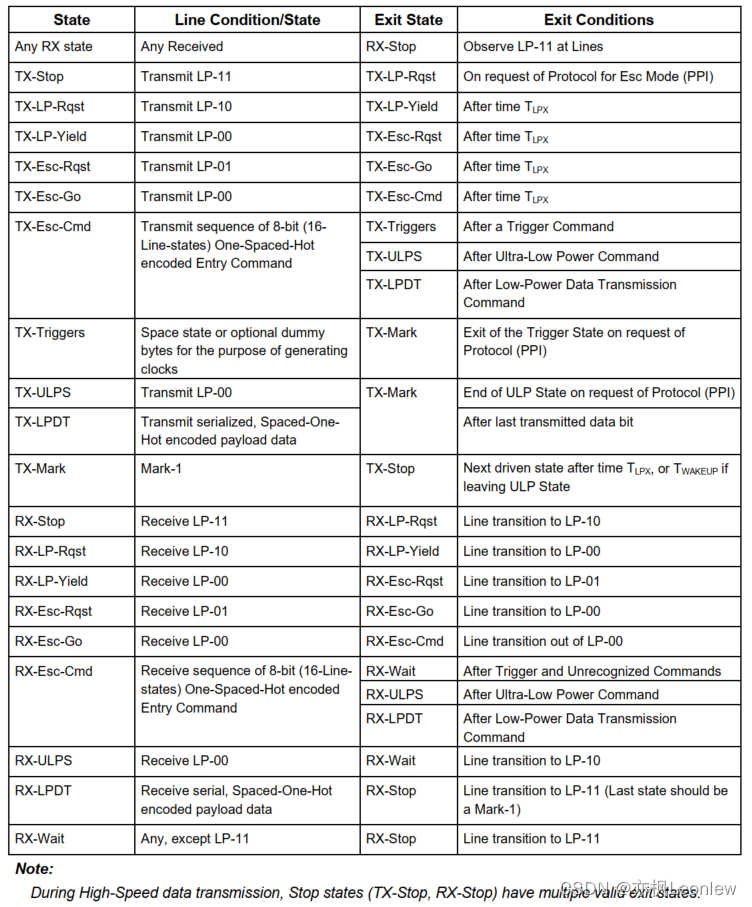

对于Data Lanes,一旦进入Escape Mode,发送端要发起8-bit的entry命令来表示要请求的动作。下表列举了所有目前可用的Escape Mode命令和动作,没有被分配的命令保留给未来使用:

图1 Escape Entry Codes

Stop状态用来退出Escape Mode,由于Spaced-One-Hot编码的缘故,Stop状态不能出现在Escape Mode操作过程中。Stop状态会立即将Lane带回到Control模式。如果entry command和支持的命令不匹配,这个命令会被忽略,接收侧会等待发送侧返回到Stop状态。Stop状态周期只要要持续

在Escape Mode中,PHY使用Spaced-One-Hot位编码用于异步通信。因此此模式中Data Lane的操作不依赖Clock Lane。

Spaced-One-Hot编码里,每个Mark状态都插入了一个Space状态。因此每个符号包含了两部分:一个One-Hot部分(Mark-0或Mark-1)以及一个Space部分。对于bit-0(zero-bit),TX会发送Mark-0和一个Space;对于bit-1(“one-bit”),TX会发送Mark-1和一个Space。Mark之后没有跟Space的话,则并不能表示一个位。在退出Escape Mode前,最后阶段要是一个Mark-1,这个Mark-1并非是通信数据bits的一部分,因此它后面不跟一个Space状态。Clock是根据两条信号线Dp和Dn,通过异或的方式得到的。每个LP状态周期的长度至少为

Remote Triggers

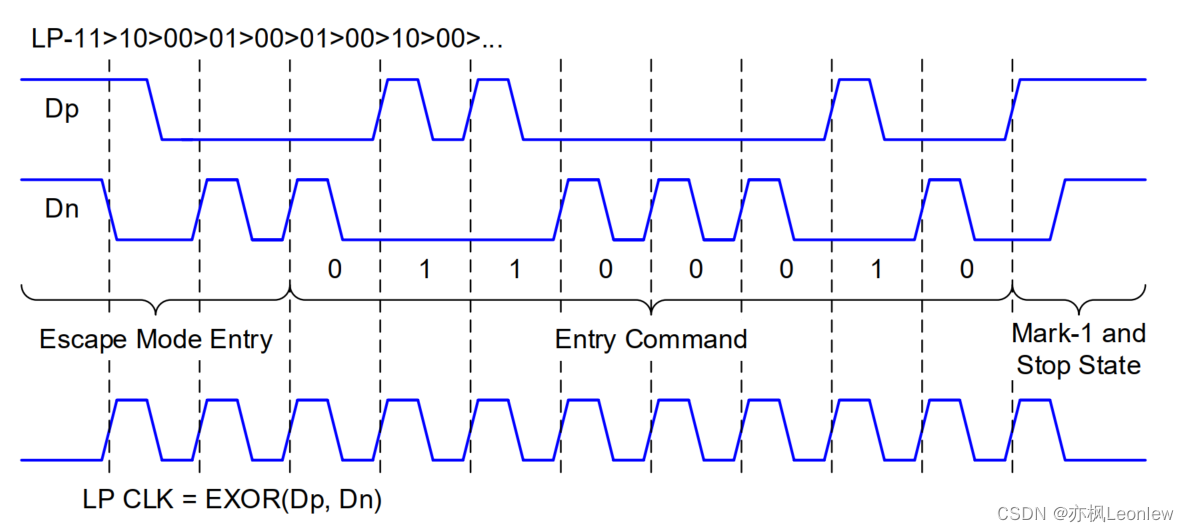

Trigger是一种用于发送标志(flag)到接收侧的协议层的机制,由发送侧的协议层发起请求。根据操作的方向以及可用的Escape Mode功能,trigger能够是Forward方向或Reverse方向中的一种。Trigger需要Escape Mode能力,并且在接口两侧要至少支持一个相互匹配的Trigger Escape Entry Command。下图是一个完整的Trigger-Reset命令的Escpe Mode action:

图2 Trigger-Reset Command in Escape Mode

Lane通过Escape Mode Entry过程进入到Escape Mode。如果Entry Command Pattern匹配上了Reset-Trigger命令,则接收侧会通过PPI向协议层触发一个Trigger。在Trigger命令之后但信号线进入Stop状态之前,任何接收到的位(bit)都要被忽略。因此,可以通过连接一些dummy字节来提为接收侧提供时钟信息。

需要注意的是,Trigger本身(包括Reset-Trigger)是一个通用的消息系统。Trigger命令不会对PHY自身的行为产生影响。因此,Trigger能够被协议层用于任何目的。

LPDT(Low-Power Data Transmission)

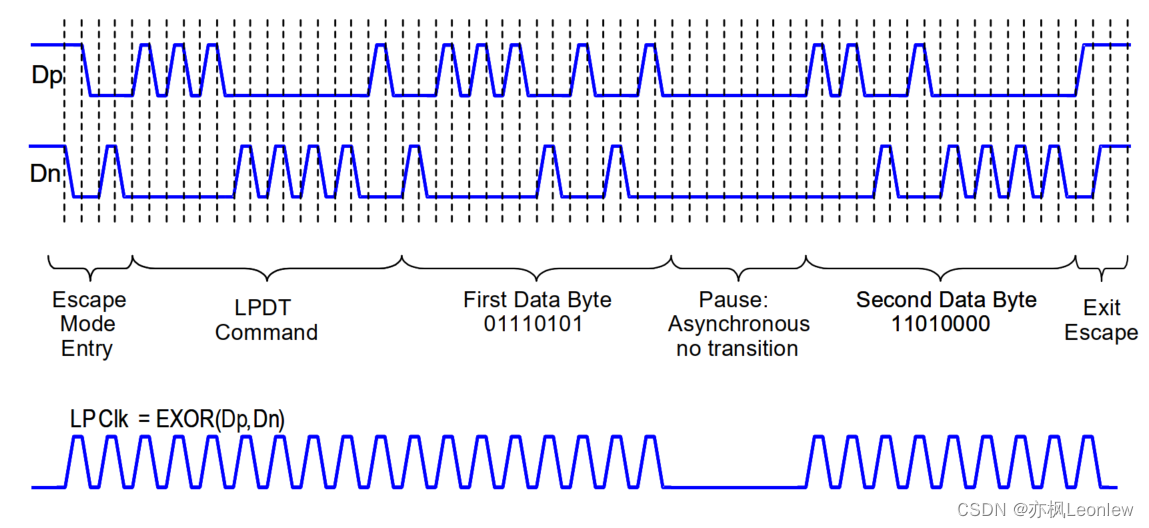

如果Escape Mode Entry过程之后,紧跟的Entry Command是LPDT,那么在Lane处于Low-Power模式时,数据能够按照协议以低速方式进行传输。

数据的编码仍然是Spaced-One-Hot编码,数据本身通过使用的bit信息编码,会自带时钟信息(self-clocked),并不依赖于Clock Lane。Lane能够在使用LPDT时暂停,这是通过在信号线上维持Space状态来实现的。信号线上的Stop状态会停止LPDT、退出Escape Mode、并且切换Lane到Control模式。在Stop状态之前的最后一个阶段是一个Mark-1状态(不表示一个数据位)。下图展示了一个暂停的例子,总共传输两个字节,这两个字节中间带一个暂停的周期:

图3 Two Data Byte Low-Power Data Transmission Example

LPDT发送数据使用了一个Low-Power(Bit)时钟信号(

ULPS(Untra-Low Power State)

如果在Escape Mode Entry命令之后,发送了ULPS命令,Lane会进入ULPS状态。这个命令要被通知到接收侧的协议层。处于ULPS的时候,信号线处于Space状态(LP-00)。ULPS状态的退出,通过一个长度为

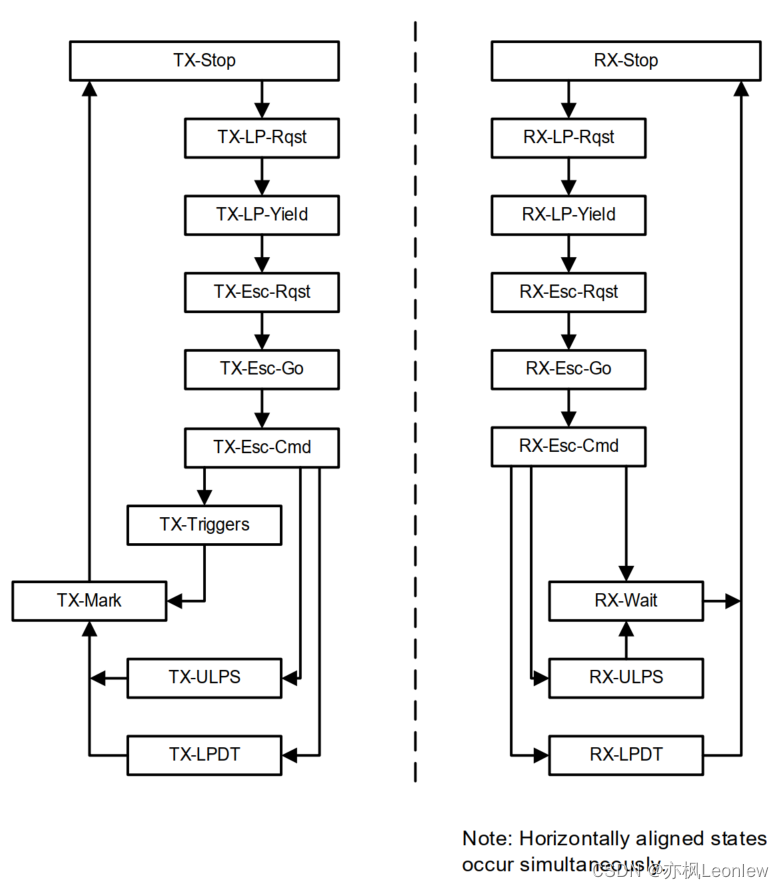

Escape Mode State Machine

图4 Escape Mode State Machine

图5 Escape Mode State Machine Description

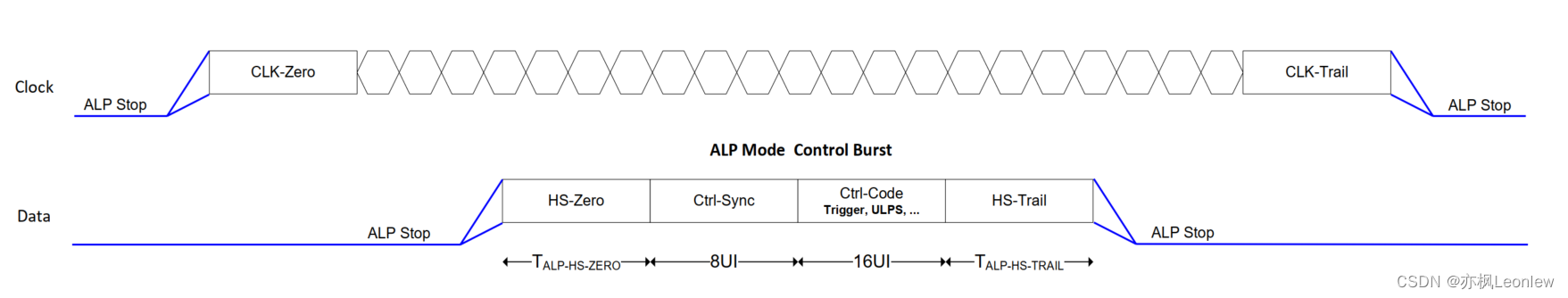

ALP模式中的Escape Mode等价功能

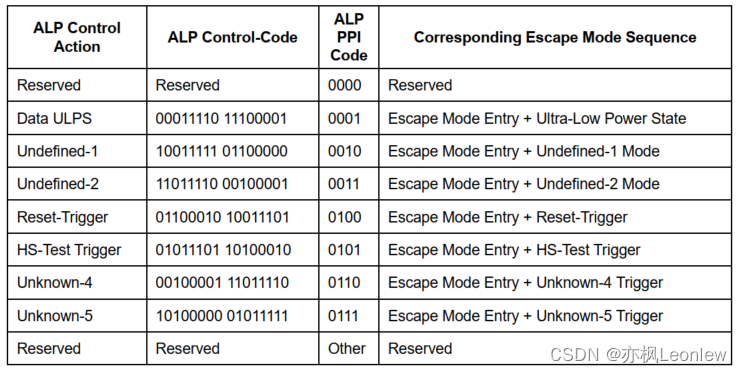

ALP Control-Codes支持和LP模式中Escape Mode一样的功能。但在ALP模式中,LPDT是唯一没有等价功能的地方。下表展示了ALP Control-Codes和LP Escape Sequences之间的映射关系:

图6 ALP Control-Code Definitions

这些ALP Control-Codes能在ALP Control Bursts中被用来给接收侧的协议层发出特殊功能的信号。

所有Control Bursts都在ALP Stop状态下开始和结束,除了Data ULPS Control Burst,在这个Burst结束后Lane会进入ALP ULPS状态,此时信号线处于ALP-00状态。通过一个长度为

要从ALP ULPS状态中唤醒一个Clock Lane,发送端要发送一个较长的ALP Wake脉冲,脉冲持续时间为

今天的文章mid pf_flippy固件分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/87518.html