由于项目需要,STM32F303跟STM32F405之间要用到DMA+SPI口来估大量数据传输,实现两边的数据收发。

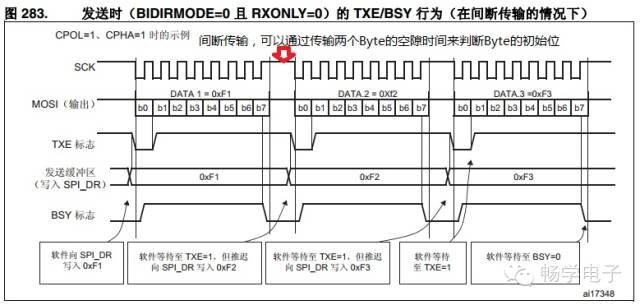

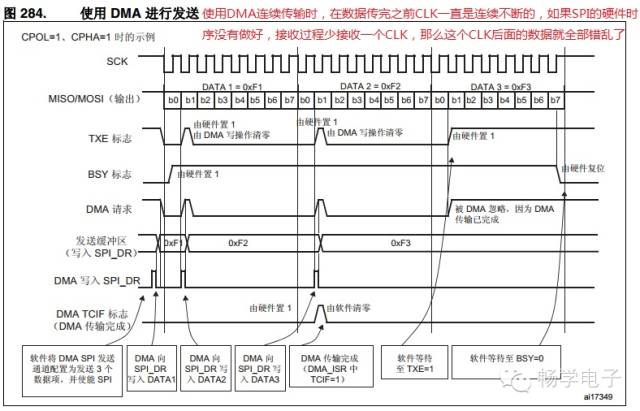

开始只用到MISO,MOSI,跟CLK三个信号,STM32F303配置成主机,18M的波特率,用DMA发4K的Buffer的数据,STM32F405这边用DMA循环接收SPI的数据,调试发现数据死活就是接收不对,完全是错乱的。改成不用DMA,直接SPI单个单个不停发送,接收数据却是正常的。用示波器看两个信号线的信号,信号也还好,用示波器的逻辑分析仪去分析SPI的通信,发现SPI的连续传输的时候,CLK是连续的,分析仪分析不到MISO上的数据或者分析出来的也是错误的。就猜想如果SPI的时钟在传输过程中是连续不间距的话,那么逻辑分析怎么可能知道SPI的MISO上1Byte的波形哪位才是初始位??STM32的SPI也是一样,硬件没法判断到,接收就错乱了。SPI通信中,如果时间每Byte的时钟不连续,就可以通过这时钟的间隙来判断。

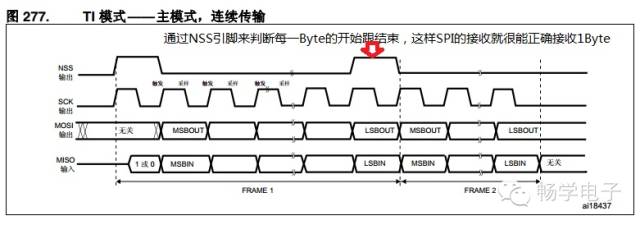

用专门的逻辑分析采齐SPI的数据来分析,数据对的,说明发送是正确的。就是接收错乱,让我更坚信前面的猜想,想要解决这个问题,最好就是增加同步,用一个同步线来告诉从机的SPI什么时候是一个Byte的开始,什么时候是结束。这里想到肯定是用NSS引脚来做,标准的SPI是不支持的,但是看到了TI Mode,这问题就解决了,也证实我的猜想。看下图TI Mode的时序

配置NSS引脚,405跟303把SPI配置修改为硬件NSS和TI Mode模式,再Debug就看到从机的接收Buffer上正常的数据。

前前后后折腾DMA+SPI有长的时间,网上都没有这样大量数据传输的应用,基本上都SPI的最简单应用,只要CLK不是连续的就不会出现这问题。按理来说如果STM32的SPI硬件时序做好了的话,也不会出现这问题,实际上它就是这里出问题了,我只能说STM32 的SPI也做得有点烂。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/bian-cheng-ji-chu/77223.html