系列文章目录

【集成电源开关拓扑系列一】

【集成电源开关拓扑系列二---负载开关】

文章目录

前言

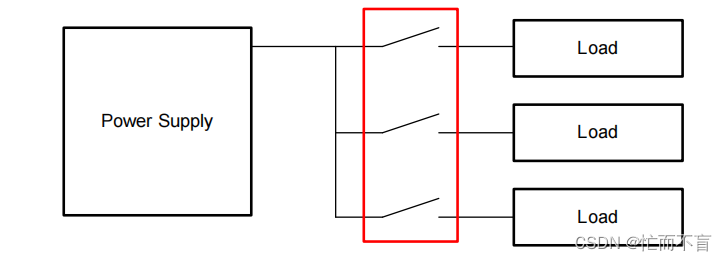

一、分立负载开关电路

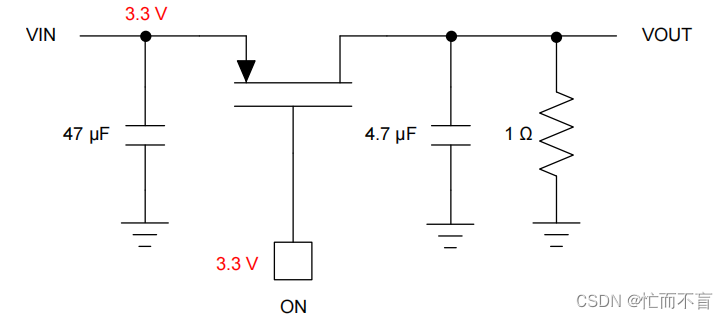

1.1 PMOS分立负载开关电路1

下图是一个非常简单的分立负载开关电路,只需要用到一个PMOS管和一个GPIO信号,GPIO连接到MOS管的栅极。当GPIO为高电平时,MOS管关闭。当GPIO为低电平的时候,MOS管打开。

这个电路最大的优点就是简单,那它的缺点是什么呢?

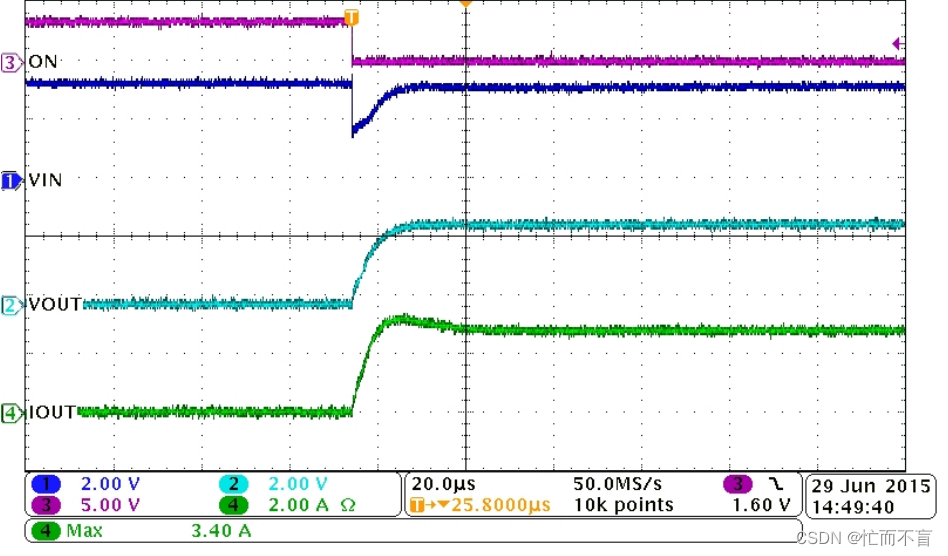

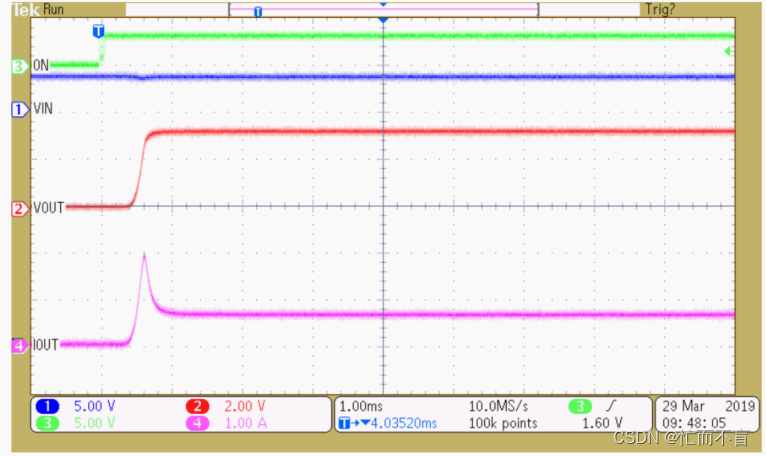

下面来看看上电过程中这个电路的实际表现 ,如下图:可以看到在开关打开过程中,输入电源出现了较大的跌落。

这是因为在开关打开瞬间,输出电容会导致较大的浪涌电流,从而导致输入电源瞬间跌落。上面的电路中,我们已经让输入电容取值是输出电容的10倍,如果输入电容更小,输出电源跌落会更大。

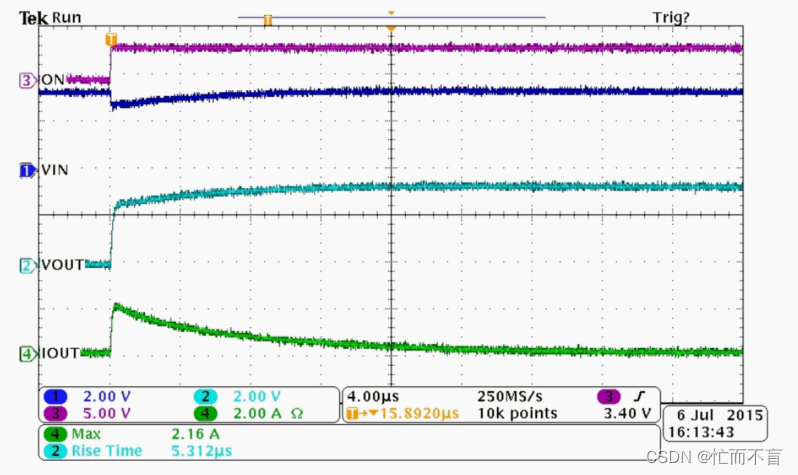

电源电压跌落只是不好的结果,根本点是浪涌电流。为了方便看出浪涌电流的大小,我们先将1Ω负载电阻去掉,然后观察到开关导通过程中的表现如下:

可以看出,仅4.7uF的电容,就会产生将近2A的浪涌电流。而浪涌电流大小是跟电容值成正比的。如果输出电容增大,浪涌电流可能会更大。(INRUSH =CLOAD*dV/ dt)

大的浪涌电流会导致输入电源电压下降、如果该输入电源还给其他模块供电,可能会导致其他模块因为低压导致复位。另外大的浪涌电流也可能导致芯片\连接器\PCB 等过流发热损坏。

另外用PMOS作为开关还有一个缺点,输入电压最大值有限制,如下图,Vgate-VIN要小于VGS(th),比如VGS(th)min=-1V,Vgate=3.3V ,则VIN 不能超过4.3V,否则MOS将会一直打开,无法关闭。

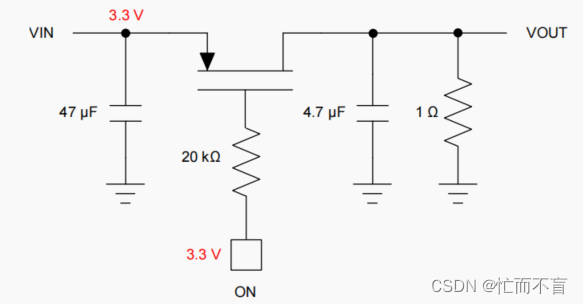

上述电路可以在MOS管栅极串联一个电阻来降低浪涌电流,如下图:

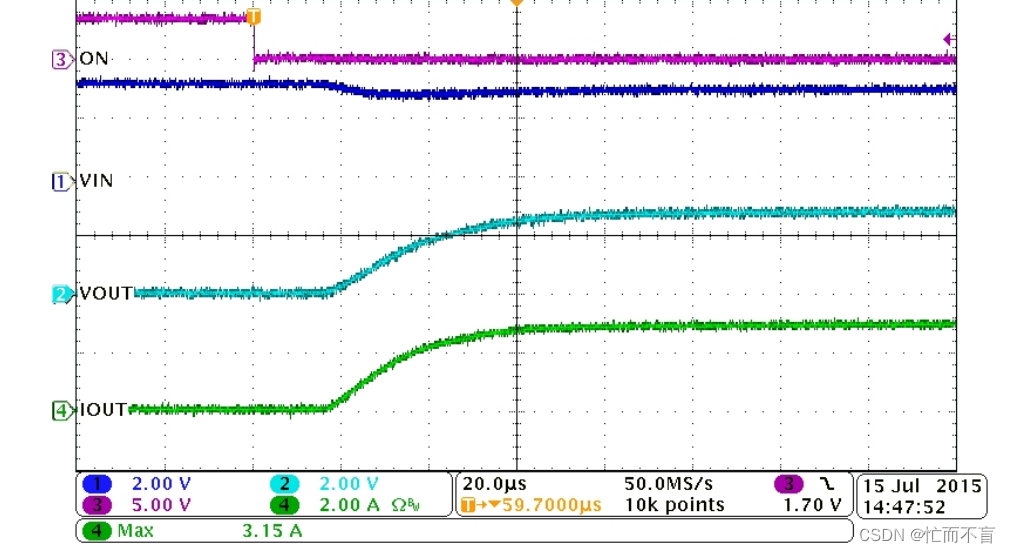

串联电阻与GS之间的电容组成RC电路,可以MOS管的开关时间变长,从而使输出电压上升速度变慢,根据IINRUSH =CLOAD*dV/ dt,dt增大,IINRUSH会减小。实际测试结果如下:

可以看出,加了20k串阻后,电压跌落很小。在PMOS的栅极上增加串阻有助于增加输出的上升时间,同时也增加了PMOS关闭时的下降时间。对于需要快速释放输出负载以加快系统运行的系统来说,这可能是一个缺点。

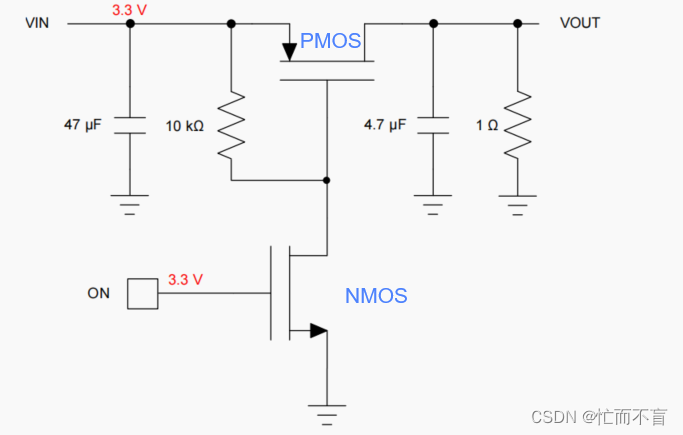

1.2 PMOS分立负载开关电路2

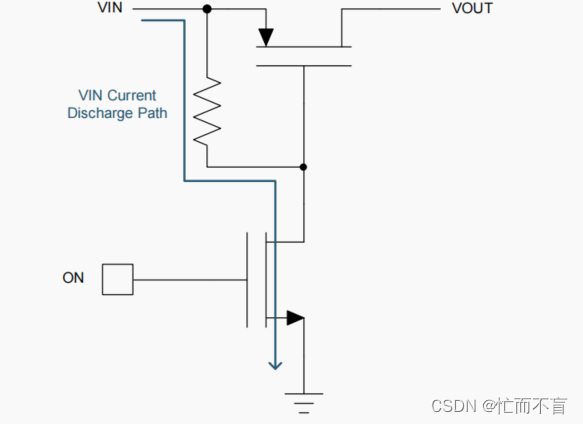

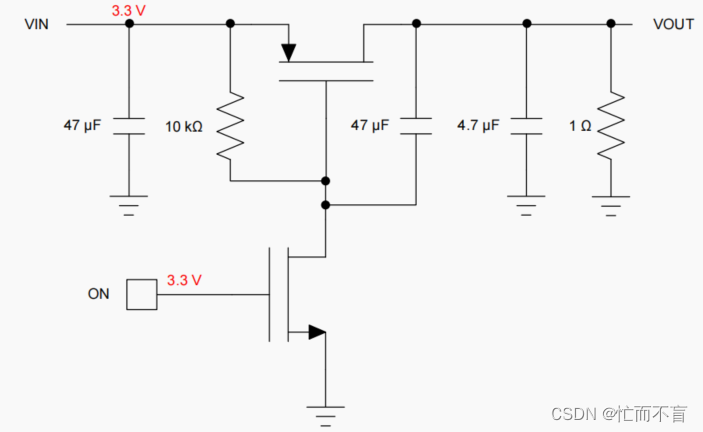

在上面分立电路的基础上增加一个NMOS(也可以是一个三极管)和一个电阻,构成第二种分立负载开关电路,如下图所示:当GPIO输出高电平到ON管脚,NMOS导通,PMOS的栅极为低电平,从而使得PMOS导通,电源从VIN流到VOUT。

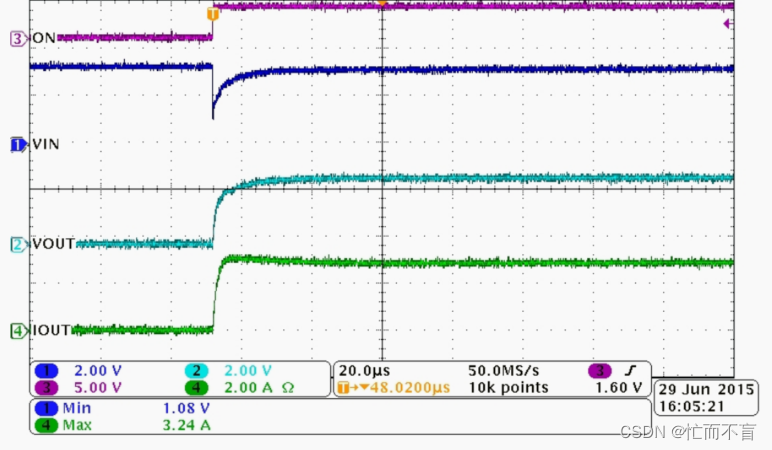

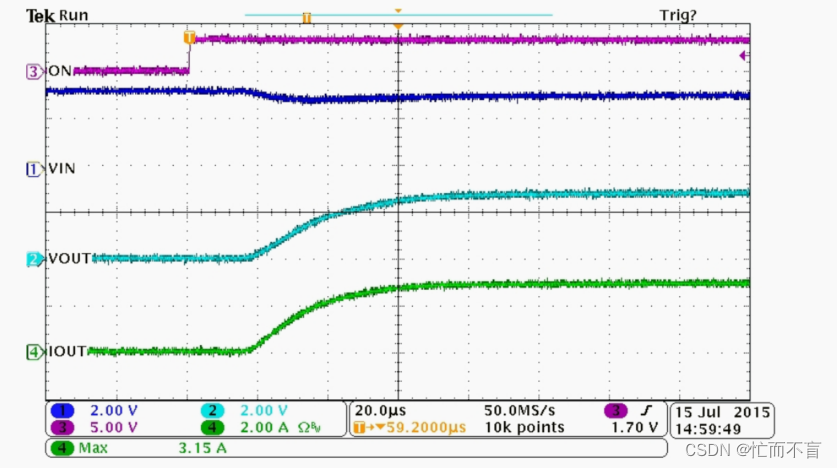

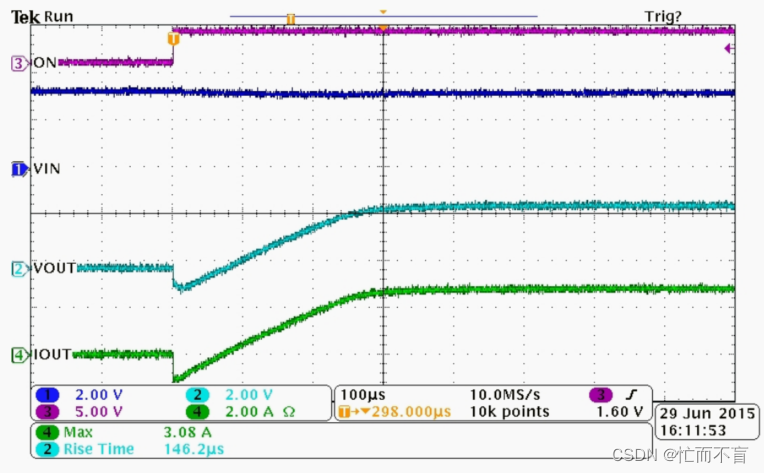

同理,通过分析电路的开关特性来评估该电路的性能。上面电路在PMOS打开过程如下:

可以看到,输入电源的跌落持续时间变短了(输出电压的上升时间更长了),跌落的幅度几乎没有变化。

同理,去掉负载电阻1Ω,观察最大的浪涌电流,还是2A左右。

不过这个电路还是解决了上个电路的一个问题,VINmax的限制。

这个电路多了一个缺点,当开关导通的时候,会有一个漏电路径,如下图所示,导致工作时功耗增加,

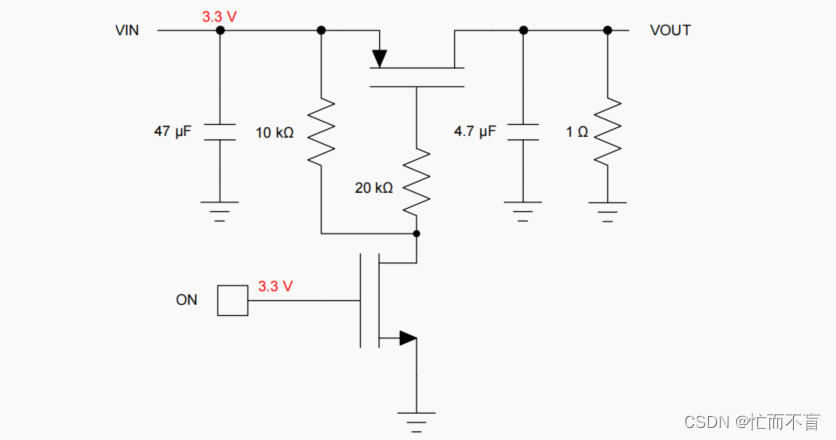

同理,该电路也可以在PMOS的栅极串联一个电阻,用来降低浪涌电流,如下图:

串联电阻后的表现如下:

1.3 PMOS分立负载开关电路3

在分立负载开关电路2的基础上,还可以在PMOS的栅极与漏极之间并联一个电容,减缓栅极电压变化速度,从而减缓VOUT的上升速度,降低浪涌电流。如下图所示:

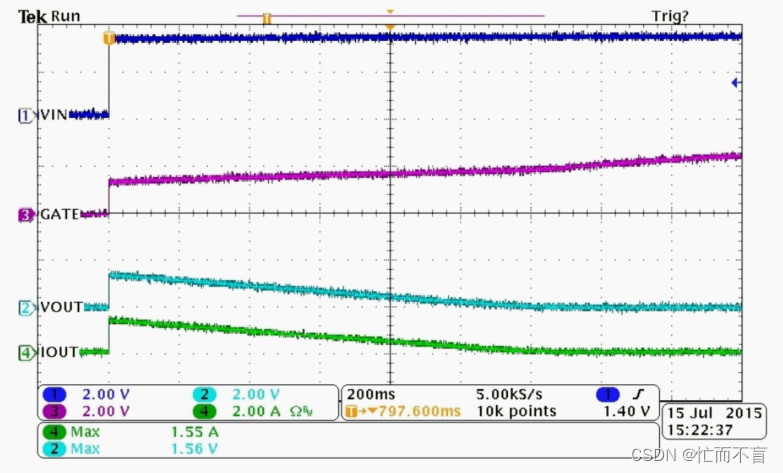

其开通过程中特性曲线如下:

可以看出,与第1、2个分立负载电路相比,输入电压没有明显跌落。但是有另外一个问题,就是输出电压和电流出现短暂负值。当VIN应用于电路且ON为低电平时,PMOS的栅极和漏极之间的电容器被充电到VIN值。当ON为高电平,PMOS的栅极从VIN拉到地。由于电容器两端的电压不能瞬间改变,PMOS输出VOUT上的电压也被拉低,这导致VOUT上出现负电压。一旦PMOS的栅极放电完成,输出电压就能够上升到VIN的值。

负电压不仅会损坏负载开关下游的设备,还会导致系统中部件的栓锁和ESD问题。

与电路#2一样,该电路也具有从VIN到地面的放电路径,当PMOS打开时,导致电流从VIN泄漏。

该电路还有一个独特的缺点,当VIN首次上电时,即使此时ON为低电平,NMOS关处于关闭状态。PMOS 栅极与漏极之间的大电容会导致栅极的电压上升较慢,从而导致PMOS误导通。如下图:这将导致大的浪涌电流和输出电压,这可能会无打开负载,并对电源造成压力。这种情况在使用可更换电池的系统中尤其普遍,因为加入一个新电池会导致VIN很快从0V转到电池电压。

1. 4 PMOS分立负载开关电路4

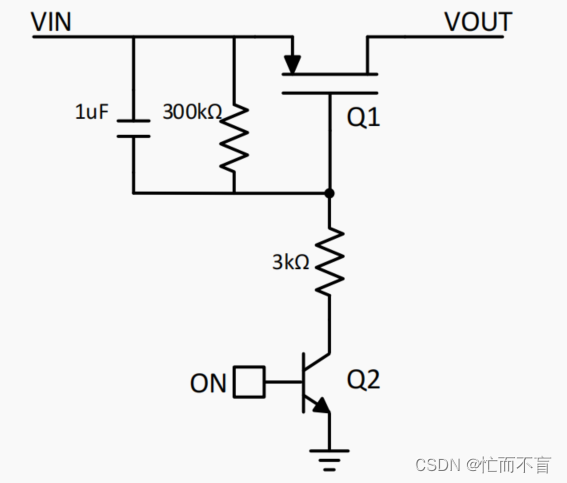

实际应用路中,使用的分立开关电路 如下图,将电阻、电容并联在PMOS的栅极与源极之间,产生一个RC延迟,从而减少涌入电流和减慢PMOS的开关速度。另外从PMOS的栅极串联电阻,也可以以减缓输出上升时间。

其开通特性如下图,输入电压基本不会跌落,浪涌电流持续时间也较短。相对与集成负载开关,浪涌电流是非线性变化的,不是可控的。

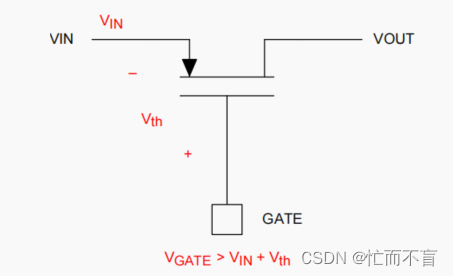

1.5 NMOS分立负载开关电路

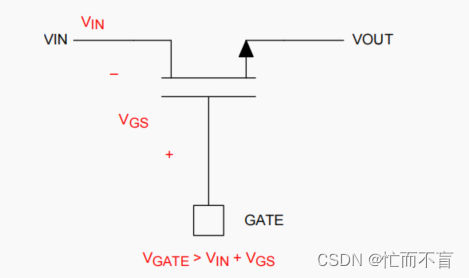

下图是一个简单的NMOS负载开关电路,该电路对输入电压VIN的最大值有限制,VIN需要小于Vgate-VGS 。

为了解决VIN限制问题,可以在上述电路基础上,增加一个电荷泵电路,使用电荷泵,可以实现NMOS的高VGS,并且使驱动电路的导通电阻降低。当然与PMOS一样,也会存在浪涌电流问题。如果需要减少浪涌电流,也还需要增加其他一些分立器件。

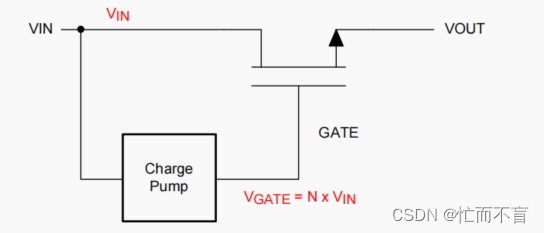

二、集成负载开关介绍

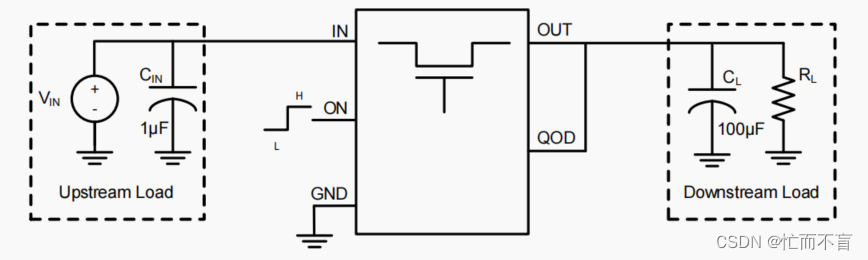

2.1 集成负载开关框图

2.2 集成负载开关datasheet中的参数

2.3 集成负载开关的导通特性

控制的上升时间确保了较低的浪涌电流和输入电压下降,且不需要使用任何外部组件。

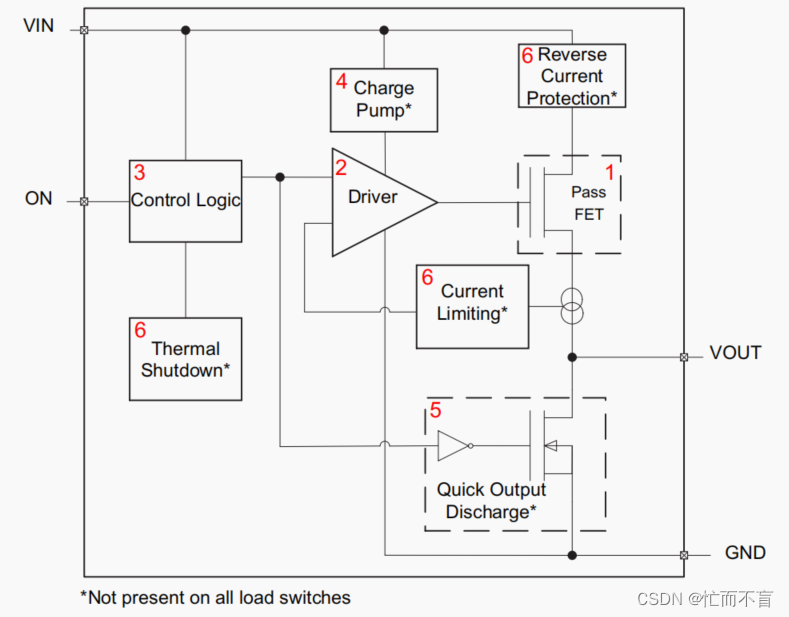

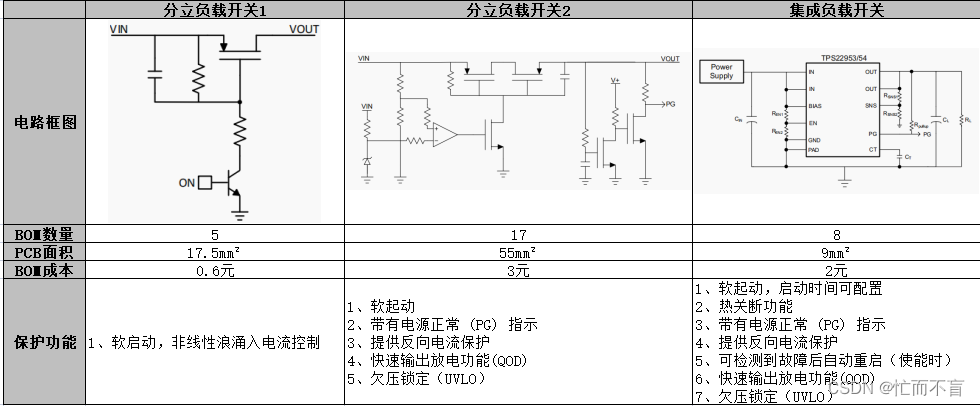

三、分立负载开关与集成负载开关对比

如下图所示,分立负载开关电路1 简单、价格相低。但是占用PCB面积较大、且基本没有保护功能。集成负载开关在占用PCB面积小、具有强大的保护功能,价格稍贵。如果用分立器件要实现接近同样的保护功能,成本、PCB面积都要高很多。

因此,如果系统对保护功能没有过高要求,可以使用简单的分立负载开关1,否则建议选用集成负载开关。

四、集成负载开关选型与设计注意事项

4.1 NMOS 与 PMOS

在 NMOS 器件中,通过使栅极电压高于源极电压来使导通 FET 接通。 通常,源极电压与 VIN 端子处于相同电势。 要使栅极和源极间产生上述电压差,需要一个电荷泵。 使用电荷泵将增大器件的静态电流。

在 PMOS 器件中,通过使栅极电压低于源极电压来使导通 FET 接通。 PMOS 器件的架构无需电荷泵,因此其静态电流比 NMOS 器件的静态电流低。基于 PMOS 的架构与基于 NMOS 的架构的一个主要差别是,基于 PMOS 的负载开关在低电压下性能欠佳,因为低压下VGS低,导通电阻RDSON大。而 NMOS 器件在低输入电压应用中性能良好。

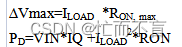

4.2 导通状态电阻 (RON)

导通状态电阻 (RON) 是一个极为重要的参数,因为它决定了负载开关的压降和功耗。 RON 越大,负载开关的压降越大,功耗越高。

其中,

∆Vmax = VIN 到 VOUT 的最大压降

ILOAD = 负载电流

RON, max = 给定 VIN 对应的器件最大导通电阻

IQ = 负载开关的静态电流

4.3 电压 (VIN) 和电流 (IMAX) 额定值

决定使用哪种负载开关时的重要考虑因素之一是应用所需的电压和电流。 负载开关必须能够支持稳态工作期间所需的直流电压和电流,以及瞬变电压和峰值电流。 需要注意的是,一些负载开关需要偏置电压来开启器件和偏置内部电路。 此偏置电压与输入电压无关。

4.4 关断电流 (ISD) 和静态电流 (IQ)

静态电流是负载开关接通时消耗的电流。 除 I2R 损耗外,静态电流还将决定负载开关接通时的功耗量。 如果负载电流足够大,则静态电流引起的功耗可忽略不计。

关断电流决定了负载开关通过 ON 引脚被禁用时的功耗量。 使用负载开关切断子系统电源可显著降低电源轨的待机功耗。

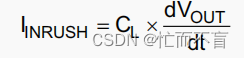

4.5 上升时间 (tR)

上升时间因器件而异。 上升时间可能需要较短,也可能较长,具体取决于应用。 此外,浪涌电流与上升时间成反比。 了解系统所能接受的浪涌电流是十分有益的。

其中

INRUSH = CL 产生的浪涌电流的大小

CL = VOUT 上的总电容

dVOUT = 启用器件时 VOUT 的电压变化

dt = VOUT 电压变化 dVOUT 所用的时间

4.6 快速输出放电 (QOD)

一些负载开关具有内部电阻,该电阻会在开关关断时将输出拉至地,以避免输出浮空。 要使快速输出放电功能起作用,输入电压引脚上的电压需处于工作范围内。

快速输出放电功能有诸多好处,例如:

• 输出不会浮空并且始终处于已确定状态。

• 下游模块始终完全关闭。

不过,仍有应用无法从快速输出放电功能中受益。

• 如果负载开关的输出与电池相连,则通过 ON 引脚禁用负载开关时,快速输出放电会导致电池电量耗尽。

• 如果两个负载开关用作双输入单输出多路复用器(其中,二者输出连在一起),则负载开关无法提供快速输出放电功能。 否则,快速输出放电期间将持续浪费电能,因为只要通过 ON 引脚禁用负载开关,电流就会通过内部电阻流向地。

4.7 封装尺寸

集成负载开关提供各种不同的形状和尺寸。 确保应用能够接受负载开关是十分重要的。 在空间受限的系统中,可能需要选择较小的封装尺寸。 例如,可能不需要使用 0.4mm 间距的器件,所以选择部件时不应考虑0.4mm 间距的器件。 因此,选择器件时应考虑封装尺寸。

4.8 输入和输出电容

4.9 散热注意事项

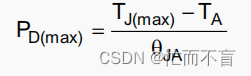

最大 IC 结温应限制为绝对最大值表中指示的正常工作条件下的最大结温。 要计算在给定的输出电流和环境温度下的最大允许功耗 PD(max),请使用公式:

其中:

PD(max) = 最大允许功耗

TJ(max) = 最大允许结温

TA = 器件的环境温度

θJA = 结点到空气热阻 此参数很大程度上取决于电路板布局。

五、总结

参考文档:

1、Basics of Load Switches--TI

2、Integrated Load Switches Versus Discrete MOSFETs--TI

3、Selecting a Load Switch to Replace a Discrete Solution--TI

今天的文章 【集成电源开关拓扑系列二---负载开关】分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/bian-cheng-ji-chu/86248.html