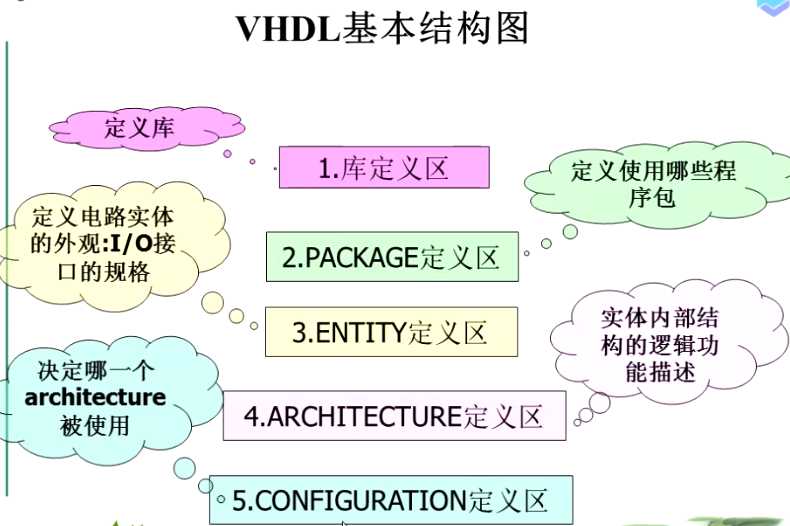

VHDL语言的基本结构

一、VHDL设计简述

VHDL主要用于描述数字系统的结构、行为、功能和接口。

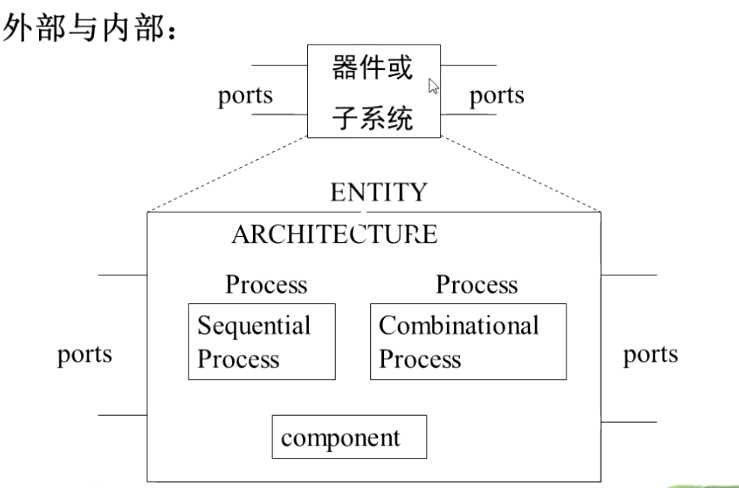

VHDL将一个设计(元件、电路、系统)分为:

外部(可视部分、端口)

内部(不可视部分、内部功能、算法)

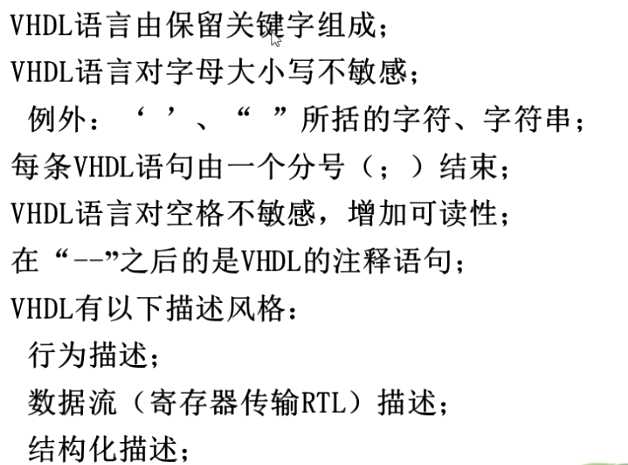

1.VHDL语言的一些基本特点

二、实体

1.功能

描述设计模块的输入/输出信号或引脚,并给出设计模块与外界的接口。实体类似一个“黑盒”,实体描述了“黑盒”的输入输出口。

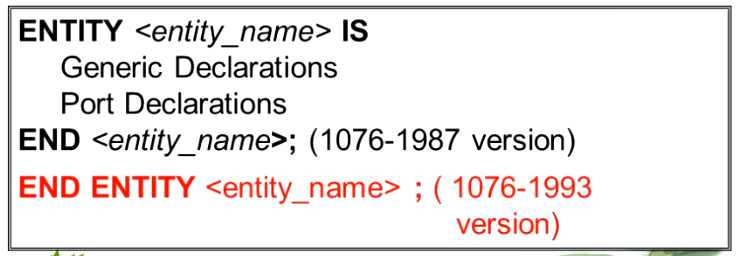

2.格式

3.实体名

实体名实际上是器件名,最好根据相应的电路功能确定。如4位2进制计数器用counter4b; 8位加法器用add8b; 3/8译码 器用ym_ 38。

实体名必须与文件名相同,否则无法编译。

实体名不能用工具库中定义好的元件名。

实体名不能用中文,也不能用数字开头。

4.类属说明

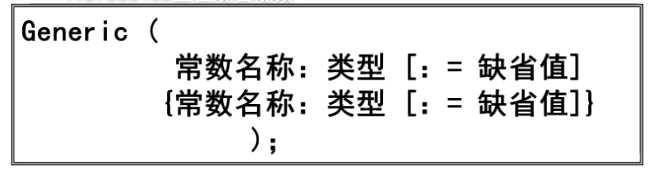

确定实体或组件中定义的局部常数。模块化设计时多用于不同层次模块之间信息的传递。可从外部改变内部电路结构和规模。类属说明必须放在端口说明之前。

类属参数是一种端口界面常数,用来规定实体端口的大小、

总线宽度设计实体的物理特性等与常数不同,常数只能从内部赋值而类属参量可以由实体外部赋值数据类型通常取Integer或Time;

综合器仅支持数据类型为整数的类属值。

5.端口声明

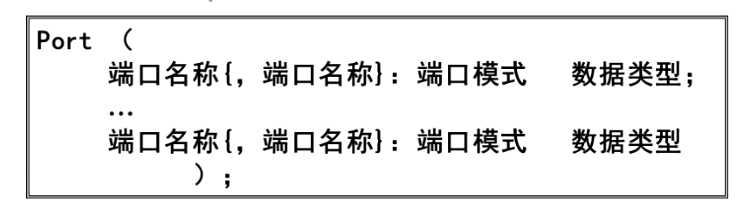

端口(PORT)是实体的一部分,PORT类似于器件的管脚,主要用于信号的传输,PORT一般有Name, Mode,和Type

端口说明格式:

端口模式:

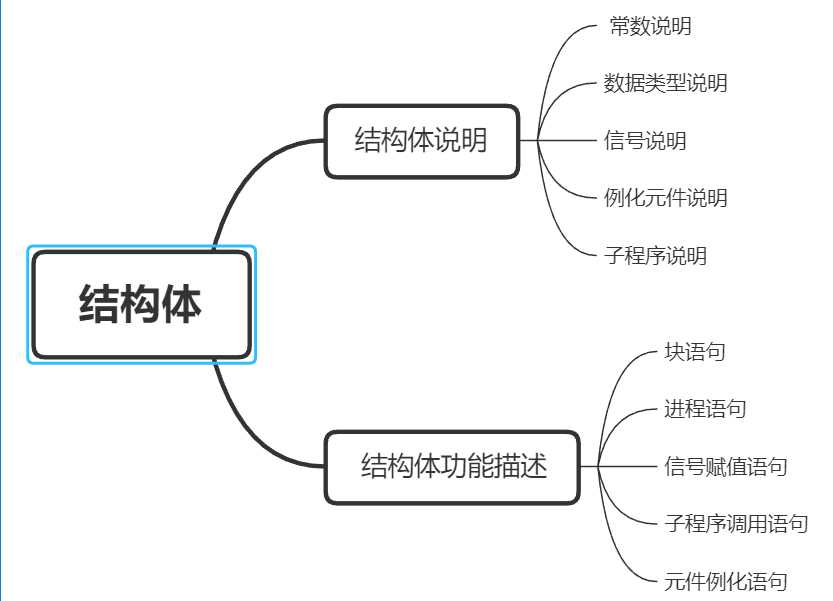

三、结构体

用来描述实体的内部结构和逻辑功能,必须和实体(ENTITY) 相联系,一个实体 (ENTITY) 可以有多个结构体,结构体的运行是并发的,结构体描述方式包括:行为描述、结构描述、数据流描述

1.结构体组成

两个组成部分:

(1)对数据类型、常数、信号、子程序、元件等元素的说明部分。

(2)以各种不同的描述风格描述的系统的逻辑功能实现的部分。

一个设计实体可有多个结构体,代表实体的多种实现方式。各个结构体的地位相同。

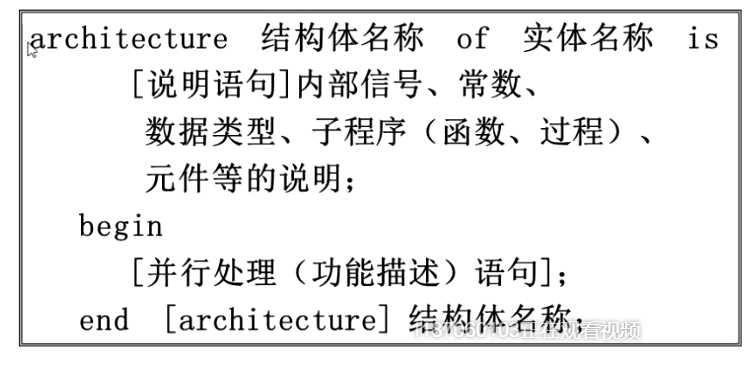

2.结构体的语法结构

同一实体的结构体不能同名。定义语句中的常数、信号不能与实体中的端口同名。

四、库

1.库的分类

VHDL库可分为5种

(1)IEEE库

定义了四个常用的程序包

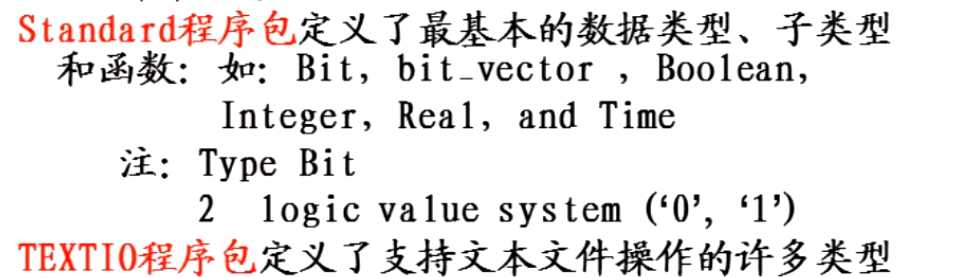

(2)STD库(默认库)

库中程序包为: s tandard, TEXTI0

(3)面向ASIC的库

(4)WORK库(默认库)

(5)用户自定义库

2.库的使用

库及程序包的说明总是放在实体单元前面,默认库(如STD, WORK库)可不作说明。用关健字library说明要使用的库。

LIBRARY 库名;

库及程序包的作用范围:仅限于所说明的设计实体。

每一个设计实体都必须有自已完整的库及程序包说明语句。

程序包:

已定义的常数、数据类型、元件调用说明、子程序的一个集合,方便公共信息、资源的访问和共享,多个程序包构成库。

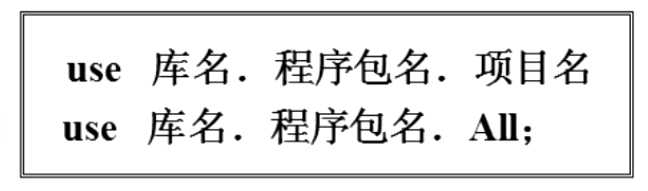

程序包的使用格式:

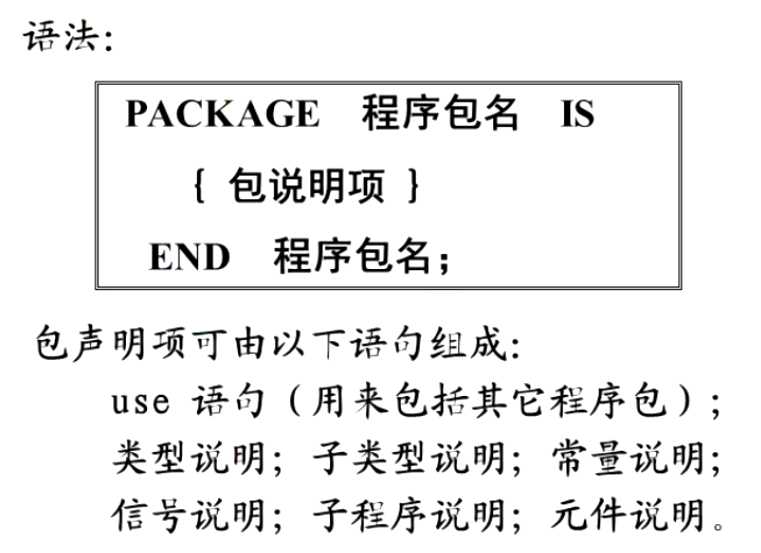

程序包的结构包括:

程序包说明(包首)

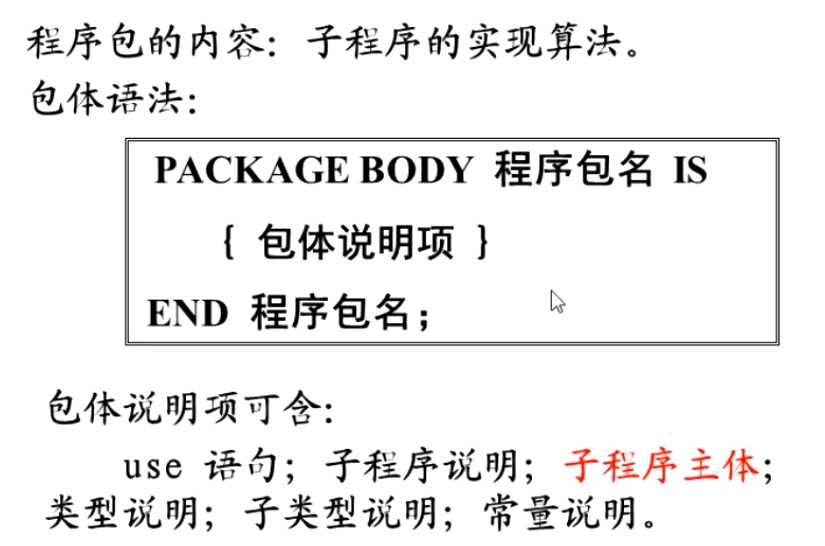

程序包主体(包体)

程序包说明的内容:

常量说明;

VHDL数据类型说明;

元件说明;

子程序说明;

(1)程序包说明

(2)程序包包体

(3)程序包首与程序包体的关系

程序包体并非必须,只有在程序包中要说明子程序时,程序包体才是必须的,程序包首可以独立定,义和使用。

五、配置

一个设计实体对应多个结构体,有多种实现方式。

配置:从某个实体的多种结构体描述方式中选择

特定的一个。

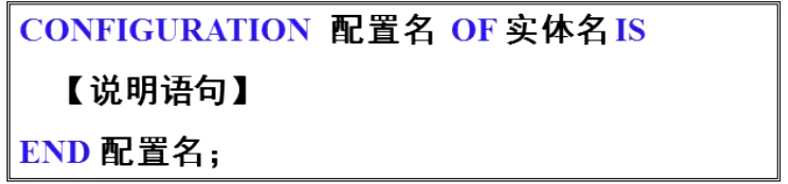

1.配置语句的基本格式

(1)默认配置格式结构(用于选择不包含元件或块的结构体)

今天的文章第三章 VHDL语言的基本结构分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:http://bianchenghao.cn/24969.html