有限状态自动机是拥有有限数量的状态,并且每个状态可以变换其他状态的数学模型。

A finite-state machine (FSM) or finite-state automaton (FSA, plural: automata), finite automaton, or simply a state machine, is a mathematical model of computation. It is an abstract machine that can be in exactly one of a finite number of states at any given time. The FSM can change from one state to another in response to some inputs; the change from one state to another is called a transition. An FSM is defined by a list of its states, its initial state, and the inputs that trigger each transition. Finite-state machines are of two types—deterministic finite-state machines and non-deterministic finite-state machines. A deterministic finite-state machine can be constructed equivalent to any non-deterministic one.

Mealy FSM(米利型有限状态机)

在Mealy机器中,输出取决于当前状态和当前输入。

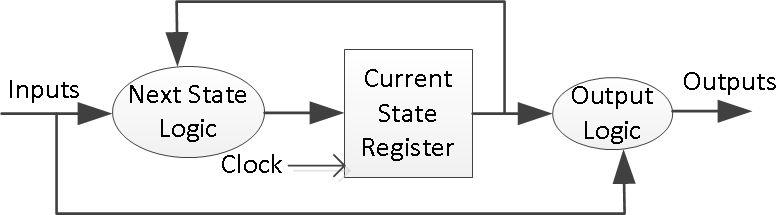

三段式Mealy机器的图示及其建模如下:

module mealy_3processes(input clk, input reset, input x, output reg parity); reg state, nextstate; parameter S0=0, S1=1; always @(posedge clk or posedge reset) // always block to update state if (reset) state <= S0; else state <= nextstate; always @(state or x) // always block to compute output begin parity = 1'b0; case(state) S0: if(x) parity = 1; S1: if(!x) parity = 1; endcase end always @(state or x) // always block to compute nextstate begin nextstate = S0; case(state) S0: if(x) nextstate = S1; S1: if(!x) nextstate = S1; endcase end

endmodule

Moore FSM(摩尔型有限状态机)

在Moore机器中,输出仅取决于当前状态。

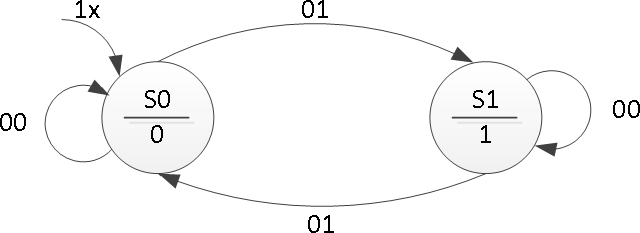

以下是使用Moore型有限状态机实现的奇偶校验器的状态图。与之关联模型如下所示。

module moore_3processes(input clk, input reset, input x, output reg parity); reg state, nextstate; parameter S0=0, S1=1; always @(posedge clk or posedge reset) // always block to update state if (reset) state <= S0; else state <= nextstate; always @(state) // always block to compute output begin case(state) S0: parity = 0; S1: parity = 1; endcase end always @(state or x) // always block to compute nextstate begin nextstate = S0; case(state) S0: if(x) nextstate = S1; S1: if(!x) nextstate = S1; endcase end endmodule

今天的文章有限状态自动机能识别_半自动机分享到此就结束了,感谢您的阅读,如果确实帮到您,您可以动动手指转发给其他人。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/54292.html