一、代数环的问题

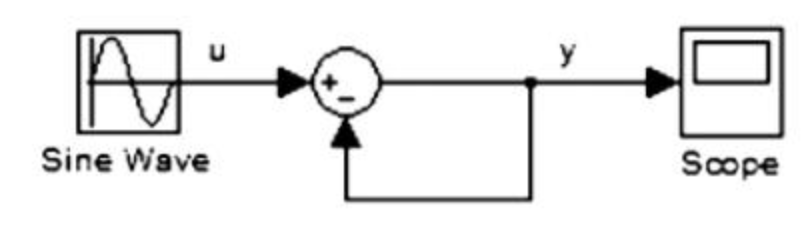

在数字计算中,输入信号决定输出信号,同时输出信号也决定输入信号,由于数字计算的时序性,导致没有输出信号无法计算输入信号,没有输入信号又反过来无法计算输出信号,形成一个死锁(deadlock)或死循环,这就是代数环。如下图1所示,就是一个简单的代数环的例子。

图1、一个简单的代数环的例子

二、代数环产生的条件

简单地说,代数环其实就是一个输入信号包含输出信号,同时输出信号也包含输入信号的特殊反馈回路。在simulink中,这是由于直通模块(无延时的模块)的原因造成的,simulink中大部分的模块都是直通模块,因此很容易形成代数环。在整个回路中,只包含直通模块就会形成代数环,反馈回路有延时模块就会消除代数环。

三、代数环的解决措施

1、用工具栏中的“simulink”中的“diagnostics”对代数环进行消除

将simulink中diagnostics的对代数环的处理信息进行选择,将对代数环的处理信息选择为“none”,即忽略代数环的信息。

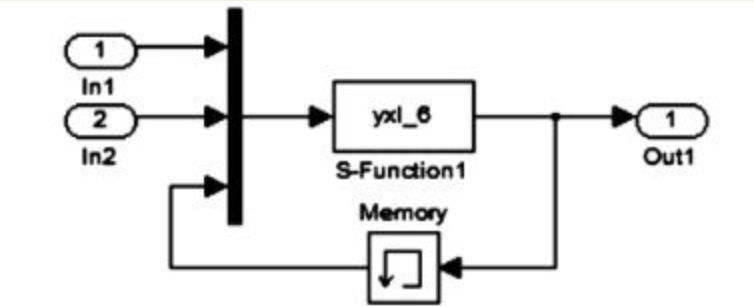

2、在反馈回路中添加延时模块进行消除

由于代数环的产生是由于整个模型中所有模块均为直通模块,因此只需在反馈回路中添加延时模块即可消除代数环。延时模块有delay模块、memory模块,如图2所示,用memory来消除代数环。

图2、用memory模块来消除代数环的例子

3、用变换法消除代数环

对于简单的代数环问题,可以通过人为地采用数字变换法来求解消除代数环,但这只针对简单的代数环有限,对于复杂的代数环基本不可能实现。

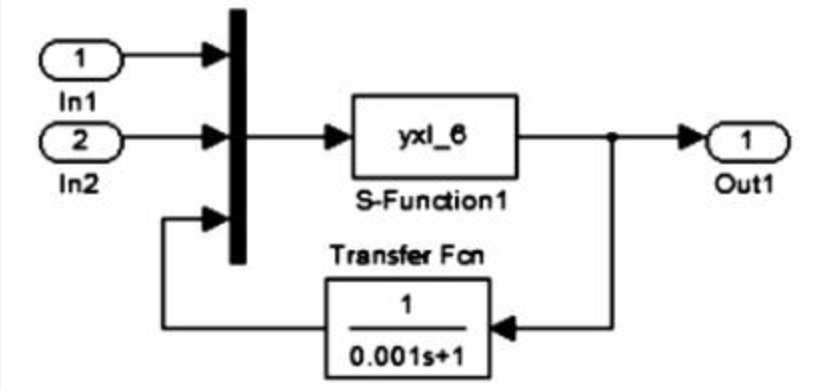

4、在反馈回路中添加入高频传递环节

在反馈回路中添加入高频传递函数,打断反馈回路中的直通模块,消除输入信号与输出信号的关联关系。如图3所示。

图3、在反馈回路中添加入高频传递环境来消除代数环的例子

5、重构部分模型

对形成代数环中的某些模块进行重构,以此来消除代数环。

今天的文章matlab/simulink中代数环的问题及解决措施分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/65595.html