尊重劳动成果,转载

请注明出处!!!

请注明出处!!!

请注明出处!!!

相关文章:

存储器相关概念

存储扩展(一):字扩展

存储扩展(二):位扩展(从位扩展到奇偶分体)

存储扩展(三):总结

存储容量位扩展

介绍与问题分析

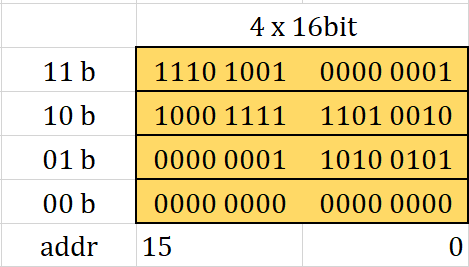

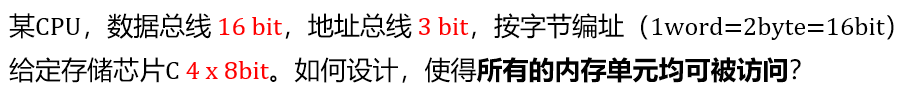

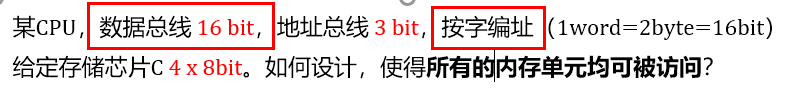

什么是存储容量位扩展?看如下问题:

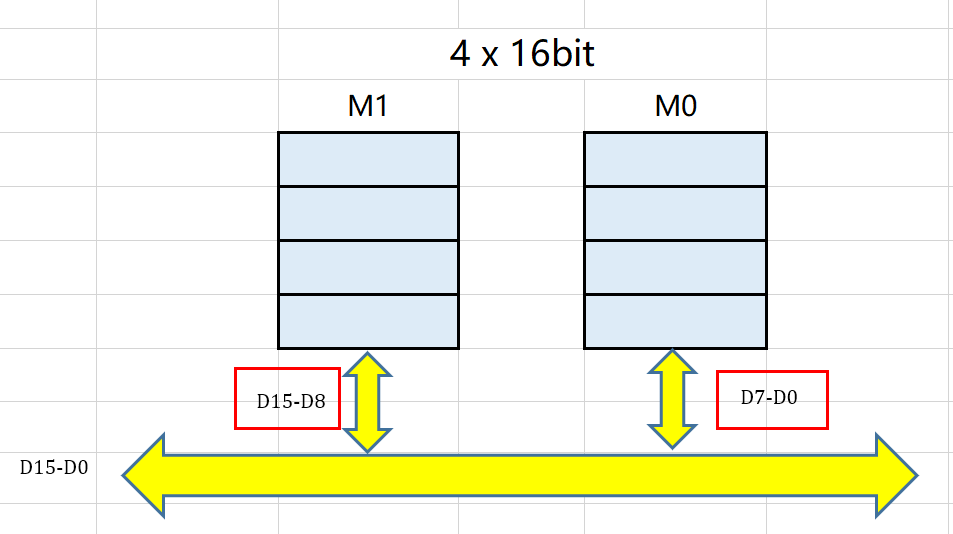

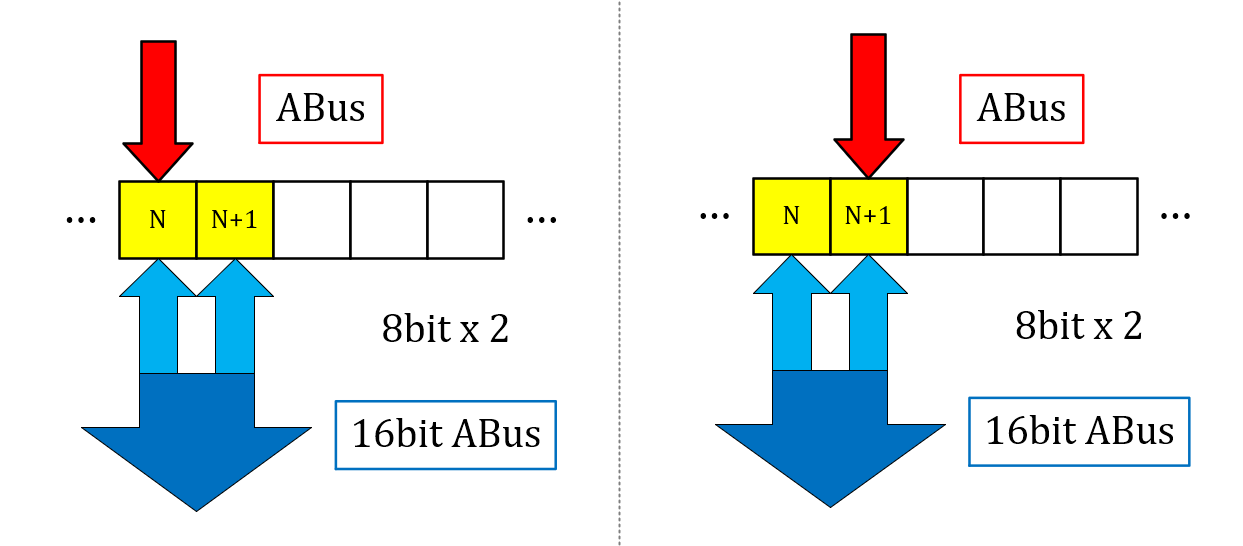

但是给定的C在它的一个工作周期内只能访问8bit,很自然的我们可以想到,用两片C,分别占用DBus的高八位与低八位,地址同时传给两片C,并且两片C同时被选中,那么两片C中的数据几乎也同时读出到DBus上的高低字节(即便是相同一片,不同地址读出时间有差异。不同片的同地址读出时间也有差异)。

(只有一片C有没有办法?有,并行转串行,将片内两个不同地址的数据组成一个字,相应的存储单元元数减半,数据寄存器MBR增加一个,地址寄存器MAR减少一位,另外考虑到时序问题,读出的两个字节的保持时间段要一致以便传送至总线,第一个字节要保持的时间更久,或者总线/CPU分时分高低字节接受数据,这就增加了C的外围电路的设计复杂度,这种设计思路与并行访问存储器的设计是很相似的,见《计算机系统结构》)

将多个芯片组成一个整体,使数据位数增加以满足CPU存储接口的数据吞吐率的要求(这里体现为数据总线的宽度),提高访问内存的速度,同时存储单元数不变,这就叫位扩展。显然易见,这种扩展方式扩容的同时也提升了速度。

数据总线连接

地址总线连接与片选信号选择

ABus 3bit,但是位扩展后的整体对外只有四个单元,占两位,还有多的一位。 地址怎么分配?8个地址,只有4个存储单元,那么可以只占用4个地址,也可以8个地址全都使用。

只占用4个地址:

与上一篇一样,假设ABus上的地址 xyz b,选两个作为地址,剩下一根。取一种情况片内地址 yz b, 剩下x,x=0与x=1均对应4个不同的地址,那么只取一种情况即可使用四个地址。如果使用x=0,且片选信号/CS低电平有效,那么可以直接将A2作为片选信号,这样000 001 010 011就对应了四个存储单元。其他的情况类似,地址分布不同。

(001 011 101 111对应四个奇存储单元,000 010 100 110对应四个偶单元,且这几个刚好组成全部的8个地址)

https://blog.csdn.net/_

8个地址都用:

怎么用?地址与存储单元的关系可以是一对一,也可以是多对一,但是不能一对多。多个地址对应一个存储单元又称为地址重叠现象。我们将A3浮空,片选始终有效,那么000与100对应同一个存储单元,这是被允许的,尤其是单片机低内存的情况。其他情况000 001对应一个存储单元,这是非常具有风险的。具体情况具体分析。

总线宽度与编址单元大小不一致怎么办?

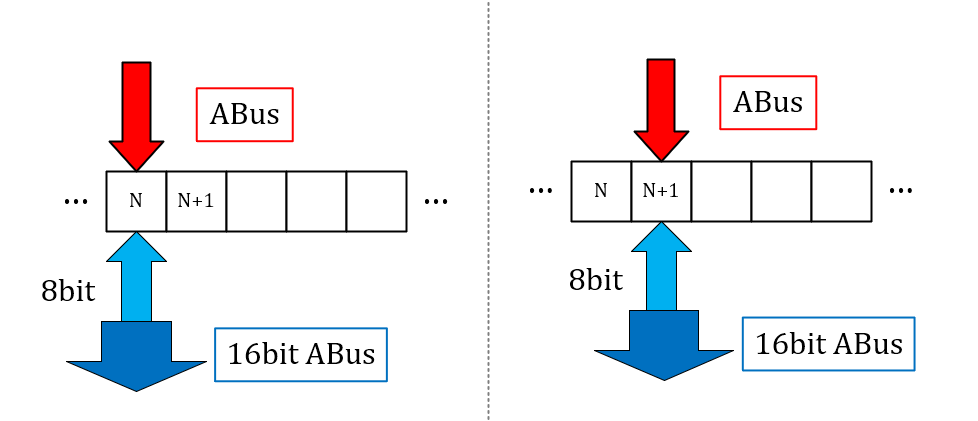

如果数据总线宽度是16bit,但是此计算机却按照字节编址,要如何设计?(此计算机一个读写周期只有一个地址在ABus上,此计算机不支持存储器并行工作)https://blog.csdn.net/_

分析

按字节编址,但数据总线却有两个字节宽,这说明此计算机必定采取了某种措施使得 一个读/写周期内 最多 可以读取/写入两个字节,再详细点,一个周期内可以读写一个字节也可以读写两个字节,这是怎么做到的呢?

(数据总线要充分利用,那就必须同时在上面并行传输16bit数据,这样传输16bit的数据效率最快。”同时”就意味着在一个存储器读/写周期内。“最多”意味着可以一个字节也可以两个字节,最好是两个字节但是一个字节也可以。)

https://blog.csdn.net/_

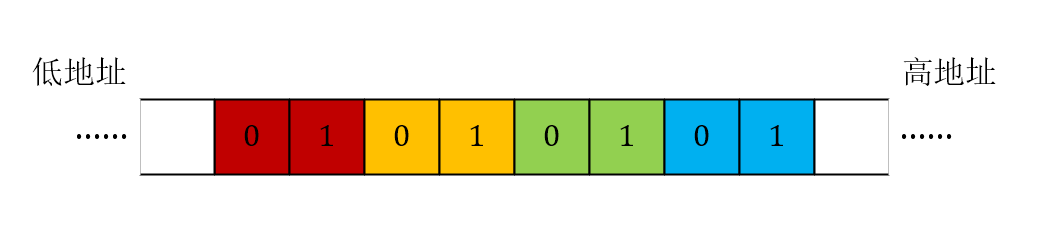

我们知道如果计算机按字节编址,且存储器一个存储单元有8bit,那么总线上的一个地址对应一个存储单元,即一个读写周期内,给一个地址就可读写一个字节。(如下所说的“地址”是指总线上的地址,“片内地址”是存储器内部的地址)

一个地址读写两个字节,很自然地想到使用位扩展,扩展成16位之后一个地址就可以读两个字节。但是问题来了,按上文位扩展之后,就变成按字编址,与按字节编址不符。

https://blog.csdn.net/_

回到问题上来,我们的目标是一个周期内,一个地址既可以读出一个字节又可以读出两个字节。(更严谨的说法是存在一个地址,既可以从这个地址读出对应的一个字节,又可以读出对应的两个字节)由于地址是相同的,那么读一个和两个字节这两种状态必然受除地址之外的最少一个因素的制约。

https://blog.csdn.net/_

假设这个因素具体化为B。当B=0时给一个地址读一个字节,当B=1时给一个地址读两个字节。新的问题来了,B=1时,一个地址读出的两个字节究竟是哪两个字节呢?显而易见的,是向这个地址写入的那两个字节,而且往往这两个字节作为一个整体具有一定的意义。整体具有意义那么最直观的方式就是将这两个字节写入相邻的两个地址,即连续的两个地址。相邻的两个地址又有两种不同的情况。

https://blog.csdn.net/_

假设这个地址为1010 b,那么向1010 b写入两个字节有两种可能,写到1010 b与1011 b,或者1010 b与1001 b

我们取左图情况继续分析,即取这个地址N和下一个地址N+1作为写入2字节的存储单元的位置。

https://blog.csdn.net/_

N有奇偶之分,暂定N为偶数,有很多个这样的地址对(N,N+1)

给定地址N,B=1可以访问N,N+1的两个字节,N(N+1),B=0则可以访问N(N+1)的一个字节,给定两片C怎么组织?

https://blog.csdn.net/_

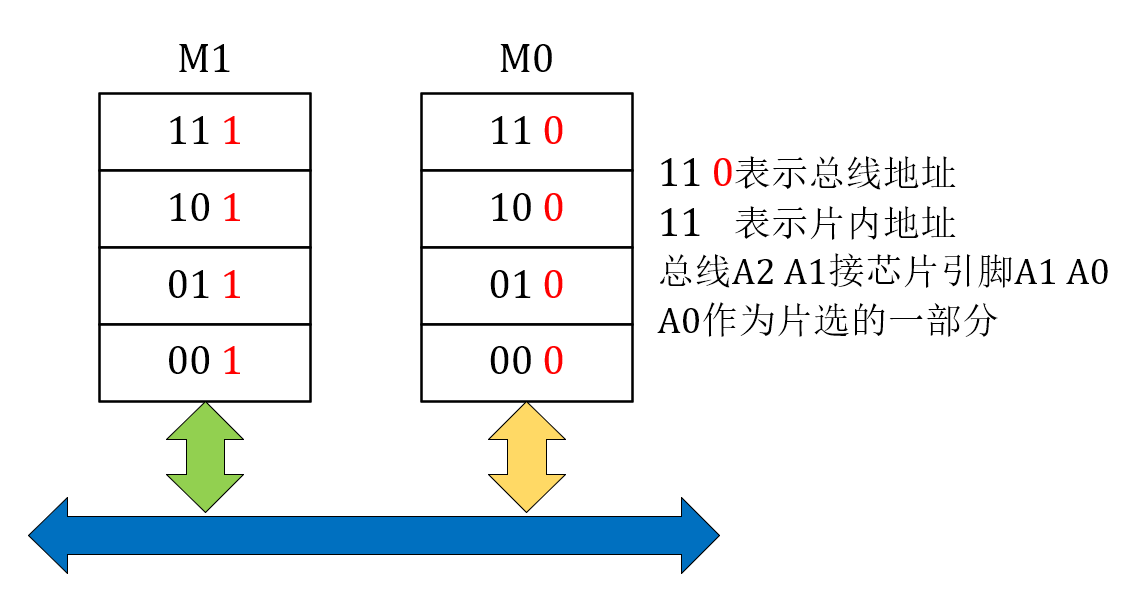

从N与N+1入手,N为偶数,可以表示为xy0 b,N+1就表示为xy1 b,其中xy完全一样,最后一位0/1决定是奇数还是偶数。在本文地址总线连接与片选信号选择这一部分我们发现取A2 A1做片内地址,可以访问4个双字节。如果采用这个设计,那么给定地址xy_ b(xy0 b或xy1 b),就可以访问xy0 b与xy1 b组成的双字节,但是无法访问单字节,如何改进呢?我们知道单字节是有奇偶之分的,也就是说地址上的A0有0,1之分。A0为0时访问偶字节,1时访问奇字节。

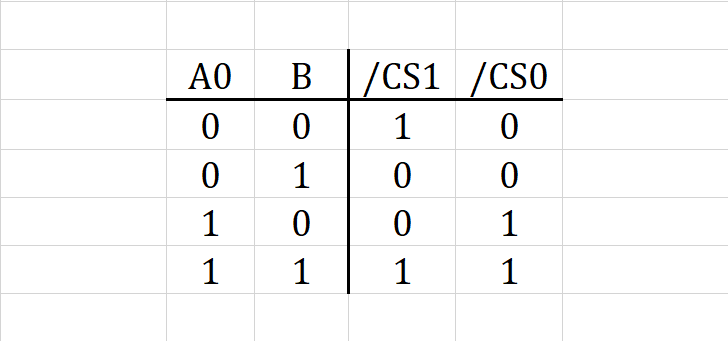

很自然地,将A0作为片选信号,A0=0且B=0,读偶字节,A0=1且B=0读奇字节,A0=0且B=1读双字节,那还有一种情况呢?A0=1且B=1,字面意思是我要从奇地址读出从这个地址开始的连续两个字节,这与”N为偶数””取这个地址N和下一个地址N+1作为写入2字节的存储单元的位置”这两个前提是矛盾的。所以这种情况干脆就啥都不做。

https://blog.csdn.net/_

真值表

/CS1 = A0 B + /A0/B

/CS0 = A0 /B + /A0 B = A0

怎么取奇数地址的开始的连续两个字节呢?并行转串行,先取奇字节,再取偶字节,分两个周期取。

如果N为奇数呢?N+1为偶数,给地址N,取N,N-1的数据,只需将A1做片选,剩下做片内地址即可,不过这种方式不符合从小到大的地址增加方案。

N为奇取N,N+1;N为偶取N,N-1这两种方案,N与N+1或N与N-1之间存在这样一个问题,1+1 0-1涉及到进借位,相邻地址之间转换关系复杂。

权衡利弊之后,我们还是取上述给定偶地址取偶地址开始之后两字节的做法。

这或许是8086计算机奇偶分体的由来。

奇地址所在的M1我们称之为奇体(odd bank)

偶地址所在的M0我们称之为偶体(even bank)

8086 CPU 34号引脚 /BHE(Bus High Enable)其实就与上述片选信号 /CS1相对应

8086计算机,两片8K*8bit的存储芯片如何扩展到16位?注意A0(/BLE)做片选,A1-A13做片内地址线。注意是A1开始,如果取A0-A12,存储器中有四分之一的存储单元不能读写!!!造成大量的浪费!!!读者可自行验证。

奇偶分体实质上是低位交叉编址,只不过数据总线宽度为16bit,偶地址一次可以拿出2*8bit的数据。

鄙人才疏学浅,如有不当之处,欢迎私信或评论区告知 [抱拳]

今天的文章

存储器的位扩展_什么是移位寄存器分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/80482.html