目录

一、门级结构描述

and 与门

nand 与非门

nor 或非门

or 或门

xor 异或门

xnor 异或非门

buf 缓冲器

not 非门

门类型引用模式: nand #10 nd1(a,data,clock,clear);

该例中nand表示与非门,#10是时间延迟,nd1是与非门名称,data,clock,clear输入信号,a输出。

二、D触发器基本原理及真值表

2.1 SR触发器介绍

2.1.1 触发器介绍

触发器是一种逻辑组合电路,其可存储一位二进制数,有两个稳定状态,SET(置位)和RESET(复位)。当输入信号发生改变并满足一定条件,输出信号随之发生改变。

2.1.2 SR触发器

作用:将输入信号转化为一个稳定输出。

SR触发器名称由来:S-SET设置,R-RESET复位。

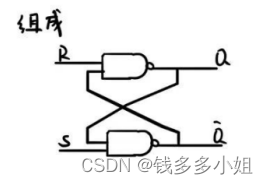

2.1.3 SR触发器原理图

触发器由两个交叉的与非门构成,其中一个与非门的输入是另一个的输出。其原理图如下:

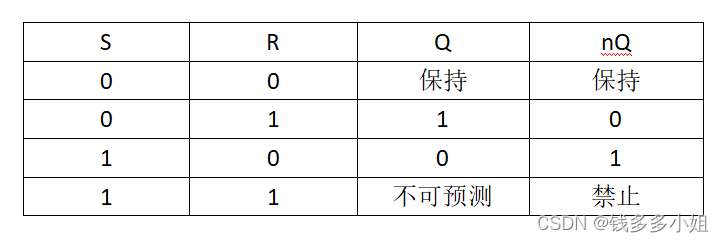

真值表如下:

2.2 D触发器介绍

2.2.1 D触发器原理图

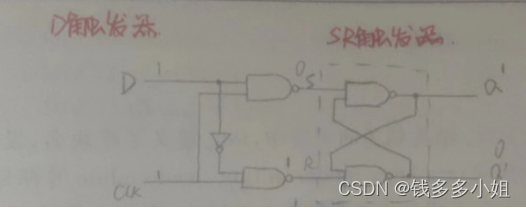

D触发器原理图如下:

2.2.2 D型触发器真值表

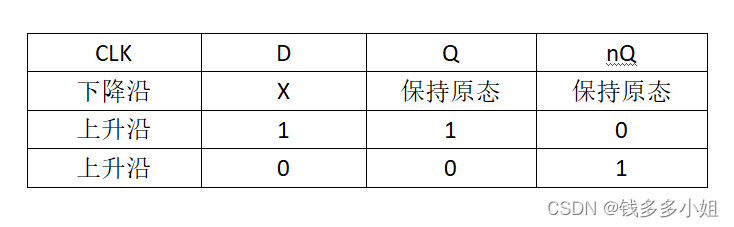

D触发器真值表如下:

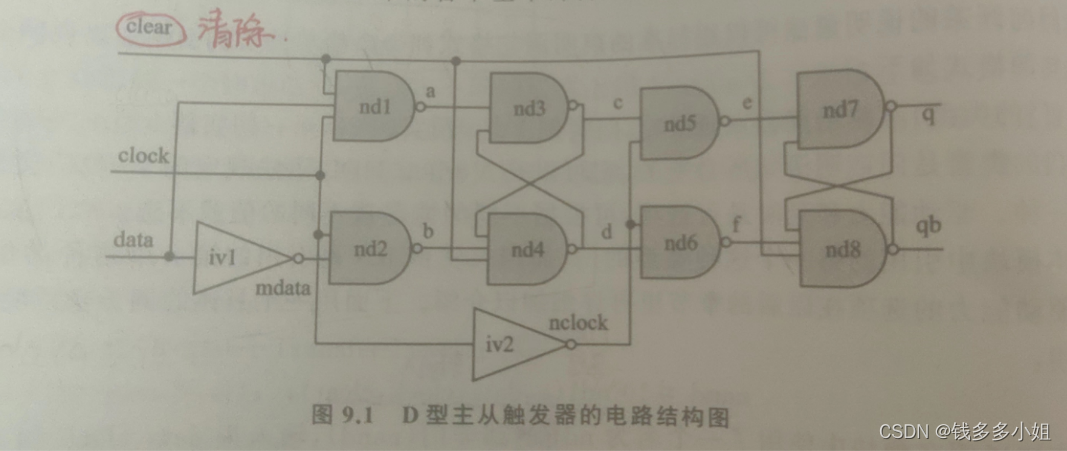

2.2.3 D型主从触发器原理图

D型主从触发器原理图如下:

2.2.4 门级结构描述D型触发器源码

module flop(data,clock,clear,q,qb);

input data,clock,clear;

output q,qb;

nand #10 nd1(a,data,clock,clear),

nd2(b,ndata,clock),

nd4(d,c,b,clear),

nd5(e,c,nclock),

nd6(f,d,nclock),

nd8(qb,q,f,clear);

nand #9 nd3(c,a,d),

nd7(q,e,qb);

not #10 iv1(ndata,data),

iv2(nclock,clock);

endmodule该处我们使用门级结构对原理图进行描述,代码中的门与电路图中一一对应,相当于使用代码绘制硬件电路,经过RTL仿真后可得到对应原理图,由于图片内容较为繁杂,对此我们不再截出。感兴趣的可点击下方工程文件自行进行电路仿真,观察结果。

三、代码编写及仿真

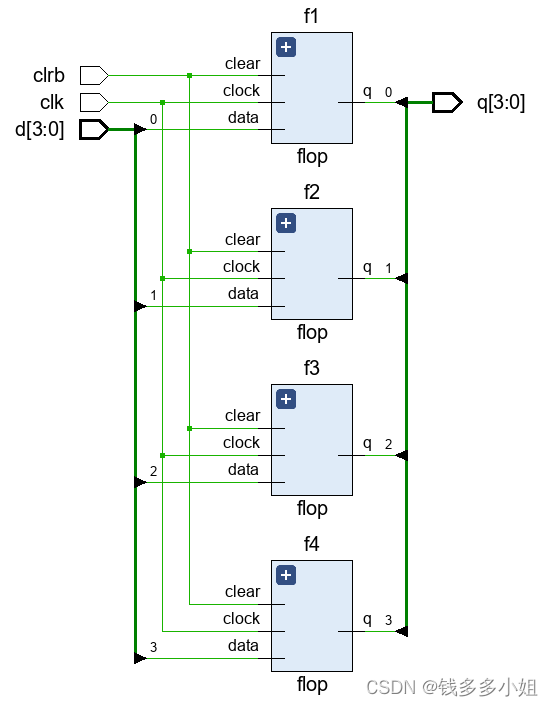

3.1 由触发器组成带清零四位寄存器

`include "flop.v"

module hardreg(d,clk,clrb,q);

input clk,clrb;

input[3:0] d;

output[3:0] q;

flop f1(d[0],clk,clrb,q[0],),

f2(d[1],clk,clrb,q[1],),

f3(d[2],clk,clrb,q[2],),

f4(d[3],clk,clrb,q[3],);

endmodule3.2 RTL仿真图

3.3 仿真测试文件

module hardreg_sim;

reg clock,clearb;

reg[3:0] data;

wire[3:0] qout;

`define stim #100 data=4'b

event end_first_pass;

hardreg reg_4bit(.d(data),.clk(clock),.clrb(clearb),.q(qout));

initial

begin

clock=0;

clearb=1;

end

always #50 clock=~clock;

always @(end_first_pass)

clearb=~clearb;

always @(posedge clock)

$display("at time %0d clearb=%b data=%d qout=%d",$time,clearb,data,qout);

initial

begin

repeat(4)

begin

data=4'b0000;

`stim 0001;

`stim 0010;

`stim 0011;

`stim 0100;

`stim 0101;

`stim 0110;

`stim 0111;

`stim 1000;

`stim 1001;

`stim 1010;

`stim 1011;

`stim 1100;

`stim 1101;

`stim 1110;

`stim 1111;

#200->end_first_pass;

end

$finish;

end

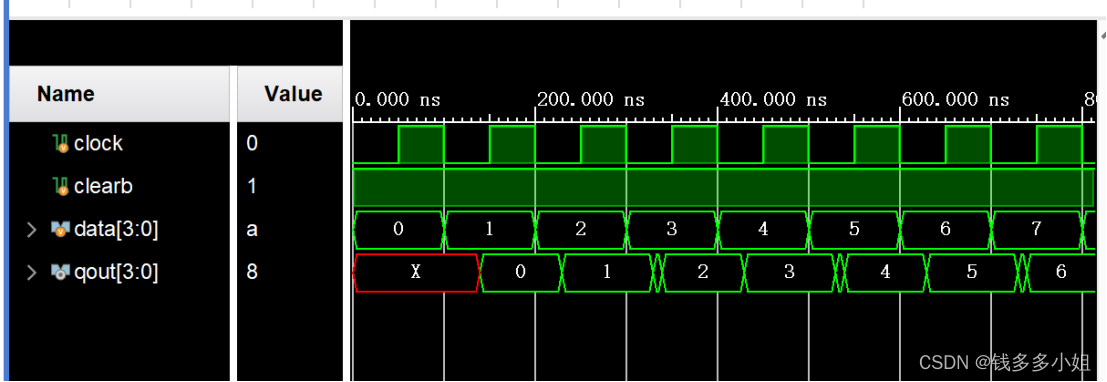

endmodule3.4 仿真波形

可以看到,在时钟上升沿来临,再延迟一段时间后,D触发器输出qout,其值与data输入基本一致,但不时会出现一些毛刺信号,毛刺信号的出现是由于延迟作用,同一时刻多个信号到达终点从而产生了竞争。如感兴趣可参考网络上多种方式对其进行消除。

工程文件连接:链接:https://pan.baidu.com/s/1jhtXhwztxQpHKHu7n54PmQ

提取码:90ce

今天的文章verilog学习记录(3)——D触发器设计分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/82819.html