本博文是博主记录DFT实训教程的笔记版本,此笔记并没有对所有的知识进行记录,仅仅以自身的认知水平,来记录了一些部分笔记并加上了自己的理解。

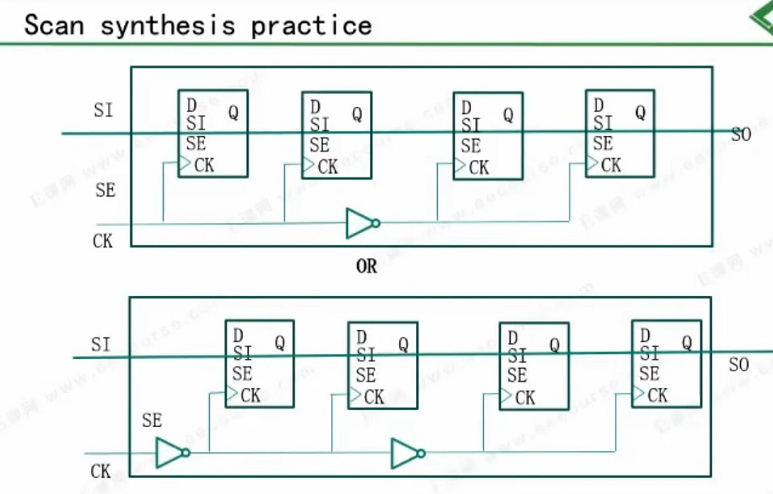

Scan synthesis practice

How to design scan clock structure?

假设一块chip里面有好几十个clock domain,如果每一个clock domain都用一个scan clock虽然会非常清晰,但是IO数目肯定不够用。

clock group:

1、no crosstalk

2、less crosstalk

3、functional clock frequency

如何理解串scan时候的不同沿触发的寄存器

脚本:

#configure library

set search_path "$search_path ./netlist ./lib"

在原来的search_path的基础上做一个补充

set target_library {

./lib/typical.db}

该命令主要是在逻辑综合中用,为了脚本的一致性,也放在这里。

set link_library {

* ./lib/typical.db}

需要去找这里library的定义

#read and link the design

read_verilog -netlist ./netlist/top.v

读取netlist文件

current_design top

设置顶层文件

link

做一个链接

#configure_DFT

set_scan_configure -chain_count 1

配置一条chain

set_dft_signal -type ScanClock -port clk -view existing_dft -timing {

45 55}

#preview and inset DFT

create_test_protocol

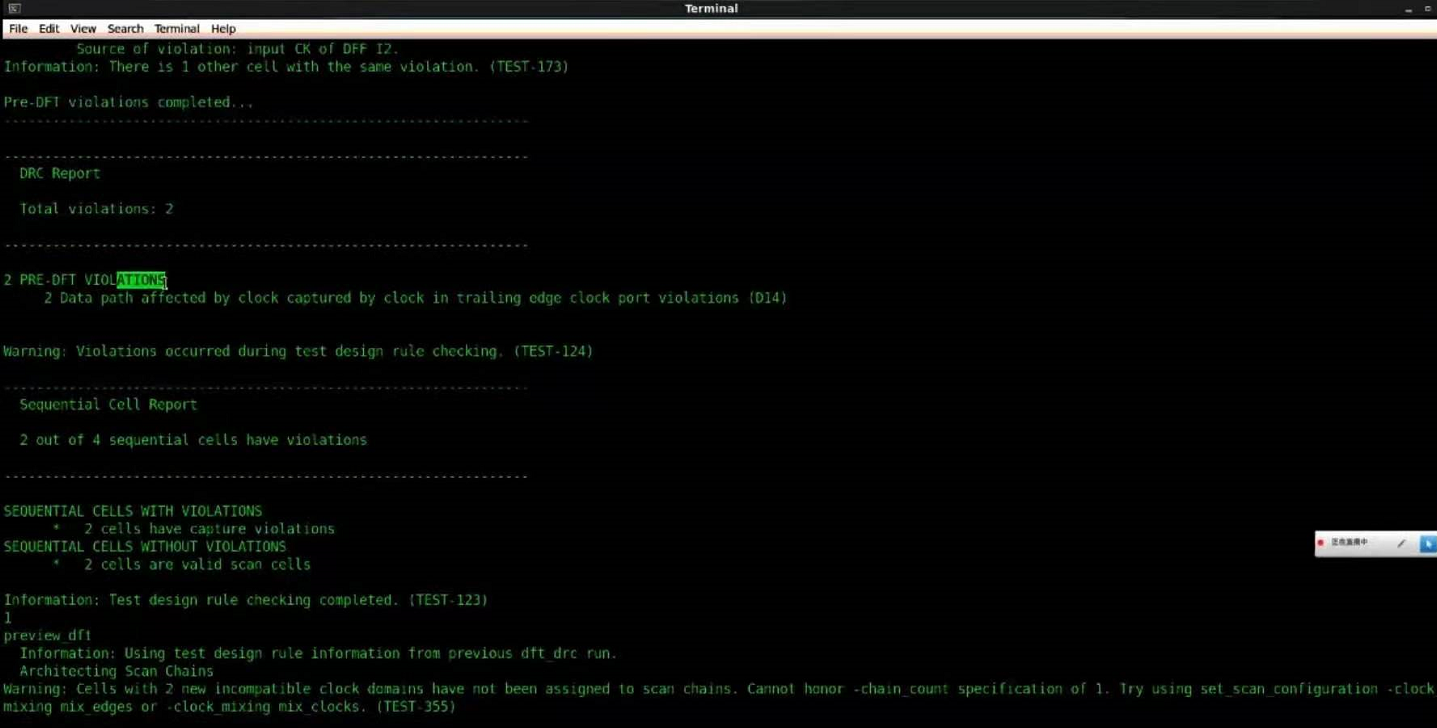

dft_drc

现在做分析

preview_dft

先根据分析结果,给出preview的报告

insert_dft

真正去做DFT scanchain

dft_drc

再做一遍DFT drc

#write out design information

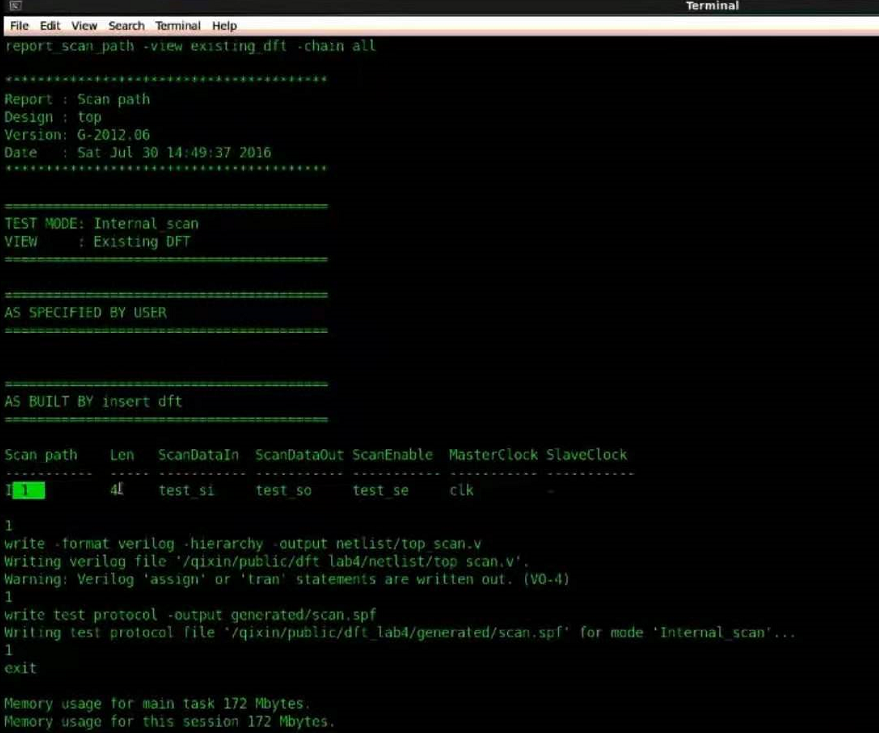

report_scan_path -view existing_dft -chain all

write -formate verilog -hierarchy -output netlist/top_scan.v

write_test_protocol -output generated/scan.spf

exit

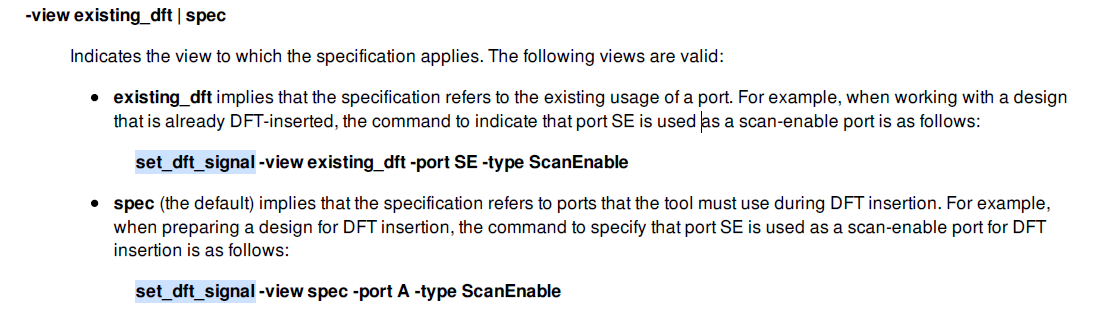

如上图所示,对于那些已经存在的,已经链接好的,可以拿来直接使用的port,就可以用existing_dft命令,所以脚本里面对于clk是用的exsiting,如果是对SE的话,就必须用spec了。

对于还没有串,没有链接的port,就必须用spec端口来指定。比如SE端口,就需要用spec来指定为ScanEnable。

现在读入netlist文件,该文件是如上图所示的两个负沿触发的reg和两个正沿触发的reg,并且我们设置了1条chain,如下图所示,报告除了violation

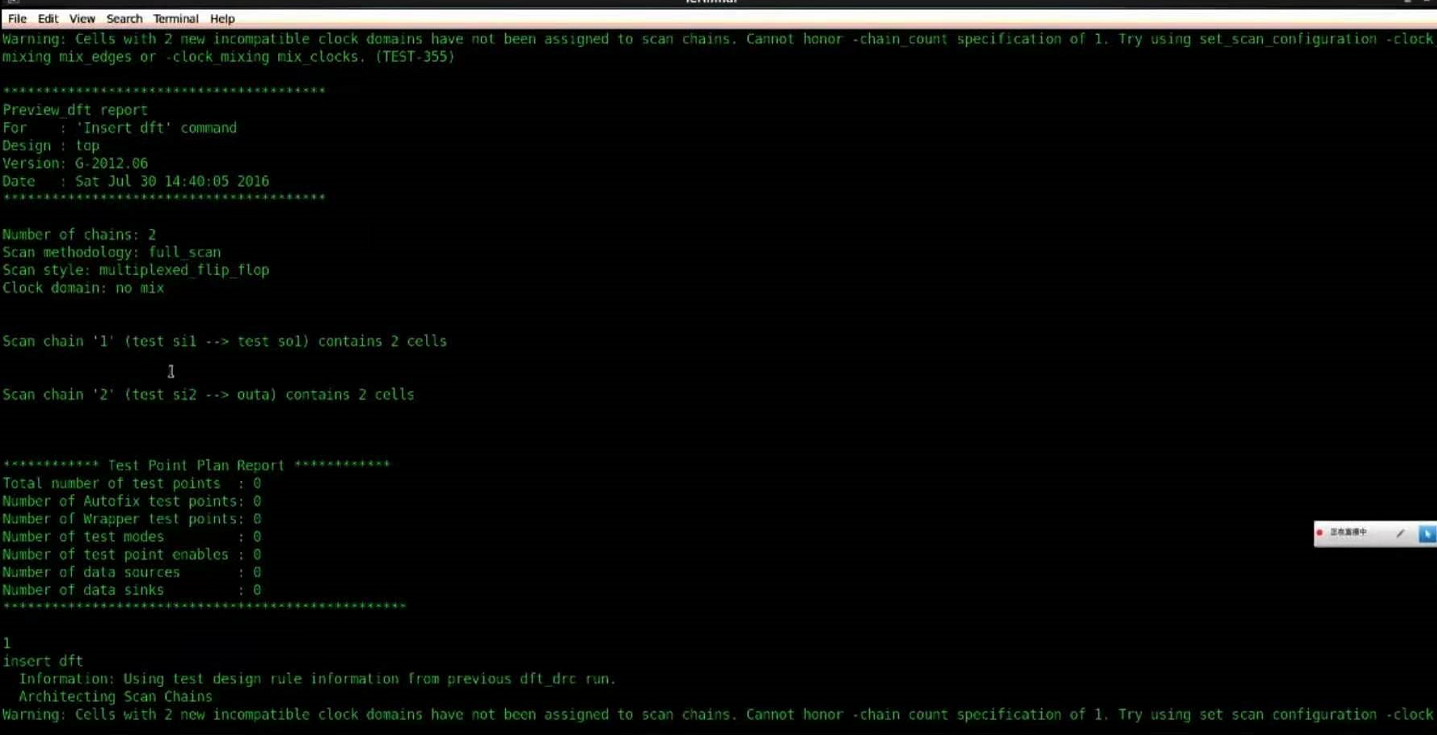

如下图所示,虽然我们指定了chain count=1但是tool还是做成了两条chain,其中一条chain包含了2条cell,另一个chain也包含了两条cell

查看已经串好的scan的netlist,验证确实是两条chain,也就是工具默认情况下,是不允许这种双沿的串在一起。现在需要更改工具这中默认的行为。

查看set_scan_configuration 这条命令的文档。

后面有一个参数是-clock_mix no_mix | mix_edges | mix_clocks | mix_clocks_not_edges

也就是说-clock_mix有四个变量选项:

1、no_mix代表的是任何情况下都不能去混合时钟

2、mix_edges代表同一个clock domain 不同clock edge可以去混合串不同edge的reg

3、mix_clocks代表不同clock domain,不同edge都可以放在一条scan chain上面。

4、mix_clocks_not_edges代表不同的clock domain可以混合,但是,不同的edges不可以混合。

现在在脚本里面更改

set_scan_configuration -clock_mixing mix_edges

如下图所示,当重新运行脚本之后,Scan path变为了1条,chain length变为了4

退出dc的gui使用gui_stop

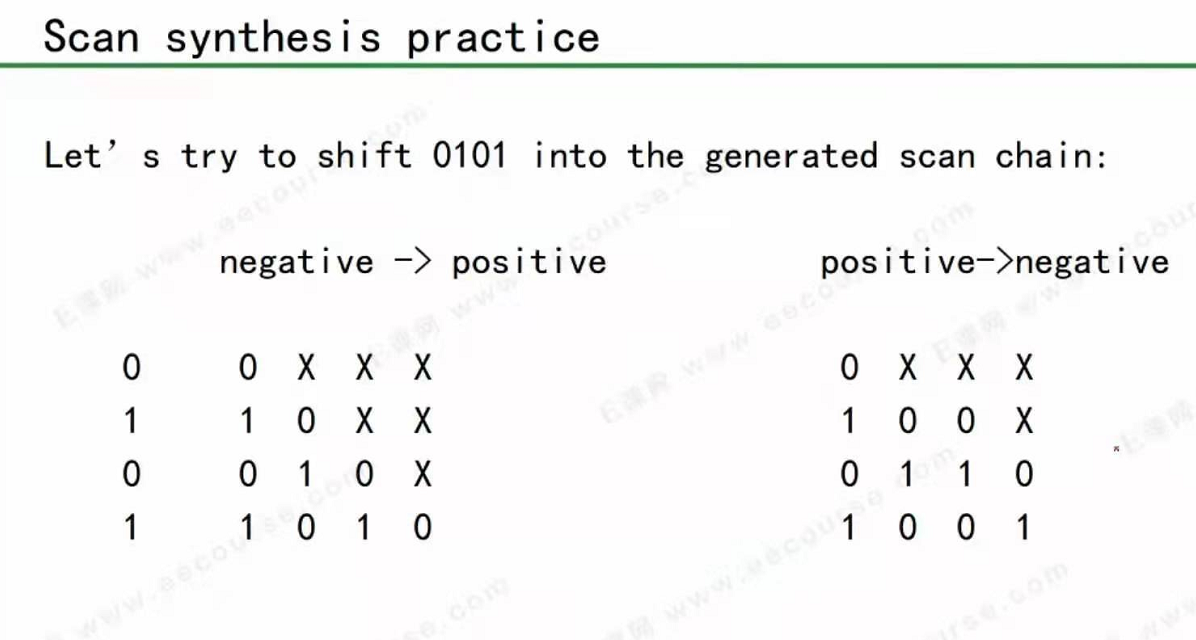

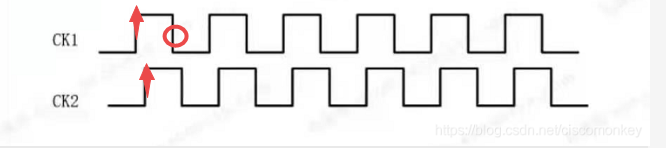

通过检查scan insetion后的netlist后发现,工具将负沿在前面,正沿在后面。为什么需要这样串chain?

如上图所示,关键一点,在一个cycle内,数据会被捕获两次,从而导致两个正沿在前负沿在后的两个寄存器的值保持了相同,被绑定。导致经过这个跨沿的后续reg均错误得到值。

总结:越晚capture的cell越放在前面去,这样保证他不能立即capture到前面cell最新的那个值

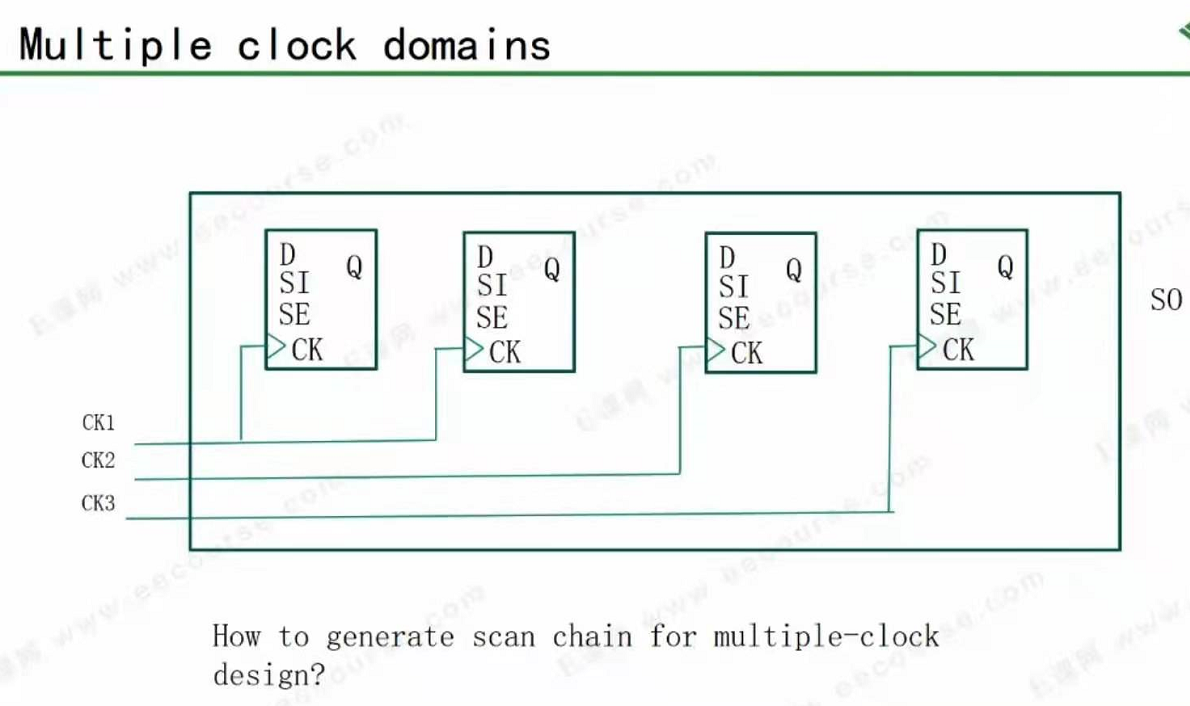

如上图所示,对于一个design来说我们可能有多个clk_domain,虽然每个clk_domain分别链接一个clk最清晰,但是我们很可能没有这么多个clk port。

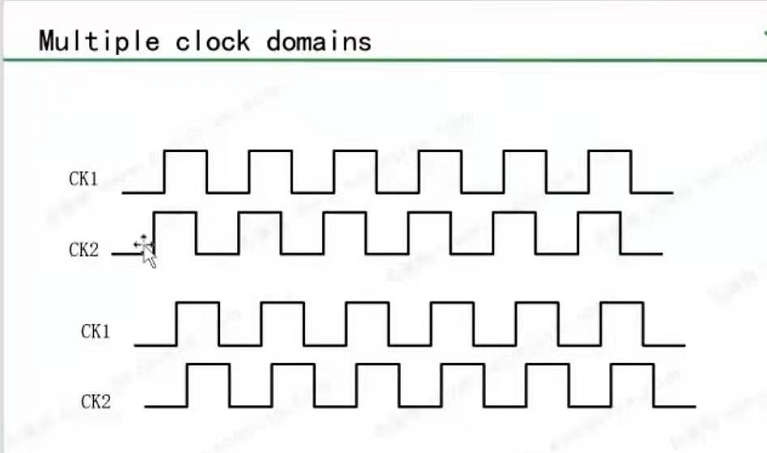

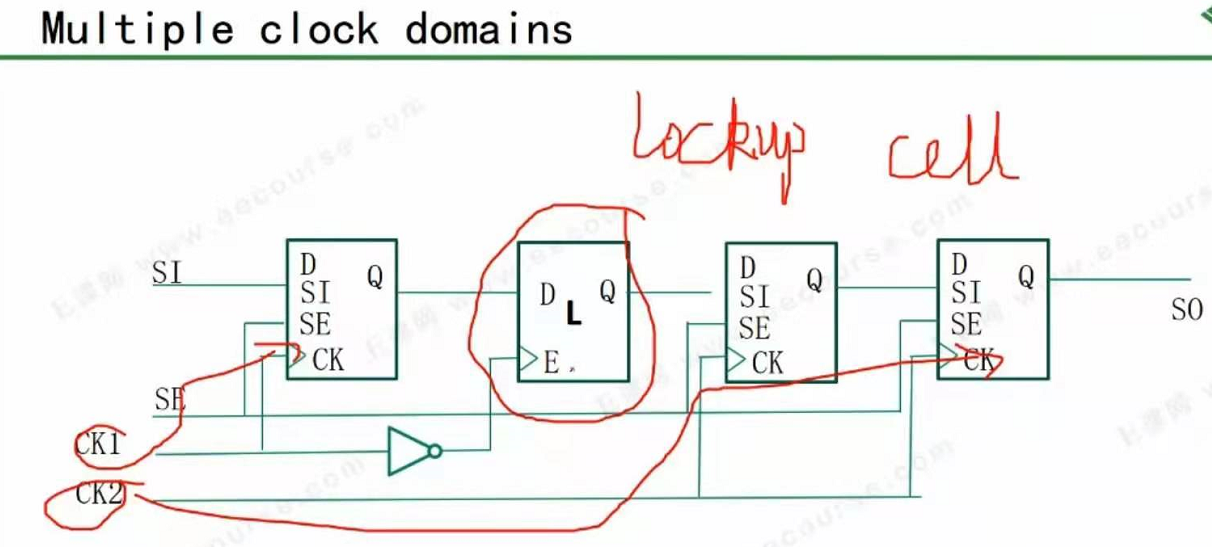

如下图所示,现在将这四个cell串起来,假设第二个和第三个reg之间的路径比较长,就会导致严重的skew的问题。

如下图所示,可以分为下面两种情况,对于第二种情况,如果skew过大后,就可能导致抓取的是最新的值,而不是前一个cycle的值。从而形成了两个寄存器之间的数据一直是绑定的。

如何解决这个问题?

如上图所示,为了解决这个问题,需要在时钟域之间加上一个lockup latch,这个lockup latch电平触发,与前面一个reg的触发沿取相反值。

当加了一个反的lockup latch之后,相当于将数据延迟了半个cycle,延迟到了下降沿的位置,只要skew不超过半个cycle,就可以保证clk2不会抓到最新的那个值。

如下图所示,因为加个反向的lockup latch可以将数据延迟半个时钟周期。从而相当于把clk2的捕获沿在前面,clk1的捕获沿在后面。当使用不同的clk domain时候,如果将scan串起来,工具会自动加上lockup latch。

在做DFT时候,经常用到的signal总结如下

Scan clock:

Reset/Set is also treated as a clock

Scanenable:it is 1 in shift, when capture it is 0

Scan mode/Test mode: always 1 in the whole test mode

Scan input/Scan output

Scan Design Rules-clock

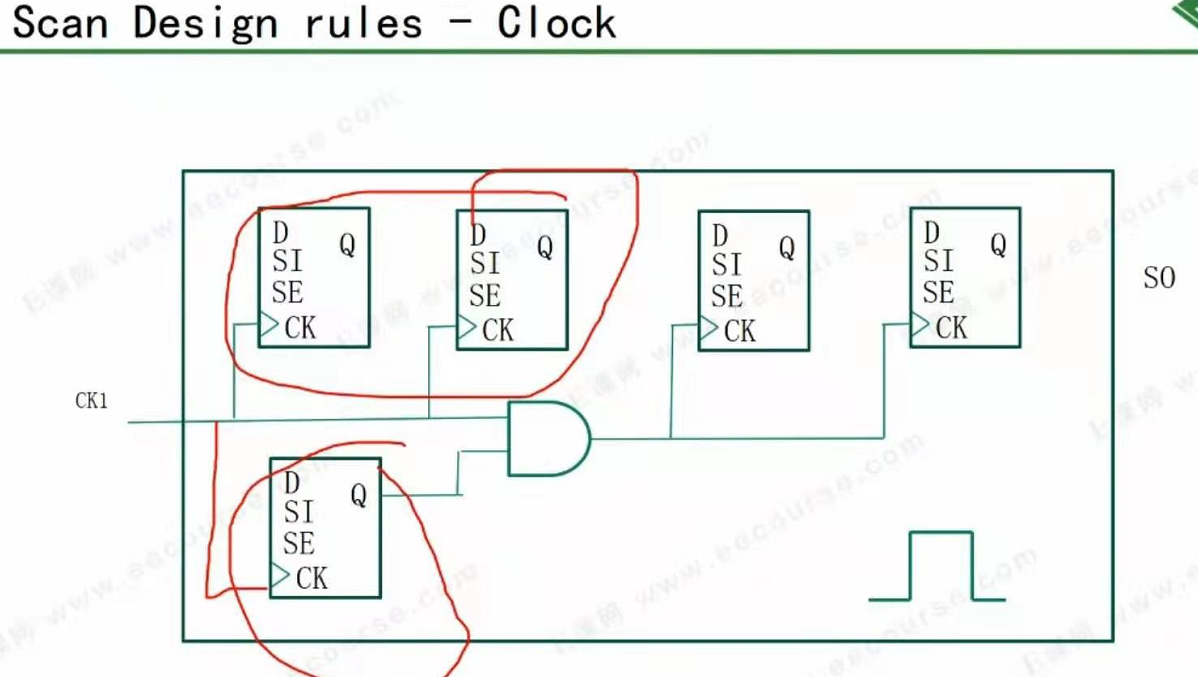

这个cell能不能串到scan chain上面去的标准是什么?

scan chain是不是能够正确的shift in shift out 是这个方法的基础,也就是说如果我把这个cell串到scan chain上面去,那他的shift in shift out是否会有问题。

如上图所示,后面两个cell的时钟受到了一个与门的控制,并且受到了Q的输出的影响,因为工具把前面三个cell串起来后,在shift 阶段,Q的值是变化的,从而导致经过与门后面的时钟是变化的,所以,如果将后面两个串起来的话,后面两个cell就没法正确的shift了。

而我们想做的是一个full scan,那么在不影响function的情况下如何解决这个问题。上面设计属于为了节约功耗low power而设计的一种门控。

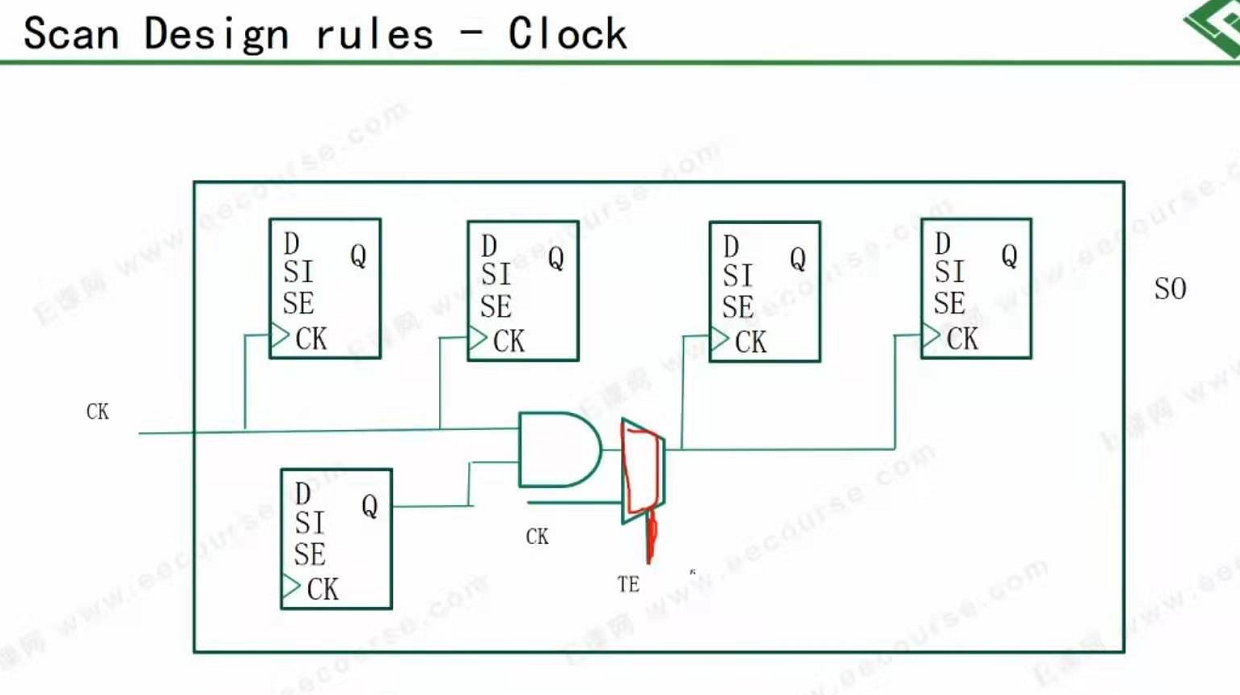

如上图所示,通过增加一个mux而解决了clk可控的问题。

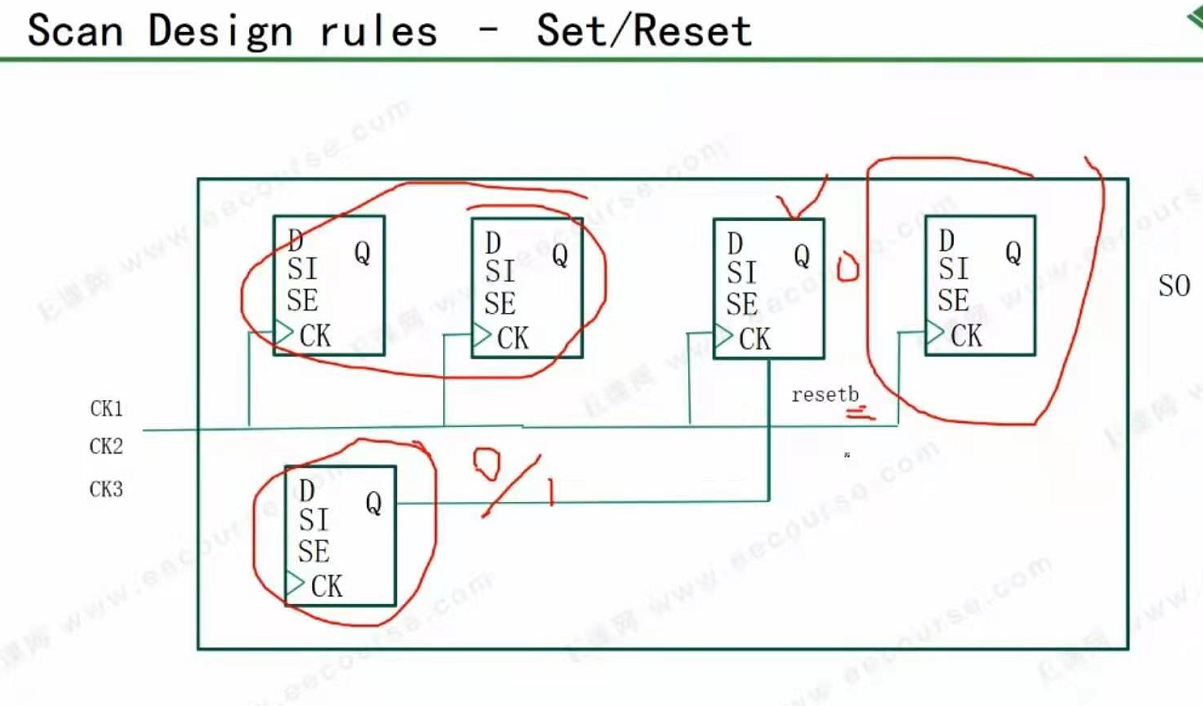

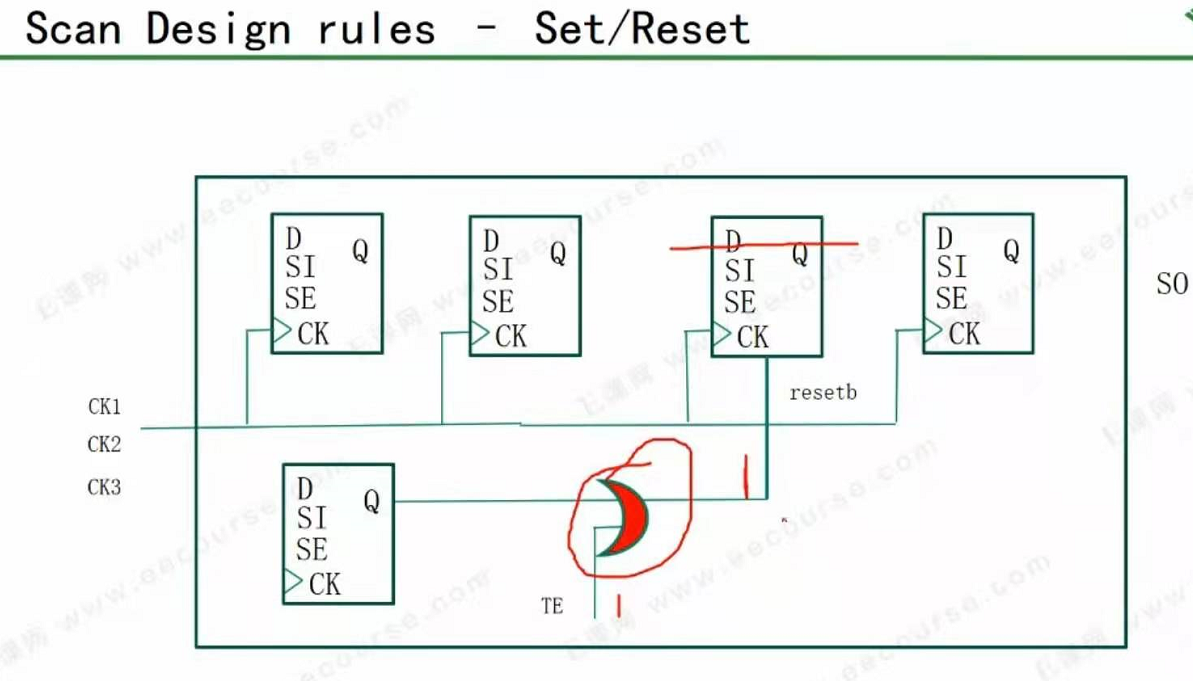

在predft阶段主要是针对clock和set/reset的问题。

同样如上图所示,由于reset被cell/Q控制,从而在shift阶段,你没法控制这个cell的值,所以没法串到chain上面去,解决的方法,要么是用autofix,要么反馈给Designer修改设计。

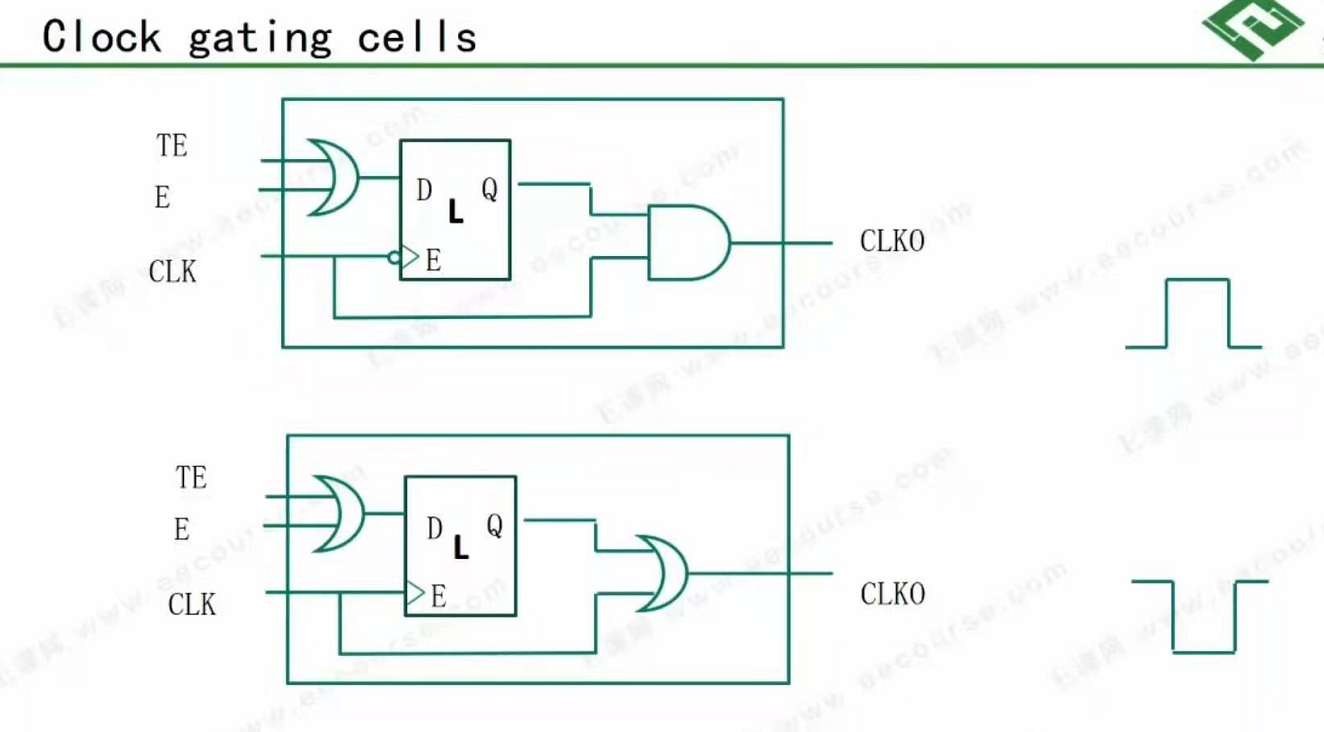

clock gating cell的设计

clock gating cell的目的就是为了省power,在这些逻辑不工作的时候,我可以通过clock gating cell 来省power,如果用与门来控制就会产生glitch。通常有两种设计:这个在综合的时候可以在综合的时候交个工具替换,添加:

如上图a所示,输入的时钟是010,如上图b所示,输入的时钟是101。

值得思考的问题:

1、除了MUX-D scan cells,再列出两种scan cell并简述

2、Measure PO的动作可以发生在capture之后吗?为什么

3、详细分析为什么lockup latch能解决clock skew的问题?

4、create a test case with reset scan violation and then fix them with EDA tool Autofix feature。

简单介绍如何使用autofix

通过在脚本中增加新的脚本command:

set_dft_configuration -fix_clock enable

set_autofix_configuration -type clock

第一条命令是希望工具能fix clock相关的问题,默认是disable的,所以这里需要enbale

第二条命令是auto fix的配置,告诉他fix clock相关的问题,这样的话,工具就会fix clock相关的问题。

今天的文章dft课程_DFT计算分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/82891.html