前言

之前上课的时候留的一个作业,找一篇相关文章分析,先把文章大致分析发出来,下一节对文章内容进行仿真。

文章原文:M. Almada-Gutierrez, F. Sandoval-Ibarra and R. Sanchez-Fraga, “Integrated NMOS Differential Amplifier,” 2022 IEEE Latin American Electron Devices Conference (LAEDC), Cancun, Mexico, 2022, pp. 1-4, doi: 10.1109/LAEDC54796.2022.9908177.

集成 NMOS 差分放大器

文章首先分析NMOS电路的工作原理及主要问题。电路采用NMOS技术,最小沟道长度5um。采用差分对作为输入级。

为了使差分对发挥适当的性能,每人晶体管的工作点必须保证它们都工作在饱和区,首先进行直流分析:为使M2管工作在饱和区,需使M2漏源电压大于栅源电压减去阈值电压:

另外,一旦电路偏置,输出节点的直流保持恒定

从而可以求出Vin2

这表明输入电压Vin2的增加会到最后M2管进入三极管区,Vin2的最大允许值由上式表示。接下来用法同样的方法对Vin2的最小允许值进行分析:

因此输入电压Vin2的上下限分别给出,接下来对电路进行仿真,考虑三级SPICE模型。

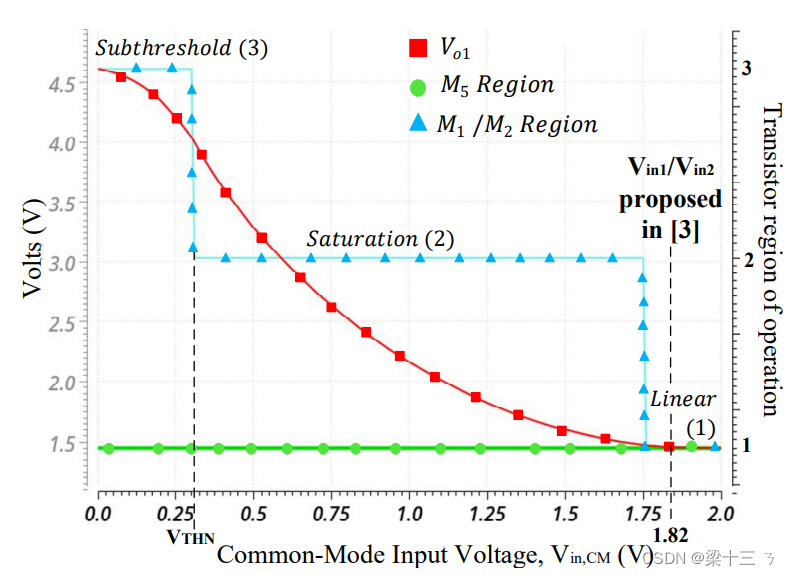

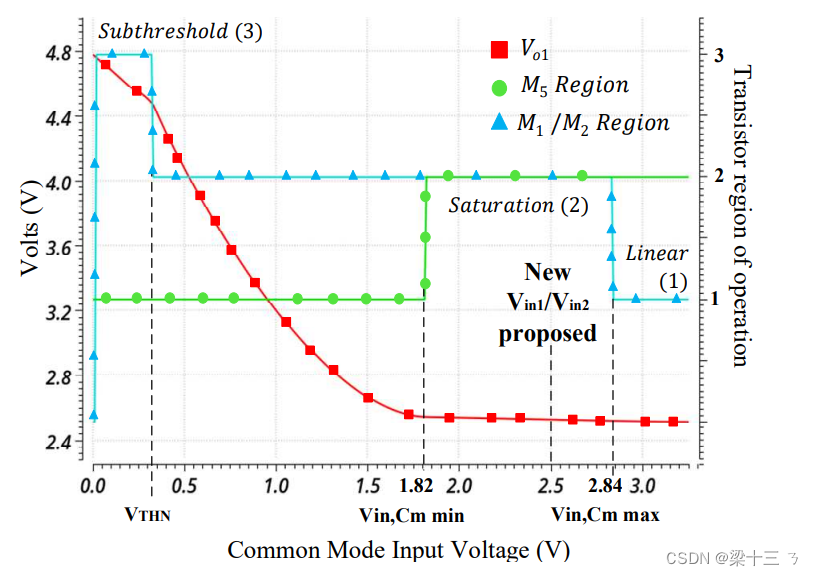

输出节点Vout1的直流电压以及晶体管M1、M2和M5的工作范围取决于共模输入电压(Vin,CM)。输出电压Vout1(由█表示)范围自VDD-VTHE至最大值。(▲)代表晶体管M1和M2的工作区域,对于较小的Vin,CM,晶体管处于亚阈值区域,只要条件VGS1>VTHN满足,晶体管进入饱和区,一直保持到Vin,CM达到最大值。而且对于任何的Vin,CM晶体管M5始终处于线性区域,用符号●表示。输出曲线这样的原因是VGS2=VGS5=1.82V而VDS5=1.24V,对于任何值都不满足Vin,CM的最小值。

针对以上分析,文章提出了一种可提高直流性能的新电路

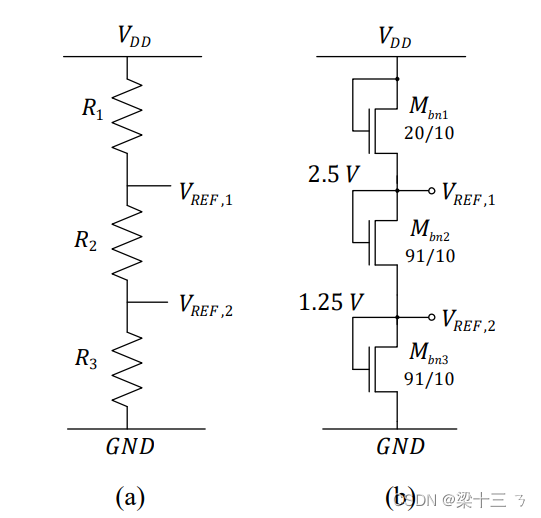

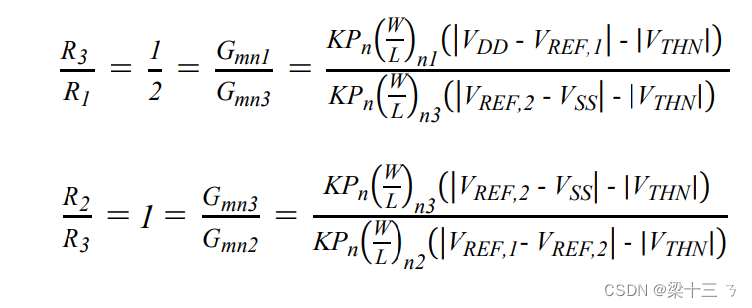

一种方法是使用有源分压器,(a)是一个电阻分压器,可以设计实现VREF,1=2.5V,VREF,2=1.25V,其中VDD=5V。使用NMOS等效电路如图(b)

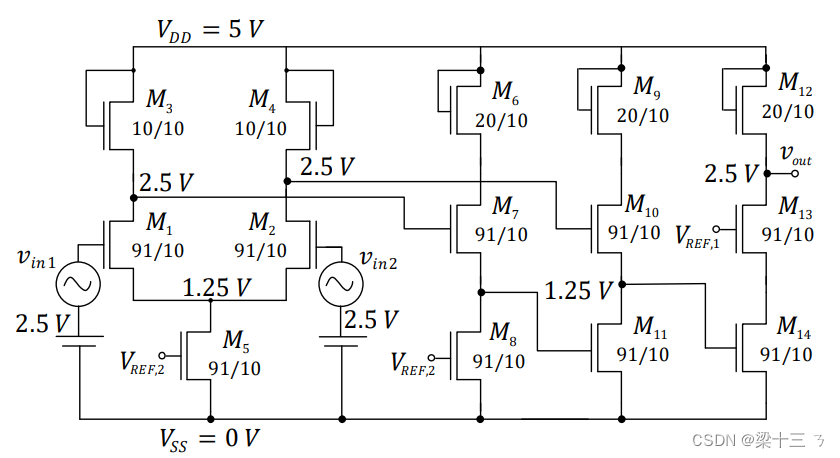

更换偏置电路可以重新构建放大器。分压器基于三个二极管连接的NMOS管,实现单级放大器,这是通过基于放大器类型识别将成为“输入”器件的晶体管并消除反馈回路来实现的。图中差分输入管的尺寸是为了在输出节点保持2.5V,在电流源M5的公共节点保持1.25V为此,晶体管M1和M5与Mbn2和Mbn3保持相同的尺寸,负载M3和M4的沟道宽度等于Mbn1的50%,这会在输出节点产生2.5V电压,因为由M5提供电流的一半分别流经管M3和M4。这反过来降低了负载晶体管的跨导,从而增加了电路的增益。

差分输入级输出节点处的直流电压(2.5V)允许后续级晶体管满足二极管连接条件,因为其几何形状与接下来三及偏置电路相同。输出级对应于共源共栅放大器,以便在完整差分放大器的输出节点保留建议的工作点(2.5V),共源共栅级的特性接收来直晶体管M14的信号响应由M13的漏极端子捕获,因为它是偏置电路的副本,所以在输出节点处保持2.5V。这有利于最大输出摆幅。

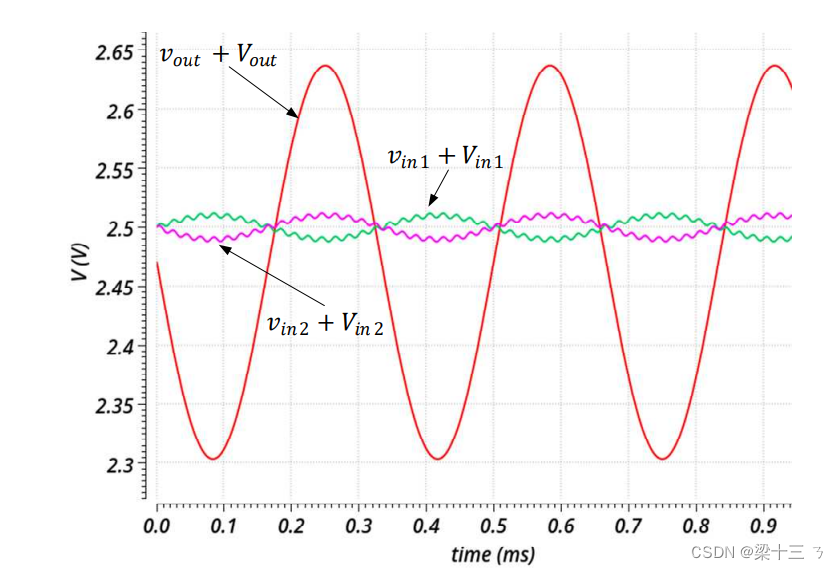

差分级的共模输入输出特性如下图。当共模输入电压等于建议的直流输入电压(2.5V)时,晶体管M1.M2和M5均工作在饱和区。存在约1V的变化范围。根据完整的差分放大器仿真,瞬态特性如图所示。在差分输入中添加带有“公共噪声”的10m交流电压,在输出节点处观察到了没有“噪声”的放大信号。以交流电而言,可获得18dB的低频增益,2pf的负载电容保持合理的相位裕度(约60°)。

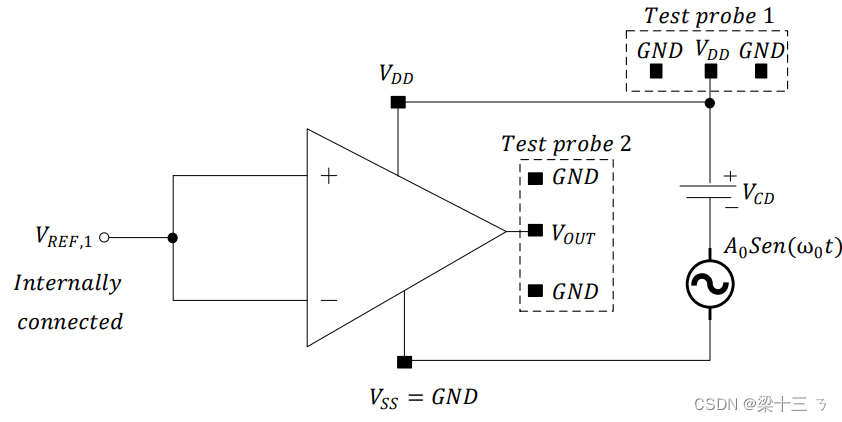

接下来用实验评估放大器的性能,该设备有一对测试探头,配置为“地-信号-地”。因此,DFT仅限于两个端口,并且设计了特定的实验来适应该情况。图中显示了一个示例。测量基于振幅A0交流电源的:(1)如果A0=0,测量偏移,(2)如果A0≠0,PSRR+被测量,(3)如果A0≠0并且正弦波发生器连接至VSS,PSRR-被测量。

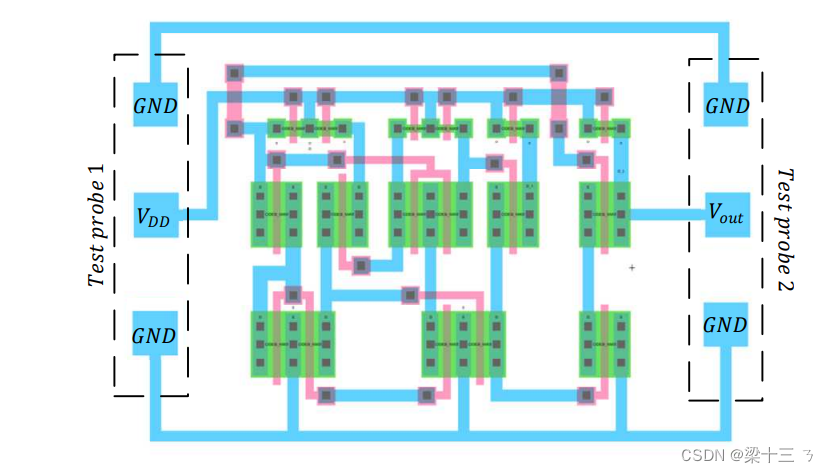

物理设计适应DFT,并且在Electric VLSI中执行的布局如图所示。该布局包括两个具有特定分布(地-信号-地)和测试探针几何形状的焊盘。因此,无需芯片封装工艺即可测试器件。物理设计的实现考虑了当前的失配减少技术:叉指技术允许对共享终端的设备进行分组以获得规则分布,从而实现集中分布,有助于减少硅各向异性的影响。另一方面,所有晶体管具有相同的方向并且避免重叠多金属,以减少寄生电容。

新差分放大器方案的设计方法允许晶体管稳定地工作在饱和区。电路仿真的瞬态行为证明了放大器消除差分输入“公共噪声”的能力。上述表明单通道差分放大器可用于多种应用。专注于测试设计的物理设计是获取测量数据的种选择,它是通过将实验适应于晶圆上测量的探针台来实现的,从而避免了集成电路测试的芯片封装过程。这项工作需要事先分析和设计实验。

今天的文章从0开始,模拟集成电路设计Cadence Virtuoso学习笔记(五)文章分析《集成NMOS 差分放大器》分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/83851.html