1 概述

本文用于讲解CLK_CFG_AD9516例程配置代码的使用说明,方便使用者快速上手。

2 例程功能

本例程 是采用verilog hdl编写,实现AD9516时钟芯片的配置,可根据使用例程修改项目需要的时钟配置,可直接使用。

具体的芯片介绍这里不做详细介绍,若需了解请自行查找资料。

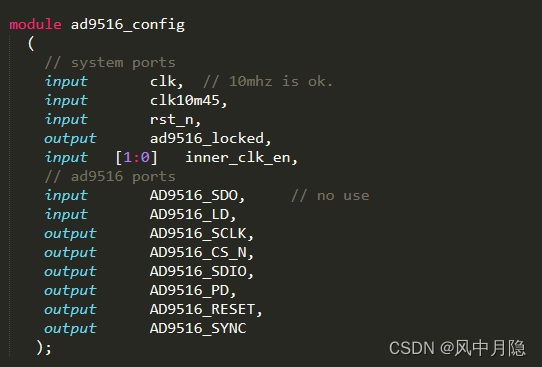

3 例程端口

ip的端口如上图所示,说明如下表所示:

表 1 端口说明表

序号 端口名 功能说明 备注

-

clk 时钟,如10MHZ -

clk10m45 时钟,如10MHZ,但相位相对于clk偏差45° -

rst_n 复位,低电平有效 -

ad9516_locked 锁定判定信号 -

inner_clk_en 时钟配置选择使能 默认为0x00 -

AD9516_LD 连接Ad9516的引脚 -

AD9516_SDO 连接Ad9516的引脚 -

AD9516_SDIO 连接Ad9516的引脚 芯片配置引脚 -

AD9516_SCLK 连接Ad9516的引脚 -

AD9516_CS_N 连接Ad9516的引脚 -

AD9516_PD 连接Ad9516的引脚 -

AD9516_RESET 连接Ad9516的引脚 -

AD9516_SYNC 连接Ad9516的引脚 一般不使用

4 数据时序

AD9516的配置模块时序是常规的SPI时序,这里就不做详细的介绍了,感兴趣的可以看手册学习。

5 注意事项

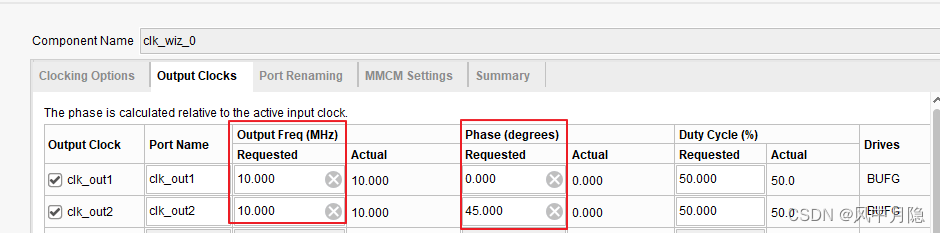

1) clk_10m与clk10m45两个时钟的频率一样,但相位相差45°,如下图所示;

2)clk的时钟可以不是10Mhz,但不能大于25MHZ(AD9516芯片的sclk的最大速率);

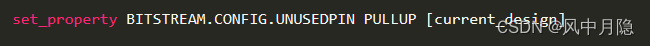

3)在fpga工程中将没有使用的pin拉高约束,如在xdc中设置如下约束;

6 调用例程

6.1 直接调用例程

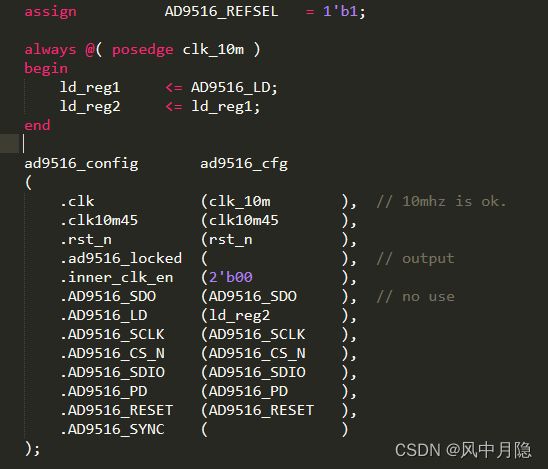

1)端口例化如下图所示:

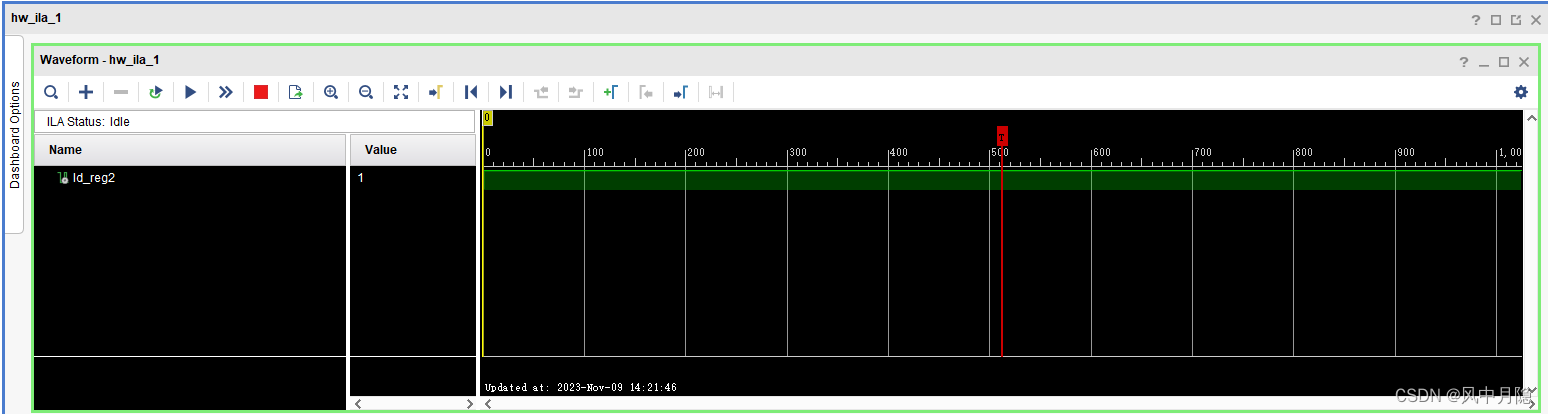

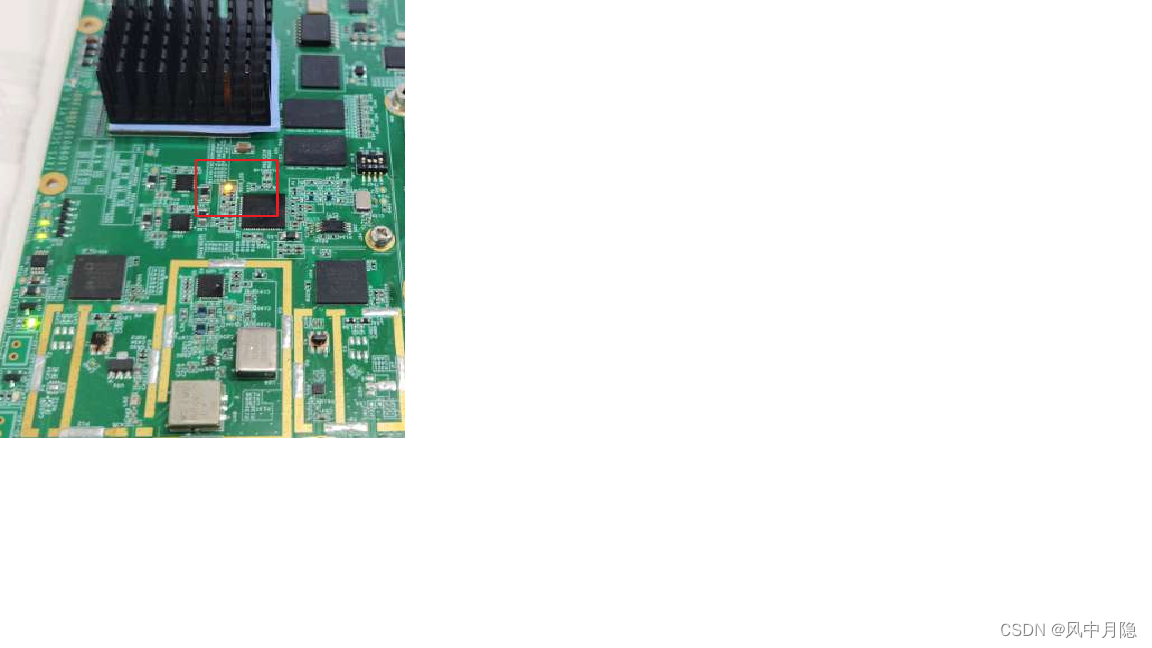

2)上板之后测试情况看到ld 为高说明初始化完成,同时可以看到AD9516的led指示灯为亮,如下图所示:

6.2 修改时钟配置输出例程

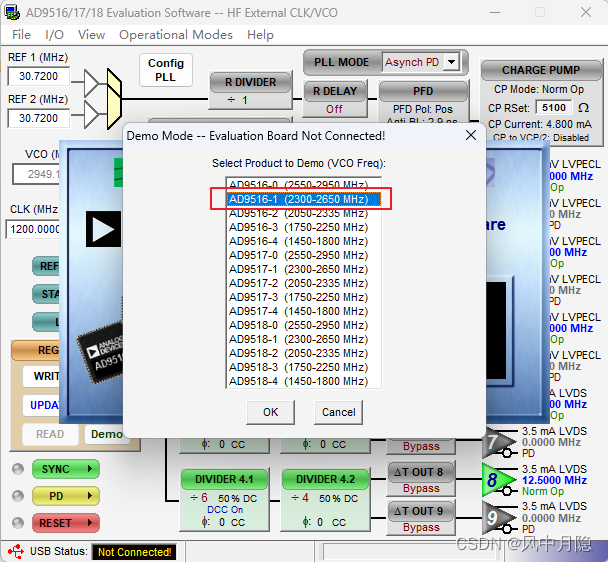

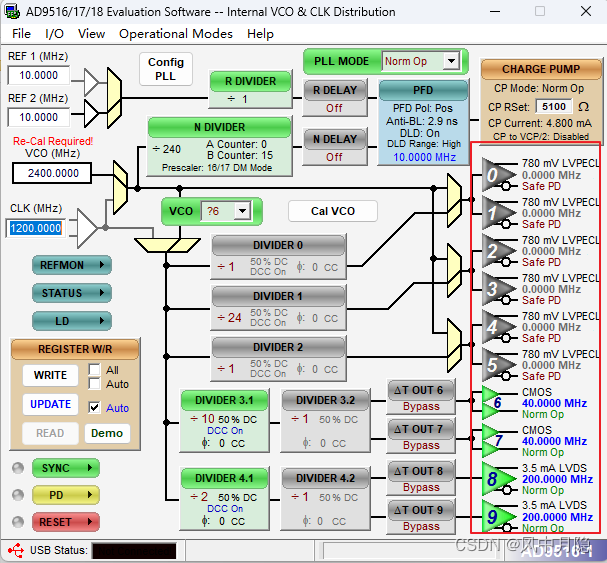

1) 打开AD9516的配置软件,选择对应的型号,本例程是AD9516-1,如下所示:

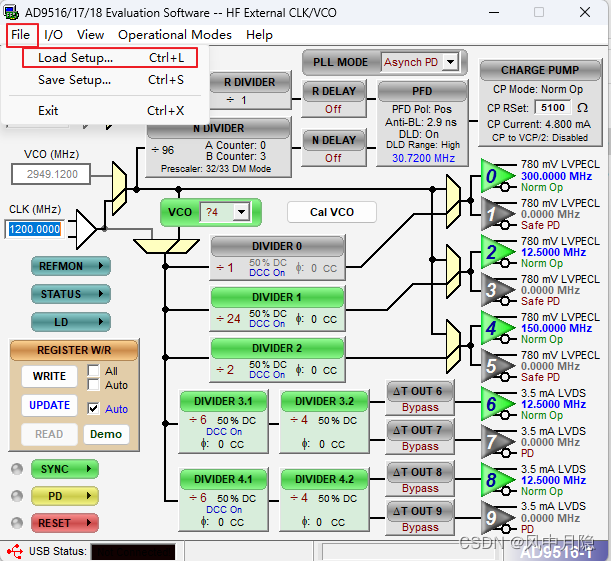

2) Load 例程配置:

3) 根据运用修改时钟输出:

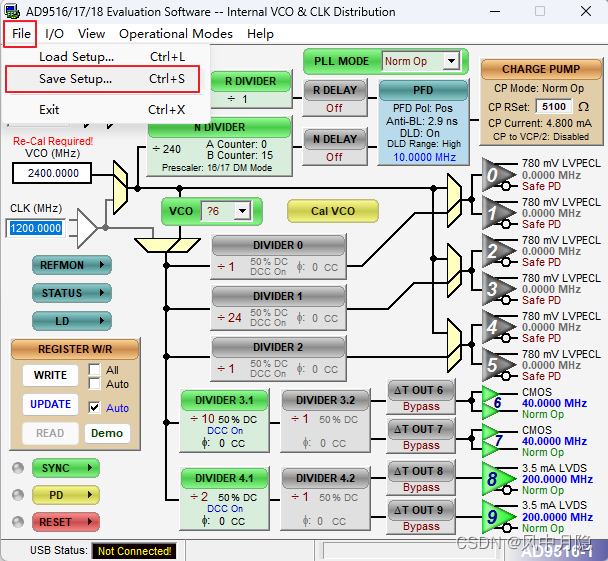

4) 导出配置:

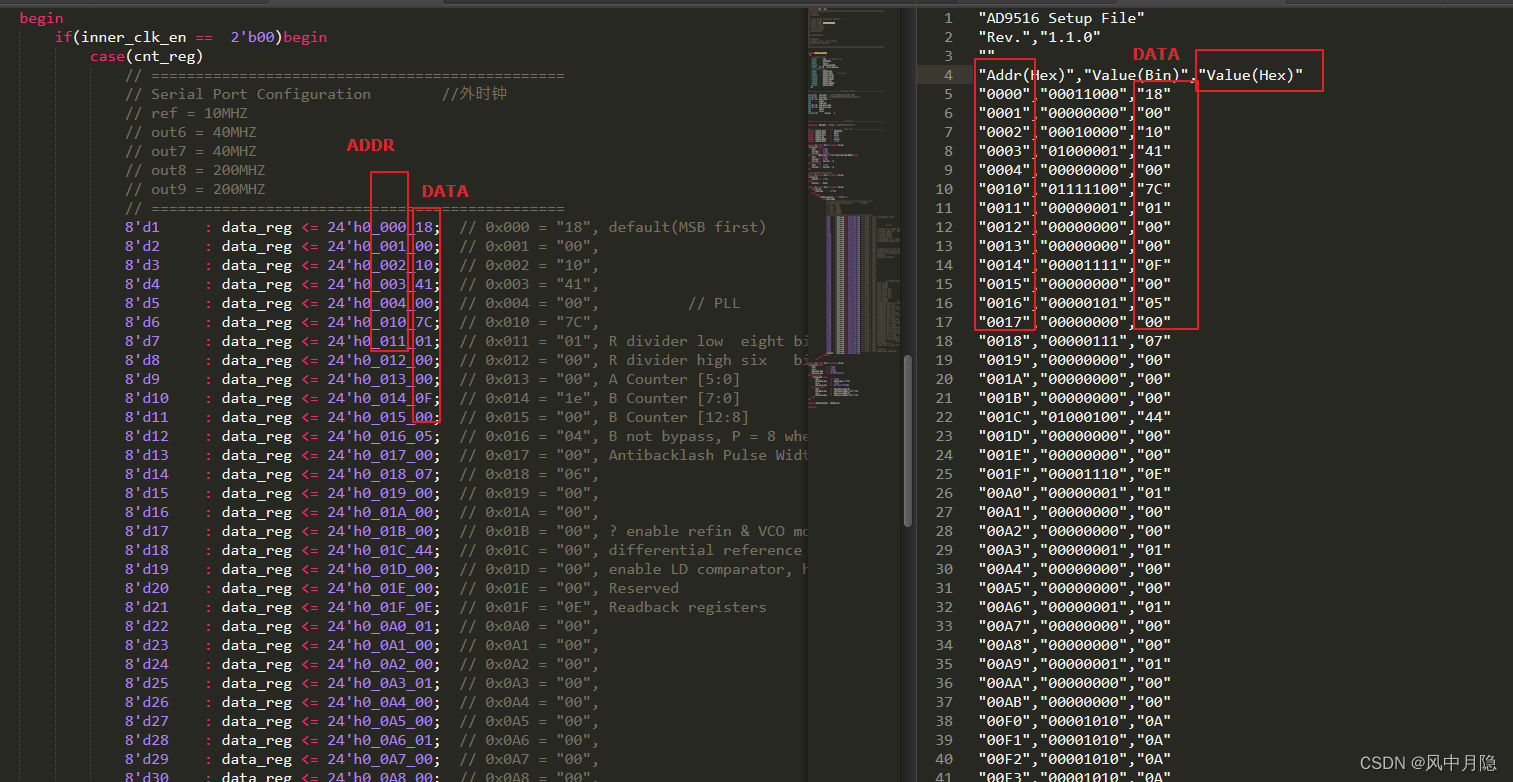

5) 将导出的值写到例程代码“ad9516_config”的对应位置:

6.3 例程平台:

1) 硬件平台:xc7z100ffg900-2

2) FPGA开发平台:vivado2018.3

7附录(代码以及寄存器)

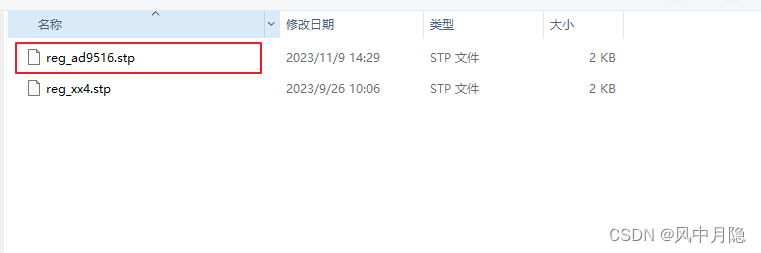

AD9516-cfg-demo(verilog hdl编写的FPGA驱动AD9516时钟芯片的案例代码

reg_ad9516.stp (配置寄存器)

AD9516/AD9517时钟芯片寄存器参数配置说明

[AD9516_17_18 Eval Software 软件下载链接]

(https://download.csdn.net/download/u014586651/77676803)

今天的文章时钟芯片操作错误096a80_常用时钟芯片分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/85098.html