掌握JESD204B(二)–AD6676的调试

配置部分

时钟芯片HMC7044配置

HMC7044芯片说明

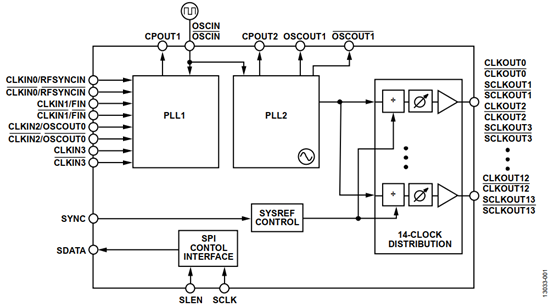

HMC7044芯片框图:

本项目中使用的芯片模式为外时钟(输入100MHz晶振),PLL1使能模式,VCO频率为2400MHz;时钟配置关系如下:

a) 输入至AD的时钟都配置为VCO的12分频200MHz;

b) 输入至AD的SYS_REF都配置为VCO的1024分频为2.34375MHz;

c) 输入至FPGA的时钟配置为100MHz;

d) 输入至FPGA的SYS_REF配置为2.34375MHz;

e) 输入至FPGA的GTX时钟配置为200MHz(用于GTX的参考时钟);

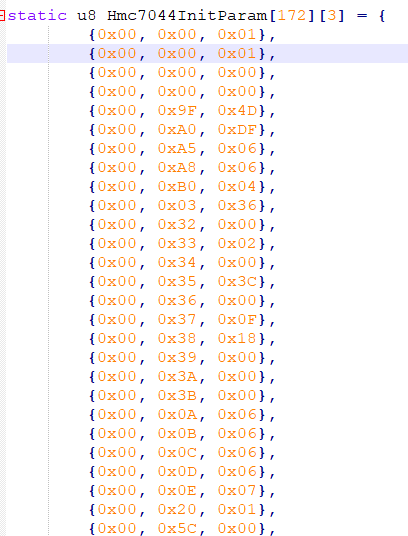

HMC7044寄存器部分配置:

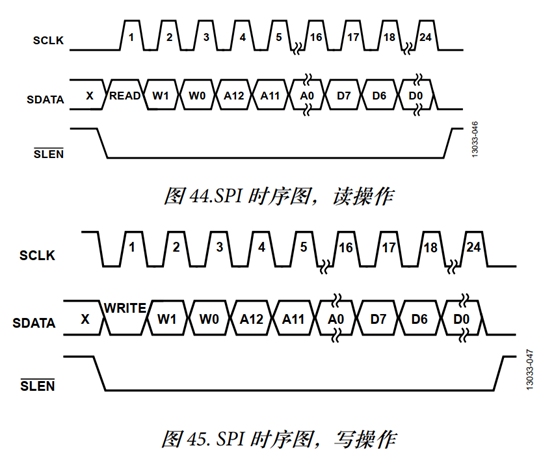

SPI配置时序:

AD芯片AD6676

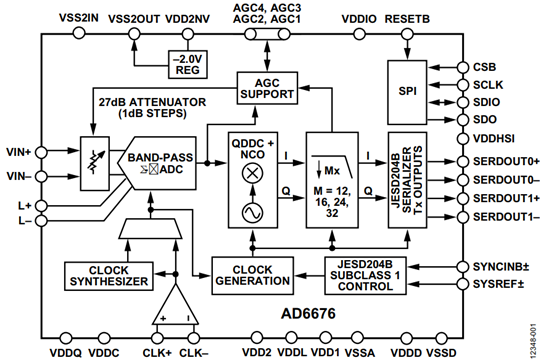

AD6676框图:

a) 信号带宽: 20 MHz至160 MHz;

b) 中频中心频率: 70 MHz至450 MHz;

c) 2.0 GSPS至3.2 GSPS ADC时钟速率;

d) 可选抽取系数: 12、 16、 24和32;

e) 片内衰减器范围为27 dB、步进为1 dB;

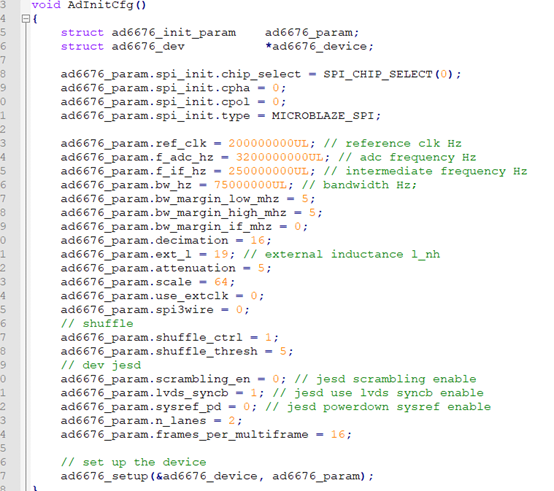

ADC配置:

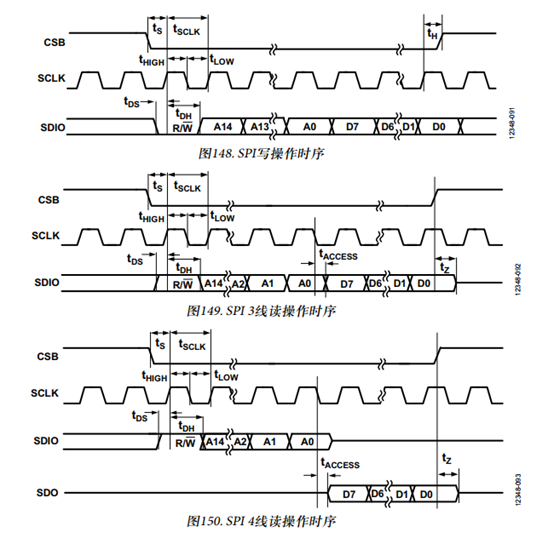

SPI配置时序:

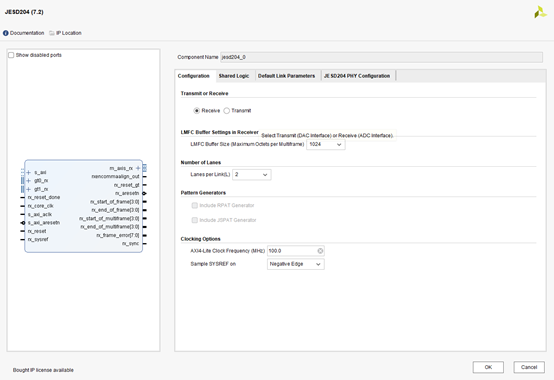

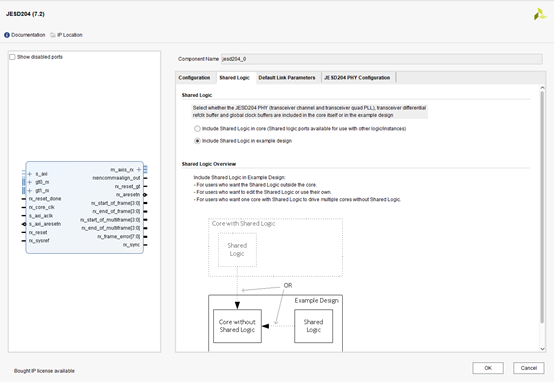

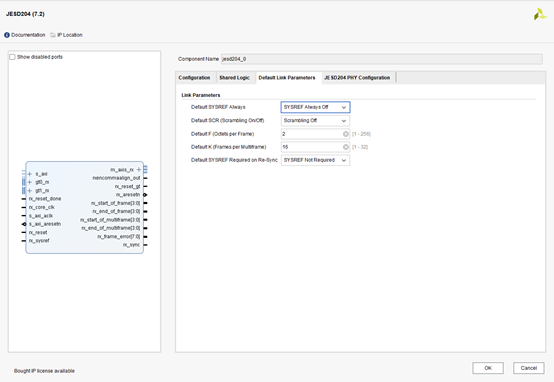

JESD204B接口配置

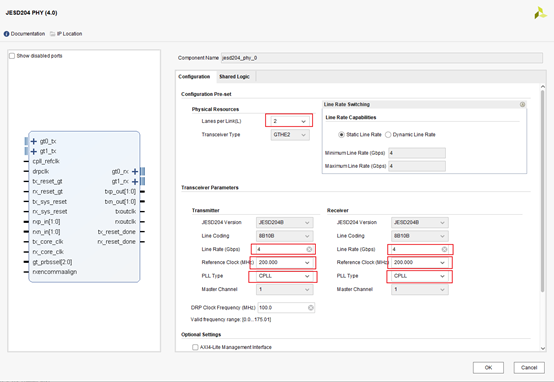

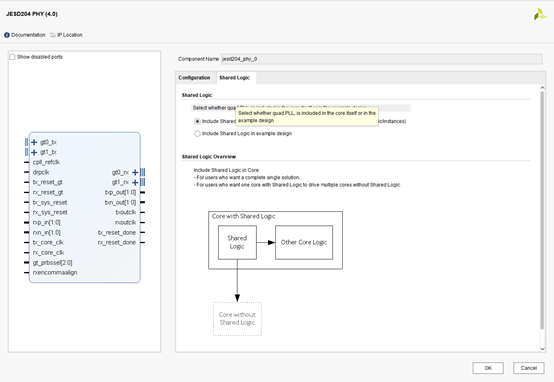

JESD PHY配置

线速率:4Gbps;

参考时钟:200MHz;

PLL TYPE:CPLL;

JESD配置

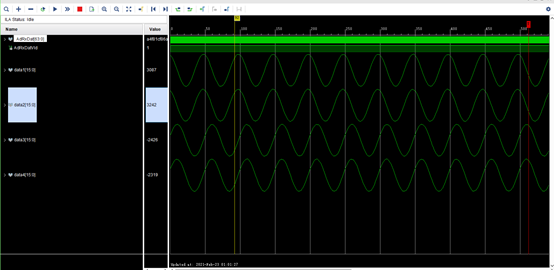

数据接收部分

配置完成以后等待链路的链接,链路的链接过程主要有以下几步:

JESD204B链路建立

AD6676 JESD204B Tx接口按照JEDEC标准204B(2011年7月规范)的规定,以Subclass 0或Subclass 1工作。链路建立过程

分为下列几个步骤:代码组同步、 ILAS和用户数据。

代码组同步(CGS)和SYNCINB

代码组同步(CGS)是JESD204B接收机找到数据流中10位符号间边界的过程。在CGS阶段, JESD204B发射(JESD Tx)模块传送/K28.5/字符。接收机必须使用时钟和数据恢复(CDR)技术,在输入数据流中定位/K28.5/字符。接收机通过置位AD6676 SYNCINB±引脚上的低电平信号,发出一个同步请求。然后, JESD Tx便开始发送/K/字符。接收机同步之后,便解除SYNCINB信号置位,使其变为高电平。 AD6676接着在下一个LMFC边界发送一个ILAS。SYNCINB±引脚操作选项可通过SPI寄存器加以控制。虽然SYNCINB输入默认配置为正引脚上的CMOS逻辑电平,但也可通过寄存器0x1E7配置为正/负引脚上的差分LVDS输入信号。 SYNCINB输入信号的极性也可通过寄存器0x1E4予以反转。

数据接收:

注意:

硬件框图参考上一篇“”掌握JESD204B(一)–AD6676的调试;

今天的文章ad9680 204b 调试问题_ad081v1接线图「建议收藏」分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/87274.html