实验内容:

1.adder(加法器)模块的编写。

2.建立完整的工程,工程中包括自己编写的 adder 模块,adder_display 模块(已

在群文件中提供),testbench.v(仿真文件)文件(已在群文件中提供),

lcd_module.dcp(显示屏操作模块)(已在群文件提供)。

※其中,adder_display.v 文件和 testbench.v 文件中的 adder 模块实例化已被挖

去,请自行填充。

3.完成仿真,并将仿真波形图像截图。

4.生成可以下载到 FPGA 上的.bit 文件。

5.完成整个工程的结构框图(包括 adder_display 模块和 adder 模块,不包括

testbench 部分和 lcd_module 部分)(选做 加分项)

实验过程:

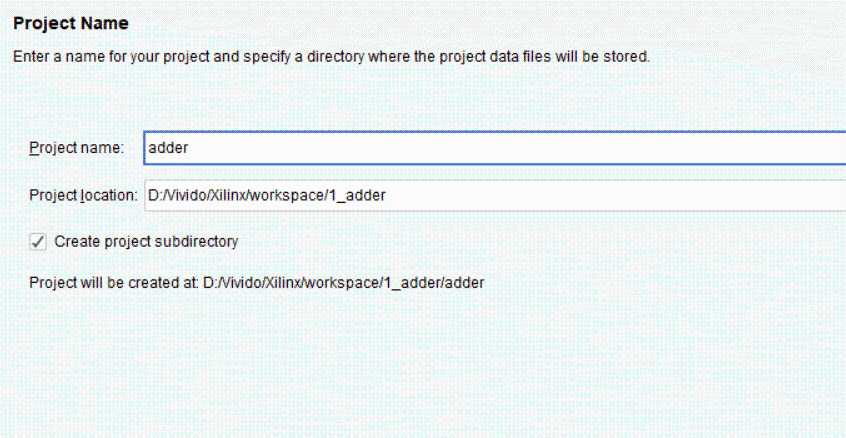

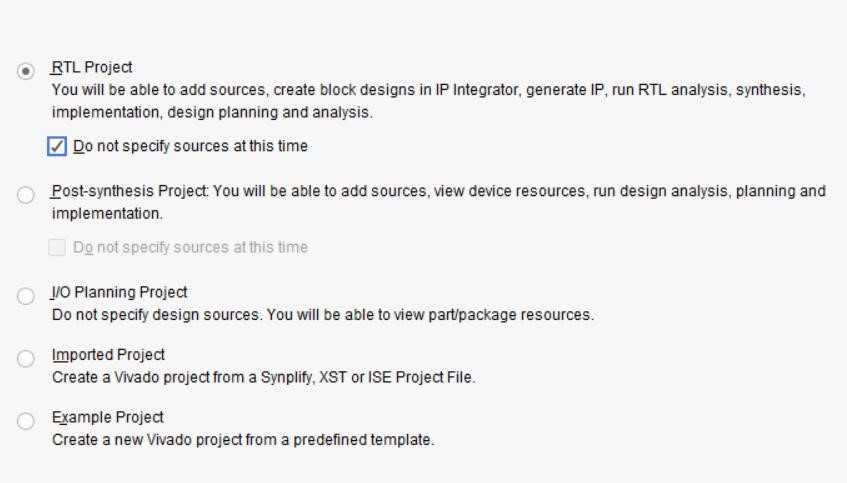

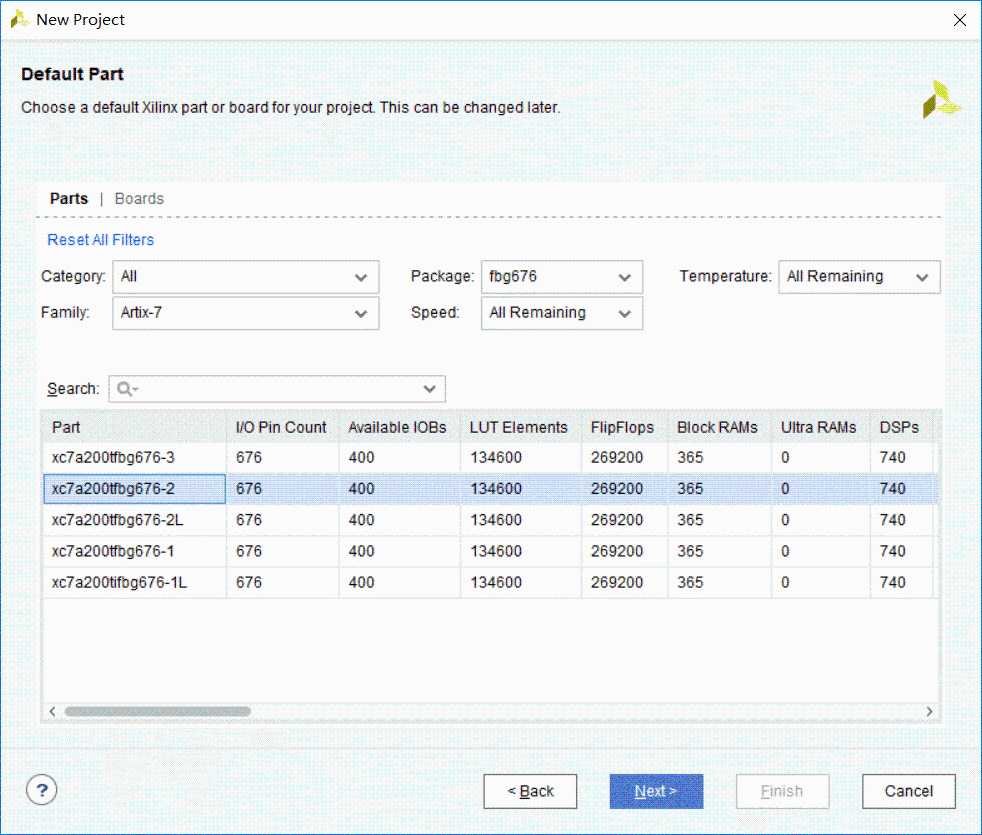

1)新建工程

本过程按照实验手册一路next,按实验手册进行选择:

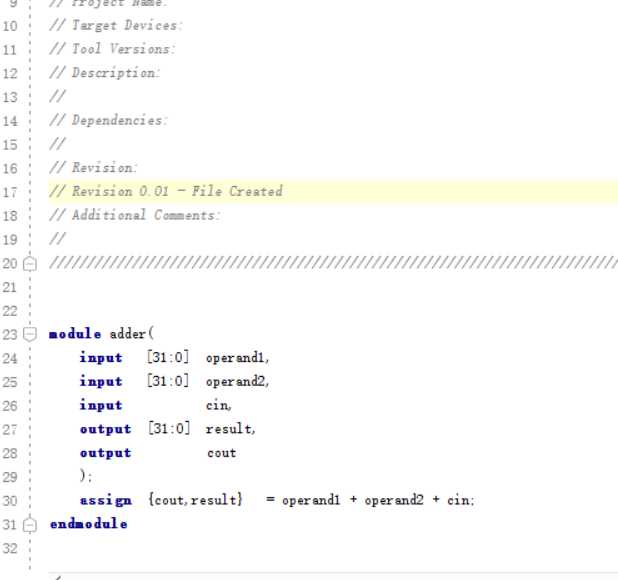

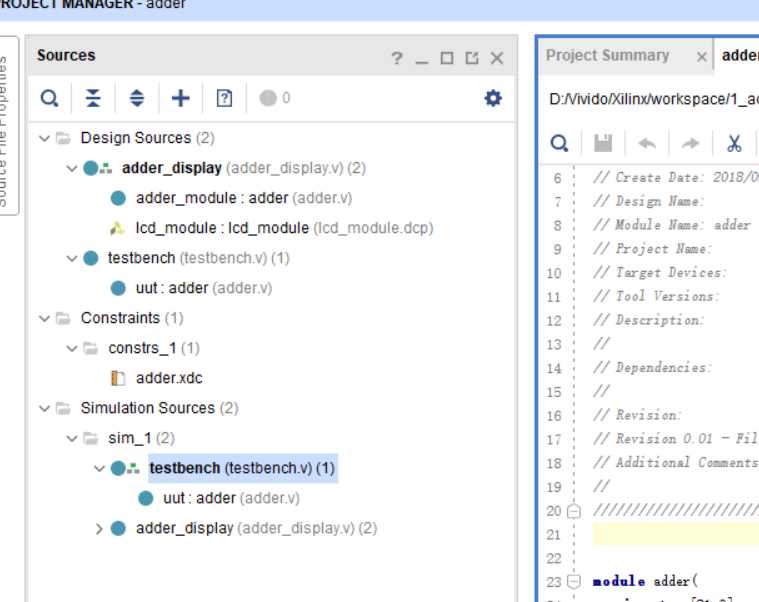

2)添加源文件

创建adder.v文件,编写代码;

有 2 个 32 位数的输入和 1 个进位输入,产生 1 个 32 位的加法 和结果和 1 个向高位的进位。本实验提供的参考设计是直接写“+”号实现加法功能 的,这样的写法综合工具会调用内部的模块库的加法器来实现;

源码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/05/02 22:42:20

// Design Name:

// Module Name: adder

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module adder(

input [31:0] operand1,

input [31:0] operand2,

input cin,

output [31:0] result,

output cout

);

assign {cout,result} = operand1 + operand2 + cin;

endmodule

3)添加展示外围模块

将实验辅助文件adder_display.v,lcd_module与testbentch.v添加到工程中;并对adder_display.v与testbentch.v的未添加模块添加,及对adder.v文件进行实例化。

adder_display.v添加部分:

源码:

//*************************************************************************

// > 文件名: adder_display.v

// > 描述 :加法器显示模块,调用FPGA板上的IO接口和触摸屏

// > 作者 : LOONGSON

// > 日期 : 2016-04-14

//*************************************************************************

module adder_display(

//时钟与复位信号

input clk,

input resetn, //后缀"n"代表低电平有效

//拨码开关,用于选择输入数和产生cin

input input_sel, //0:输入为加数1(add_operand1);1:输入为加数2(add_operand2)

input sw_cin,

//led灯,用于显示cout

output led_cout,

//触摸屏相关接口,不需要更改

output lcd_rst,

output lcd_cs,

output lcd_rs,

output lcd_wr,

output lcd_rd,

inout[15:0] lcd_data_io,

output lcd_bl_ctr,

inout ct_int,

inout ct_sda,

output ct_scl,

output ct_rstn

);

//-----{调用加法模块}begin

reg [31:0] adder_operand1;

reg [31:0] adder_operand2;

wire adder_cin;

wire [31:0] adder_result ;

wire adder_cout;

adder adder_module(

//需要补充的部分

.operand1(adder_operand1),

.operand2(adder_operand2),

.cin (adder_cin ),

.result (adder_result ),

.cout (adder_cout )

);

assign adder_cin = sw_cin;

assign led_cout = adder_cout;

//-----{调用加法模块}end

//---------------------{调用触摸屏模块}begin--------------------//

//-----{实例化触摸屏}begin

//此小节不需要更改

reg display_valid;

reg [39:0] display_name;

reg [31:0] display_value;

wire [5 :0] display_number;

wire input_valid;

wire [31:0] input_value;

lcd_module lcd_module(

.clk (clk ), //10Mhz

.resetn (resetn ),

//调用触摸屏的接口

.display_valid (display_valid ),

.display_name (display_name ),

.display_value (display_value ),

.display_number (display_number),

.input_valid (input_valid ),

.input_value (input_value ),

//lcd触摸屏相关接口,不需要更改

.lcd_rst (lcd_rst ),

.lcd_cs (lcd_cs ),

.lcd_rs (lcd_rs ),

.lcd_wr (lcd_wr ),

.lcd_rd (lcd_rd ),

.lcd_data_io (lcd_data_io ),

.lcd_bl_ctr (lcd_bl_ctr ),

.ct_int (ct_int ),

.ct_sda (ct_sda ),

.ct_scl (ct_scl ),

.ct_rstn (ct_rstn )

);

//-----{实例化触摸屏}end

//-----{从触摸屏获取输入}begin

//根据实际需要输入的数修改此小节,

//建议对每一个数的输入,编写单独一个always块

//当input_sel为0时,表示输入数为加数1,即operand1

always @(posedge clk)

begin

if (!resetn)

begin

adder_operand1 <= 32'd0;

end

else if (input_valid && !input_sel)

begin

adder_operand1 <= input_value;

end

end

//当input_sel为1时,表示输入数为加数2,即operand2

always @(posedge clk)

begin

if (!resetn)

begin

adder_operand2 <= 32'd0;

end

else if (input_valid && input_sel)

begin

adder_operand2 <= input_value;

end

end

//-----{从触摸屏获取输入}end

//-----{输出到触摸屏显示}begin

//根据需要显示的数修改此小节,

//触摸屏上共有44块显示区域,可显示44组32位数据

//44块显示区域从1开始编号,编号为1~44,

always @(posedge clk)

begin

case(display_number)

6'd1 :

begin

display_valid <= 1'b1;

display_name <= "ADD_1";

display_value <= adder_operand1;

end

6'd2 :

begin

display_valid <= 1'b1;

display_name <= "ADD_2";

display_value <= adder_operand2;

end

6'd3 :

begin

display_valid <= 1'b1;

display_name <= "RESUL";

display_value <= adder_result;

end

default :

begin

display_valid <= 1'b0;

display_name <= 40'd0;

display_value <= 32'd0;

end

endcase

end

//-----{输出到触摸屏显示}end

//----------------------{调用触摸屏模块}end---------------------//

endmodule

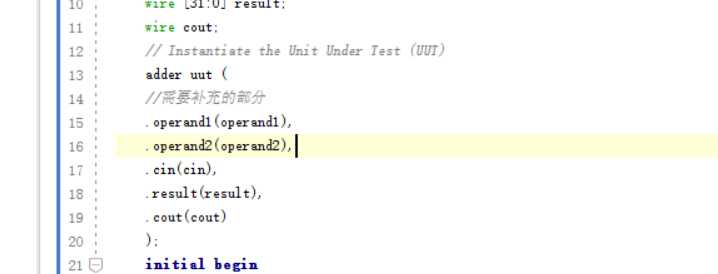

testbentch.v添加部分:

源码:

`timescale 1ns / 1ps //仿真单位时间为1ns,精度为1ps

module testbench;

// Inputs

reg [31:0] operand1;

reg [31:0] operand2;

reg cin;

// Outputs

wire [31:0] result;

wire cout;

// Instantiate the Unit Under Test (UUT)

adder uut (

//需要补充的部分

.operand1(operand1),

.operand2(operand2),

.cin(cin),

.result(result),

.cout(cout)

);

initial begin

// Initialize Inputs

operand1 = 0;

operand2 = 0;

cin = 0;

// Wait 100 ns for global reset to finish

#100;

// Add stimulus here

end

always #10 operand1 = $random; //$random为系统任务,产生一个随机的32位数

always #10 operand2 = $random; //#10 表示等待10个单位时间(10ns),即每过10ns,赋值一个随机的32位数

always #10 cin = {$random} % 2; //加了拼接符,{$random}产生一个非负数,除2取余得到0或1

endmodule

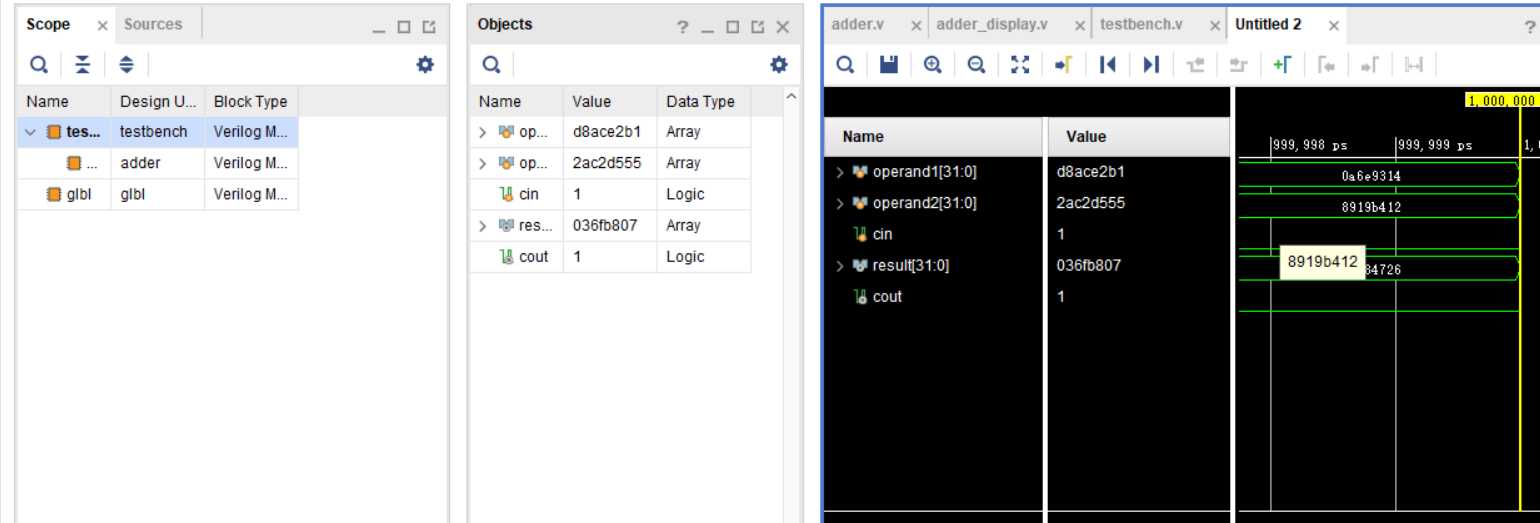

4)仿真图像

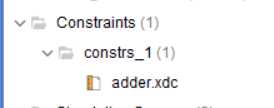

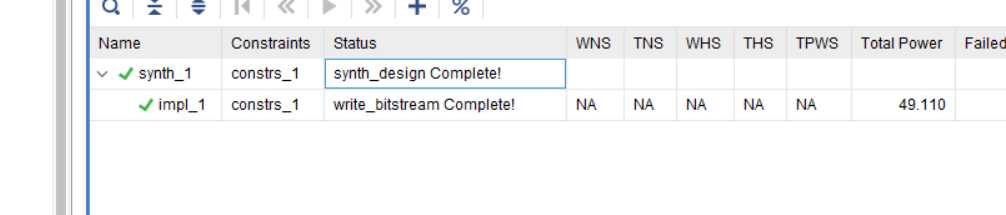

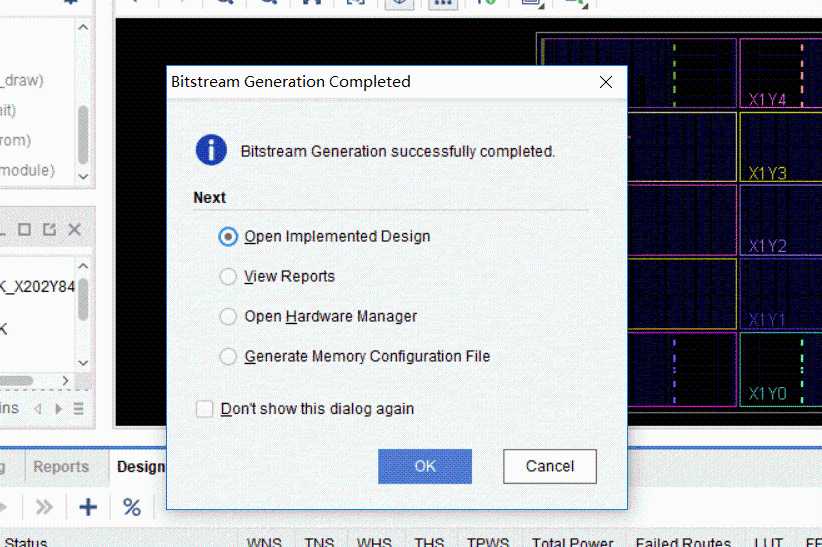

5)加入约束文件,烧成bit文件,上板验证

将adder.xdc文件添加到工程中;

生成可烧写的bit文件

点击“Generate Bitsteam”

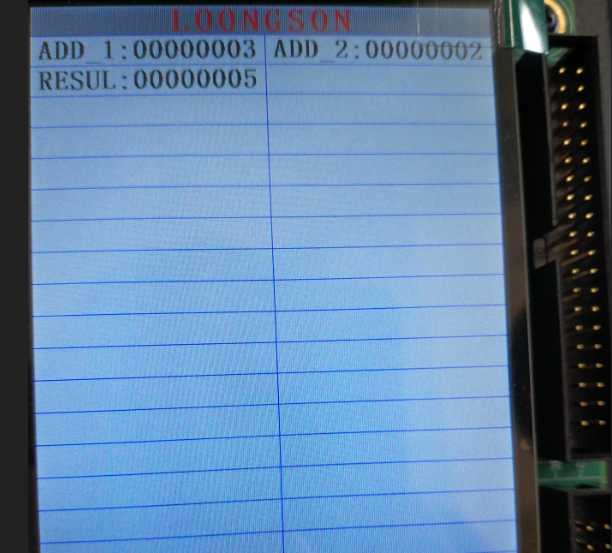

上板验证:烧写bit文件,在FPGA板上操作

今天的文章verilogbcd加法器_verilog用什么软件编写分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/88890.html