JESD204B

1、jesd204b概述

jesd204b是一种基于高速SERDES的ADC/DAC数据传输接口。详细介绍可以参考:

JESD204B详细介绍

初学的时候有好多问题没理清楚,现在记录一下:

0、 Subclass 0 uses device clock, lanes, and SYNC(子类0只有SYNC信号);

Subclass 1 uses device clock, lanes, SYNC~, and SYSREF(子类1有SYNC~和SYSREF信号);

Subclass 2 uses device clock, lanes, and SYNC(子类2只有SYNC信号)。

1、jesd204b分为几个子类,其中subclass 1 支持确定性时延,是最为常用的一个。

由于AD/DA一般有多个lane来传输数据,但是每条lane上的时延可能不一样,在subclass 1 模式下,在外部参考时钟sysref和sync的作用下,可以缓存快的一路,在确定所有路径同步后,再进行数据传输。

主要流程为以下几步:

a. RX拉低sync~,TX检测到sync~拉低后,在sysref上升沿开始CGS(代码组同步),RX接收到四个K28.5后,同步成功。RX将sync~拉高,并开始第一个LMFC计数

b.TX接收到sync~拉高后,在第二个LMFC边界开始ILAS(初始通道对齐)。确定rx所有通道都接收到valid data后,buffer the data until the next LMFC crossing

c.数据传输

2、jesd204b包括jesd204b core和jesd204b phy。在vivado 的jesd204 ip核中,如果选择了include share logic in core,则只需要输入tx_data,输出txp和txn;输出rx_data,输入rxp和rxn即可,中间的物理层不管。如果选择了include share logic in example ,则必须再添加一个jesd204b phy ip核。

3、jesd204b IP核接口较多,可以直接修改vivado自带的例程来适应自身项目。

4、jesd204b 的配置主要分为两个部分,一是AD/DA芯片的配置,一般通过SPI配置完成。二是jesd204b ip核接口的配置,包括L、M、F等,这个可以通过GUI直接配置,也可以通过s_axi修改物理层的寄存器值来设置,一般就用GUI设置。

2、时钟

参考博客:https://blog.csdn.net/qq_33675986/article/details/114443928

JESD时钟一般由外部的时钟芯片提供给ADC和FPGA1:

1、提供给ADC的时钟

提供给ADC的有两个时钟:采样时钟DCLK和参考时钟SYSREF。

采样时钟DCLK不管ADC的输出是不是JESD接口,都要用,是ADC的主时钟;参考时钟SYSREF是JESD接口特有的时钟,用于数据同步。

2、提供给FPGA的时钟

提供给FPGA的时钟有三个:GTBank的参考时钟、JESD的Device clock和JESD的参考时钟SYSREF。

a.GTBank的参考时钟是用于GTBank的数据恢复,JESD IP核的参考时钟;

b.JESD的Device clock是用于接收JESD链路数据的接收端设备时钟;

c.参考时钟SYSREF是JESD接口特有的时钟,用于数据同步。

这些时钟的关系,如下所示:

1.DCLK由ADC的采样率决定;

2.FPGA端Device clock由ADC输出JESD单lane的线速率lane_rate决定,Device clock=lane_rate/40

3.给FPGA和ADC的参考时钟SYSREF频率相同,要同源,频率由多帧时钟决定(见注释);

4.GTBank的参考时钟根据FPGA内IP核的设置决定,与其他几个时钟不相关。

注释:多帧时钟F_lmfc是JESD协议定义的时钟,不需要时钟芯片输出。多帧时钟F_lmfc的具体频率由ADC端的LMKFS等配置信息决定

3、JESD时钟计算实例

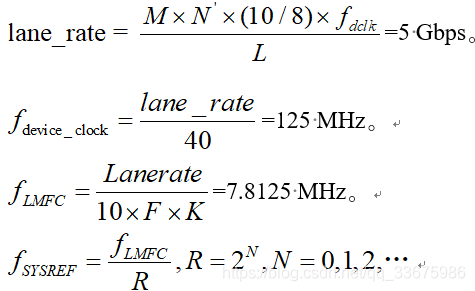

首先根据ADC的工作模式、采样率、LMKFS等信息计算JESD单lane的线速率lane_rate。

假设ADC的采样率为250MSps,JESD的关键参数配置为:M=2, L=2, F=2, S=1, K=32.

则各个时钟计算入下图所示:

按照上述时钟进行配置,然后将FPGA内部JESD IP核输出的SYNC信号接到ADC端,即可完成JESD的链接。

JESD204B定义

jesd204B是一种高速串行接口,最高串行数据速率可达12.5Gbps。

其标准是一种分层规范,主要包括以下几层:

1、应用层

2、传输层

在这层完成链路参数的配置,并根据配置完成数据的组包和解包。

主要参数为LMFS。

| L | 数据传输的通道(lane)数量 |

|---|---|

| M | 每个器件的转换数(理解为每个AD或者DA的转换通道数) |

| F | 每一帧的字节数(octets) |

| K | 多帧情况下的帧数 |

| S | 每一帧所传输的采样数 |

3、数据链路层

主要完成链路建立和数据编码。

链路建立分为三个阶段:

①代码组同步(CGS):

检测到多个连续的K28.5字符,跳入下一阶段

②初始通道对齐序列(ILAS):

对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。

通过传输几个多帧来对齐,对齐字符包括A、 R 、Q。

③用户数据

传输数据

4、物理层

在物理层中,数据进行串行化,8B/10B编码数据以线路速率发送和接收,实际为serdes结构。

8B/10B编码:保证直流平衡、方便错误检查、有利于提取时钟

扰码:降低电磁噪声、有利于提取时钟、避免出现连0/1

同步详解:

subclass1的三个阶段

1) 代码组同步(CGS):

-

RX将SYNC~引脚拉低,发出一个同步请求。

-

TX从下一个符号开始,发送未加扰的/K28.5/符号(每个符号10位)。

-

当R X接收到至少4个无错误的连续/K28.5/符号时,R X同步,然后将SYNC~引脚拉高。

-

R X必须接收到至少4个无错误8B/10B字符,否则同步将失败,链路留在CGS阶段。

-

C G S阶段结束,I L A S阶段开始。

注意:

-

串行数据传输没有接口时钟,因此RX必须将其数位及字边界与 TX 串行输出对齐。RX 向 TX 发送 ~SYNC 请求信号,让其通过所有信道发送一个已知的重复比特序列K28.5。RX 将移动每个信道上的比特数据,直到找到 4 个连续的 K28.5 字符为止。此时,它不仅将知道比特及字边界,而且已经实现了 CGS。

-

RXSYNC的输出必须与RX的帧时钟同步,同时要求TX的帧时钟与SYNC同步(可通过~SYNC复位TX的帧时钟计数器来实现)。

-

不能使用交流耦合。(with the exception that SYNC~ should never be ACcoupled)。

2) 初始通道同步(ILAS):

1.在JESD204B中,发送模块捕捉到SYNC~信号的变换,在下一个本地多帧(LMFC)边界上启动ILAS。

2.ILAS主要对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。

3.ILAS由4个多帧组成。每个多帧最后一个字符是多帧对齐字符/A,第一,三,四个多帧以/R字符开始,以/A字符结束。接收器以各通道的最后一个字符/A对齐接收器内各通道内各多帧的末尾。

4.这些特定的控制字符只用于初始通路对齐序列中,而不用在数据传输的任何其他阶段。CGS和ILAS阶段不加扰。

5.RX模块中的FIFO吸收信道偏移。

3) 数据传输阶段:没有控制字符,获取链路全带宽。利用字符替换来监视数据同步,多帧计数器LMFC。

今天的文章JESD204B接口和Xilinx IP核学习笔记分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/81743.html