模块的结构

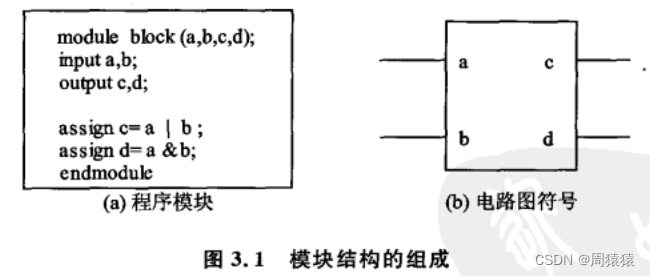

Verilog的基本设计单元是“模块”(block)。 一个模块是由两部分组成的,一部分描述接口,另一部分描述逻辑功能,即定义输入是如何影响输出的。图所示是模块结构组成图。下面举例说明。

图中的程序模块(见图3.1(a))旁边有一个电路图的符号(见图3.1(b))。在许多方面,程序模块和电路图符号是一致的,这是因为电路图符号的引脚也就是程序模块的接口。而程序模块描述了电路图所能实现的逻辑功能。上面的Verilog设计中,模块中的第二、第三行说明接口的信号流向,第四、第五行说明了模块的逻辑功能。以上就是设计一个简单的Verilog程序模块所需的全部内容。

从这一例子可以看出,Verilog结构位于在module和endmodule声明语句之间 , 每个 Verilog程序包括4个主要部分:端口定义、I/0说明、内部信号声明和功能定义。

模块的端口定义

模块的端口声明了模块的输入输出口 。 其格式如下:

module 模块名(口1,口2,口3,口4, ………);

模块的端口表示的是模块的输入和输出口名,也就是说,它与别的模块联系端口的标识。在模块被引用时,在引用的模块中 ,有些信号要输入到被引用的模块中 ,有的信号需要从被引用的模块中取出来。 在引用模块时其端口可以用两种方法连接:

(1) 在引用时,严格按照模块定义的端口顺序来连接 ,不用标明原模块定义时规定的端口名,例如:

模块名(连接端口 1 信号名, 连接端口 2信号名,连接端口 3信号名,……);

(2)在引用时用 “.” 符号 ,标明原模块是定义时规定的端口名, 例如:

模块名(.端口 1名(连接信号 1名),端口 2名(连接信号 2名),……);

这样表示的好处在于可以用端口名与被引用模块的端口相对应, 而不必严格按端口顺序 对应 , 提高了程序的可读性和可移植性。

例如:

…

MyDesignMK M1(.sin(SerialIn),.pout(ParallelOut),…);

…

其中 , .sin和. pout都是M1的端口名, 而M1则是与MyDesignMK完全一样的模块。 MyDesignMK已经在另一个模块中定义过, 它有两个端口,即sin和pout。 与sin口连接的信号名为Serialln , 与pout端口连接的是信号名为ParallelOut。

模块内容

模块的内容包括l/0说明 、内部信号声明和功能定义。

I/O说明的格式

输入口 :

input[信号位宽- 1:0] 端口名1;

input[信号位宽- 1:0] 端口名2;

...

input[信号位宽一]:0]、端口名i;

输出口 :

output[信号位宽- 1:0] 端口名1;

output[信号位宽- 1:0] 端口名2;

...

output[信号位宽一]:0]、端口名i;

输入/输出口 :

inout[信号位宽- 1:0] 端口名1;

inout[信号位宽- 1:0] 端口名2;

...

inout[信号位宽一]:0]、端口名i;

I/O说明也可以写在端口声明语句里。 其格式如下:

module module_name(input portl, input port2, ···output port1, output port2…) ;

内部信号说明

在模块内用到的和与端口有关的wire和reg类型变矗的声明。

如:

reg [width-1: 0] R变量 1, R 变童 2···;

wire [ width-1 : O] W变蜇 1, W 变量 2···;

....

功能定义

模块中最重要的部分是逻辑功能定义部分。 有3种方法可在模块中产生逻辑。

(1) 用“assign”声明语句 如:assign a = b &. c;

这种方法的句法很简单,只需写一个“assign”,后面再加一个方程式即可。 例中的方程式描述了一个有两个输入的与门。

(2) 用实例元件 如:and # 2 u1(q, a, b) ;

采用实例元件的方法像在电路图输入方式下调入库元件一样,键入元件的名字和相连的引脚即可。 这表示在设计中用到一个跟与门(and)一样的名为u1的与门 ,其输入端为a 、b, 输出为q。 输出延迟为2个单位时间 。 要求每个实例元件的名字必须是唯一的, 以避免与其他调用与门(and)的实例混淆。

(3) 用“always”块 如:

always @(posedge clk or posedge clr);

begin

if(clr) q<= 0;

else if(en) q <= d;

end

采用“assign” 语句是描述组合逻辑最常用的方法之一。 而 “always” 块既可用于描述组合逻辑,也可描述时序逻辑。 用“always “块的例子生成了一个带有异步清除端的D触发器。 “always ”块可用很多种描述手段来表达逻辑, 例如上例就用了if…else语句来表达逻辑关系 。 如按一定的风格来编写“always“块,可以通过综合工具把源代码自动综合成用门级结构表示 的组合或时序逻辑电路。

理解要点

如果用Verilog模块实现一定的功能,首先应该清楚哪些是同时发生的,哪些是顺序发生的。上面3个例子分别采用了“assign” 语句、实例元件和“always”块。这3个例子描述的逻辑功能是同时执行的。 也就是说,如果把这3项写到一个 Verilog 模块文件中去 ,它们的顺序不会影响实现的功能。 这3项是同时执行的,也就是并发的。

然而,在 “always “模块内, 逻辑是按照指定的顺序执行的。 “always “块中的语句称为“顺序语句“, 因为它们是顺序执行的。 所以, “always “块也称为“过程块"。 请注意,两个或更多的 “always “模块都是同时执行的,而模块内部的语句是顺序执行的。 看一下“always “内的语句,就会明白它是如何实现功能的。 if…else···if必须顺序执行,否则其功能就没有任何意义。 如 果else语句在 if语句之前执行,其功能就会不符合要求。 为了能实现上述描述的功能 ,“always “模块内部的语句将按照书写的顺序执行。

要点总结

(1) 在Verilog模块中所有过程块(如:initial块、always块) 、连续赋值语句、实例引用都是并行的;

(2) 它们表示的是一种通过变量名互相连接的关系 ;

(3) 在同一模块中这三者出现的先后次序没有关系;

(4) 只有连续赋值语句assign和实例引用语句可以独立于过程块而存在于模块的功能定义部分。

今天的文章数字系统有哪些_verilog模块例化「建议收藏」分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/82266.html