锁相环 PLL ( Phase Locked Loop)

PLL 的英文全称是 Phase Locked Loop,即锁相环,是一种反馈控制电路。锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

同步时钟

当两个时钟间的相位是固定关系的,则可以称这两个时钟为同步时钟(synchronous clock)。 注意,这个表述很重要。

那么这里就又有一种情况,经过一个 PLL 产生相位不同,但相位固定的两个时钟,他们依旧是同步时钟。

而如果是两个晶振产生的时钟,因为两个晶振在上电时相位差是随机的,而且不同晶振时钟漂移抖动也不一样,所以相位是不固定的。当无法判断两个时钟间的相位时,则可以称这两个时钟为异步时钟(asynchronous clocks)。

同步电路/异步电路

同步电路

电路中所有受时钟控制的单元全部由一个统一的全局时钟进行控制。

同步电路特点

a) 电路核心逻辑是用各种触发器实现;

b) 电路主要信号、输出信号等都是在某个时钟沿驱动触发器产生的;

c) 同步时序电路可以很好的避免毛刺;

d) 利于器件移植;

e) 利于静态时序分析(STA)、验证设计时序性能。

异步电路

异步电路设计最大的不同是电路中的数据传输可以在任何时候发生,电路中没有一个全局的或者局部的控制时钟

异步电路特点

a) 电路核心逻辑用组合电路实现;

b) 异步时序电路的最大缺点是容易产生毛刺;

c) 不利于器件移植;

d) 不利于静态时序分析(STA)、验证设计时序性能。

什么叫 FPGA

FPGA 是一种可以重构电路的芯片,是一种硬件可重构的体系结构。它的英文全称是 Field Programmable Gate Array,中文名是现场可编程门阵列。

通过编程,用户可以随时改变它的应用场景,它可以模拟 CPU、GPU 等硬件的各种并行运算。通过与目标硬件的高速接口互联,FPGA 可以完成目标硬件运行效率比较低的部分,从而在系统层面实现加速。

IC

什么叫数字 IC

IC 就是半导体元件产品的统称,IC 按功能可分为:数字 IC、模拟 IC、微波 IC 及其他 IC。数字 IC 就是传递、加工、处理数字信号的 IC,是近年来应用最广、发展最快的 IC 品种,可分为通用数字 IC 和专用数字 IC。

通用 IC:是指那些用户多、使用领域广泛、标准型的电路,如存储器(DRAM)、微处理器(MPU)及微控制器(MCU)等,反映了数字 IC 的现状和水平。

专用 IC(ASIC):是指为特定的用户、某种专门或特别的用途而设计的电路。

对数字 IC 设计的理解

Verilog HDL 和 VHDL 是世界上最流行的两种硬件描述语言,都是在 20 世纪 80 年代中期开发出来的。前者由 Gateway Design Automation 公司(该公司于 1989 年被 Cadence 公司收购)开发。两种 HDL 均为 IEEE 标准。

是的,20 世纪 80 年代,这个语言距今已经 40 年,期间的修修改改并没有出现翻天覆地的大改动,也没有被时间和市场抛弃。原因很简单,在现有工艺没有突破性创新并推广之前,对以晶体管为基础的数字电路设计描述方法并不会变。 其次,数字电路就是一个由严密的逻辑组成的巨大建筑,经验的累积非常重要。小到一个加法器能不能加,加上去会不会又 timing 问题,performance bug 如何去修正,各种逻辑描述的优劣,对各种 EDA 的掌握和熟悉,如何才能写出物理实现最平衡的电路…更别说大到各种各样的算法建模前的研讨,复杂算法的 RTL 实现,对新的系统的预研,如此种种不一而足。恐怕不是上上培训班然后教你个 XXX 天学会 XXX 就能教给你的,不在完全匹配的岗位上磨练十年,或许连我列出的这些都学不完。最重要的是,没人敢把较高风险的系统交给有”青春”但是没有经验的人去做,一次流片,特别是高端工艺失败的代价可以顷刻让小公司破产,是的,驱动这个社会的是资本,资本是逐利的,但是资本也是最聪明的,他清楚应该选谁。十年之后,你大约 35 岁的日子,别人的“中年危机”正是你在 IC 这个领域成熟的时间段,可以说是风华正茂。可以在技术上继续前进,或者以经验来带领团队,可以抽身出来完成创业。 客观的说,ICer 并不是严格意义上的程序员,我们是数字电路的设计者和维护者,我们的每一行语言都会转换成物理意义上真实存在的与或非门,被光刻机印刻在芯片的最深处,成为所有现代工业物品中最核心的“大脑”,为它们赋予智慧。

关键路径

什么是关键路径?

关键路径通常是指同步逻辑电路中,组合逻辑时延最大的路径(这里我认为还需要加上布线的延迟),也就是说关键路径是对设计性能起决定性影响的时序路径。

如何优化关键路径?

对关键路径进行时序优化,可以直接提高设计性能。对同步逻辑来说,常用的时序优化方法包括 Pipeline、Retiming、逻辑复制、加法/乘法树、关键信号后移、消除优先级等解决。

静态时序分析能够找出逻辑电路的关键路径。通过查看静态时序分析报告,可以确定关键路径。

- 组合逻辑中插入寄存器(插入流水线)

组合逻辑的延时过长,就会成为关键路径,这时可以考虑在该路径上插入额外的寄存器,这种方法也称为插入流水线,多用于高度流水的设计中,因为这种设计中额外插入寄存器增加的时钟周期延时并不会违反整个设计的规范要求,从而不会影响设计的总体功能性实现,也即额外插入的寄存器在保持吞吐量不变的情况下改善了设计的时序性能。当然,其不可避免地会带来部分面积的增加。 - 寄存器平衡(重定时 Retiming)

在不增加寄存器个数的前提下,通过改变寄存器的位置来优化关键路径,可以对比和流水线插入寄存器的不同。 - 操作符平衡(加法树、乘法树)

平衡前,a 和 b 均经过 3 个乘法器带来的延时,c 经历 2 个,d 经历 1 个,最长延时为 3 个乘法器延时。平衡后,树形结构,a、b、c、d 均经历 2 个乘法器延时,最长延时为 2 个乘

法器延时。 - 消除代码优先级(case 代替 if…else)

本身确实不需要优先级的地方,可以使用 case 代替 if…else,使得顺序执行的语句编程并行执行。如果确实有优先级兵,则不能这样做。这种消除代码中的优先级的策略也称为代码结构平坦化技术,主要针对那些带优先级的编码结构。 - 逻辑复制

当某个信号的扇出 fanout 比较大时,会造成该信号到各个目的逻辑节点的路径变得过长,从而成为设计中的关键路径,此时可以通过对该信号进行复制来降低扇出。高扇出的危害是大大增加了布局布线的难度,这样其扇出的节点也就无法被布局得彼此靠近,所以就导致了布线长度过大的问题。 - 关键信号后移

关键输入应该在逻辑最后一级提供,其中关键输入为芯片、Slice、或者 LUT 提供的时延最大的输入,比如在 if…else if…链中,将关键信号放在第一级。

补充知识(扇入、扇出)

The number of circuits that can be fed input signals from an output device.

扇出:可以从输出设备 输入信号的电路数量 。

扇出(fan-out)是定义单个逻辑门能够驱动的数字信号输入最大量的术语。大多数TTL逻辑门能够为10个其他数字门或驱动器提供信号。因而,一个典型的TTL逻辑门有10个扇出信号。

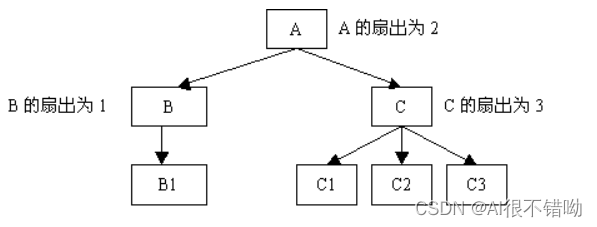

如图所示:

一个模块的扇出数过大或过小都不理想,过大比过小更严重。一般认为扇出的上限不超过7。扇出过大意味着管理模块过于复杂,需要控制和协调过多的下级。解决的办法是适当增加中间层次。

一个模块的扇入是指有多少个上级模块调用它。扇人越大,表示该模块被更多的上级模块共享。这当然是我们所希望的。但是不能为了获得高扇人而不惜代价,例如把彼此无关的功能凑在一起构成一个模块,虽然扇人数高了,但这样的模块内聚程度必然低。这是我们应避免的。

设计得好的系统,上层模块有较高的扇出,下层模块有较高的扇人。其结构图像清真寺的塔,上面尖,中间宽,下面小。

FPGA 开发工具

目前 FPGA 的生产厂家主要有 ALTERA,Xilinx,Actel,Lattice。

Altera 公司生产的 FPGA 和 CPLD,开发工具主要用 Quartus;

Xilinx 公司的 FPGA 主要用 ISE,vivado 作为开发工具;

EDA 开发工具

数字逻辑仿真工具

cadence: Incisive

synopsys: VCS

mentor: QuestaSim

ModelSim

数字逻辑综合工具

Cadence:Genus

Synopsis: design

Compiler (DC)

数字后端设计工具

1,自动布局布线工具

Cadence: Innovus

Synopsis: IC Compiler

2. 物理验证工具

1, Mentor: Calibre

2, Synopsis: ICV

3, Cadence: PVS/Pegasus

参考文献

理解扇入扇出

今天的文章基础知识~ 锁相环 PLL、同步时钟 、同步电路/异步电路、FPGA、IC、关键路径分享到此就结束了,感谢您的阅读。

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请发送邮件至 举报,一经查实,本站将立刻删除。

如需转载请保留出处:https://bianchenghao.cn/83348.html